# SN32F100 Series

**USER'S MANUAL**

SN32F107 SN32F108 SN32F109

**SONIX 32-Bit Cortex-M0 Micro-Controller**

SONIX reserves the right to make change without further notice to any products herein to improve reliability, function or design. SONIX does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. SONIX products are not designed, intended, or authorized for us as components in systems intended, for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SONIX product could create a situation where personal injury or death may occur. Should Buyer purchase or use SONIX products for any such unintended or unauthorized application. Buyer shall indemnify and hold SONIX and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that SONIX was negligent regarding the design or manufacture of the part.

### AMENDENT HISTORY

| Version | Date       | Description                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 1.0     | 2013/03/18 | First version released.                                                                                                                                                                |  |  |  |  |  |  |  |  |

| 1.1     | 2013/03/29 | Update Codec Spec.                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|         |            | Update DAC Setting 3 Register.                                                                                                                                                         |  |  |  |  |  |  |  |  |

|         |            | 3. Update Sigma-delta DAC Power-Up Sequence.                                                                                                                                           |  |  |  |  |  |  |  |  |

| 1.2     | 2013/04/02 | Update Codec Spec.                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|         |            | Update ADC Setting 23 Register.                                                                                                                                                        |  |  |  |  |  |  |  |  |

|         |            | <ol><li>Update DAC Setting 1 Register and DAC Setting 2 Register.</li></ol>                                                                                                            |  |  |  |  |  |  |  |  |

| 1.3     | 2013/06/04 | 1. Add SN32F100 Start Kit V1.1 description.                                                                                                                                            |  |  |  |  |  |  |  |  |

|         |            | Add Comparator Output Debounce Time.                                                                                                                                                   |  |  |  |  |  |  |  |  |

|         |            | 3. Update supply current.                                                                                                                                                              |  |  |  |  |  |  |  |  |

|         |            | 4. Add Operation Mode Comparison Table.                                                                                                                                                |  |  |  |  |  |  |  |  |

|         |            | 5. Update System Block Diagram.                                                                                                                                                        |  |  |  |  |  |  |  |  |

|         |            | 6. Update System Tick Timer description.                                                                                                                                               |  |  |  |  |  |  |  |  |

|         |            | 7. Update LQFP 64 Pin Package Information.                                                                                                                                             |  |  |  |  |  |  |  |  |

|         |            | 8. Update Comparator description.                                                                                                                                                      |  |  |  |  |  |  |  |  |

|         |            | 9. Modify ADC's SEL_MIC definition.                                                                                                                                                    |  |  |  |  |  |  |  |  |

| 1.4     | 2013/07/16 | Update I2S's Status register default value.                                                                                                                                            |  |  |  |  |  |  |  |  |

|         |            | Update ADC's SEL_MIC register default value.                                                                                                                                           |  |  |  |  |  |  |  |  |

|         |            | 3. Update Code Security diagram.                                                                                                                                                       |  |  |  |  |  |  |  |  |

|         |            | 4. Update Code Option Table.                                                                                                                                                           |  |  |  |  |  |  |  |  |

|         |            | 5. Update High-level and Low-level input voltage Spec.                                                                                                                                 |  |  |  |  |  |  |  |  |

|         |            | 6. Update P0.14/DPDWAKEUP pin description.                                                                                                                                             |  |  |  |  |  |  |  |  |

| 1.5     | 2014/02/27 | Update Electrical characteristics.                                                                                                                                                     |  |  |  |  |  |  |  |  |

|         |            | Update Code Security table in <u>Code Security</u> section.                                                                                                                            |  |  |  |  |  |  |  |  |

|         |            | 3. Add Note for I/O open-drain function.                                                                                                                                               |  |  |  |  |  |  |  |  |

|         |            | <ol> <li>Add descriptions of I2C events which trigger I2C interrupt for <u>I2Cn_STAT</u> register.</li> <li>Update SN-LINK description in Chap 17. <u>Development Tool</u>.</li> </ol> |  |  |  |  |  |  |  |  |

|         |            | Update SN-LINK description in Chap 17. Development Tool.                                                                                                                               |  |  |  |  |  |  |  |  |

|         |            | <ul><li>6. Add Notice for BOOT pin in <u>Chap 16. SWD</u>.</li><li>7. Add WAKEUP sections.</li></ul>                                                                                   |  |  |  |  |  |  |  |  |

|         |            | <ul><li>7. Add <u>WAKEUP</u> sections.</li><li>8. Fix typing error.</li></ul>                                                                                                          |  |  |  |  |  |  |  |  |

| 1.6     | 2014/06/04 | Update SN-LINK-V2 photos.                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 1.0     | 2014/00/04 | 2. Fix typing errors.                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| 1.7     | 2015/05/29 |                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| 1.8     |            | Fix typing errors.                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| 1.0     | 2010/01/22 | Add Notice: HCLK MUST be equal or less than 24MHz during Flash program and erase                                                                                                       |  |  |  |  |  |  |  |  |

|         |            | operations.                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|         |            | Add SSPn Data Fetch (SSPn_DF) register.                                                                                                                                                |  |  |  |  |  |  |  |  |

|         |            | Update LQFP48 package information.                                                                                                                                                     |  |  |  |  |  |  |  |  |

| 1.9     | 2018/02/02 | Fix typing errors.                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|         | ,,         | 2. Remove SYSTICKPRE[1:0]                                                                                                                                                              |  |  |  |  |  |  |  |  |

|         |            | 3. Remove SYS0_ANTIEFT register.                                                                                                                                                       |  |  |  |  |  |  |  |  |

|         |            | 4. Update WDTPRE[2:0] bits description in SYS1 APBCP1 register.                                                                                                                        |  |  |  |  |  |  |  |  |

|         |            | 5. Update TO[15:0] bits description in I2Cn_TOCTRL register.                                                                                                                           |  |  |  |  |  |  |  |  |

|         |            | 6. Add Note for setting the pins which are not pin-out.                                                                                                                                |  |  |  |  |  |  |  |  |

|         |            |                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

# **Table of Content**

|   | AMENDENT HISTORY                                          |               |

|---|-----------------------------------------------------------|---------------|

| 1 | 1 PRODUCT OVERVIEW                                        |               |

|   | 1.1 FEATURES                                              | 13            |

|   | 1.2 SYSTEM BLOCK DIAGRAM                                  | 15            |

|   | 1.3 CLOCK GENERATION BLOCK DIAGRAM                        | 16            |

|   | 1.4 PIN ASSIGNMENT                                        | 17            |

|   | 1.5 PIN DESCRIPTIONS                                      |               |

|   | 1.6 PIN CIRCUIT DIAGRAMS                                  |               |

| 2 | 2 CENTRAL PROCESSOR UNIT (CPU)                            |               |

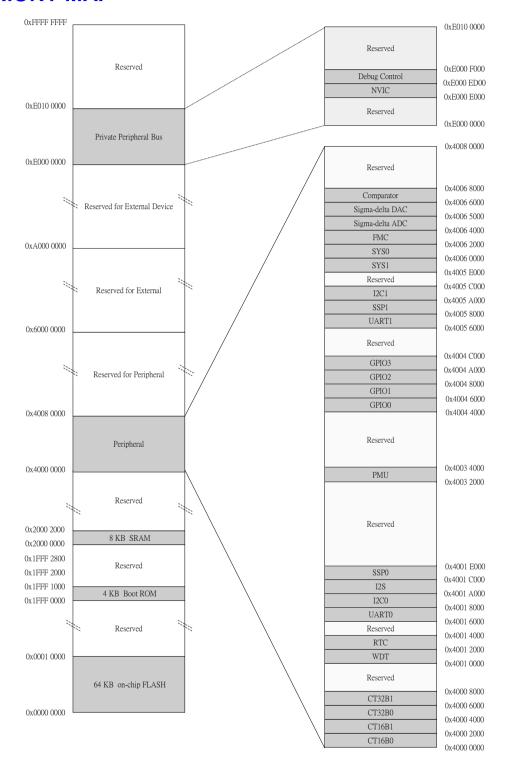

|   | 2.1 MEMORY MAP                                            | 27            |

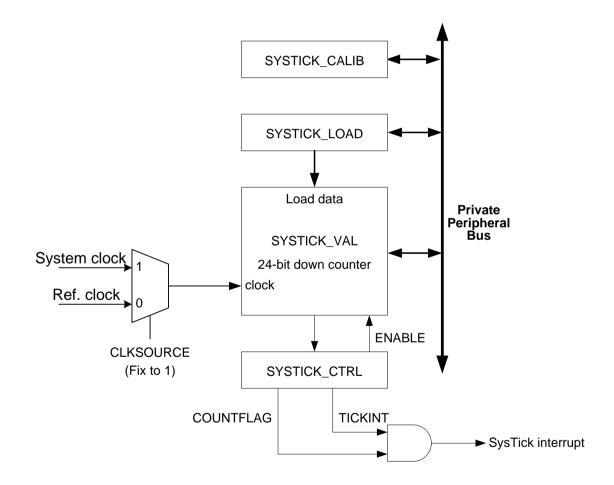

|   | 2.2 SYSTEM TICK TIMER                                     |               |

|   | 2.2.1 <i>OPERATION</i>                                    |               |

|   | 2.2.2 SYSTICK USAGE HINTS AND TIPS                        | 29            |

|   | 2.2.3 SYSTICK REGISTERS                                   |               |

|   | 2.2.3.1 System Tick Timer Control and Status register (SY | STICK_CTRL)29 |

|   | 2.2.3.2 System Tick Timer Reload value register (SYSTIC   | K_LOAD)29     |

|   | 2.2.3.3 System Tick Timer Current Value register (SYSTIC  | CK_VAL)30     |

|   | 2.2.3.4 System Tick Timer Calibration Value register (SYS | ST_CALIB) 30  |

|   | 2.3 NESTED VECTORED INTERRUPT CONTROLLER (NV              | VIC)31        |

|   | 2.3.1 INTERRUPT AND EXCEPTION VECTORS                     | 31            |

|   | 2.3.2 NVIC REGISTERS                                      | 31            |

|   | 2.3.2.1 IRQ0~31 Interrupt Set-Enable Register (NVIC_ISE   | ER) 32        |

|   | 2.3.2.2 IRQ0~31 Interrupt Clear-Enable Register (NVIC_I   | CER) 32       |

|   | 2.3.2.3 IRQ0~31 Interrupt Set-Pending Register (NVIC_IS   | SPR) 32       |

|   | 2.3.2.4 IRQ0~31 Interrupt Clear-Pending Register (NVIC_   | _ICPR) 32     |

|   | 2.3.2.5 IRQ0~31 Interrupt Priority Register (NVIC_IPRn)   | (n=0~7)33     |

|   | 2.4 APPLICATION INTERRUPT AND RESET CONTROL (A            | AIRC)33       |

|   | 2.5 CODE OPTION TABLE                                     | 35            |

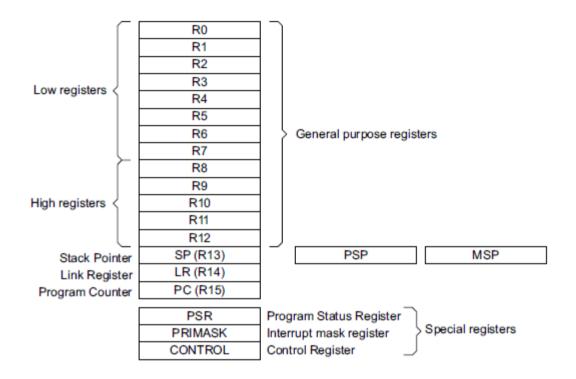

|   | 2.6 CORE REGISTER OVERVIEW                                |               |

| 3 | 3 SYSTEM CONTROL                                          |               |

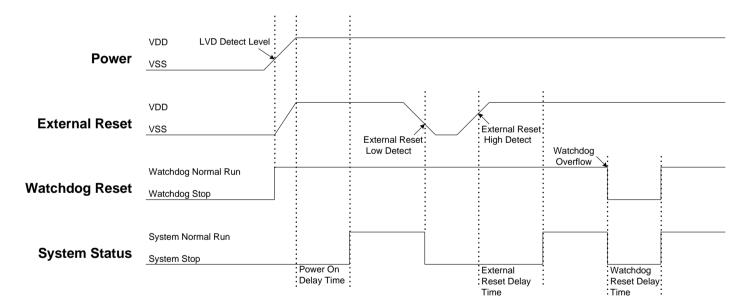

|   | 3.1 RESET                                                 |               |

|   | 3.1.1 POWER-ON RESET (POR)                                |               |

|   | 3.1.2 WATCHDOG RESET (WDT RESET)                          |               |

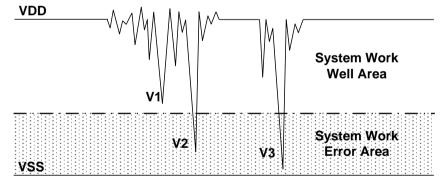

|   | 3.1.3 BROWN-OUT RESET                                     |               |

|   |                                                           |               |

| 3.1.3.1 | BROWN OUT DESCRIPTION                                | 38 |

|---------|------------------------------------------------------|----|

| 3.1.3.2 | THE SYSTEM OPERATING VOLTAGE DECSRIPTION             | 39 |

| 3.1.3.3 | BROWN-OUT RESET IMPROVEMENT                          | 39 |

| 3.1.4   | EXTERNAL RESET                                       | 40 |

| 3.1.4.1 | SIMPLY RC RESET CIRCUIT                              | 41 |

| 3.1.4.2 | DIODE & RC RESET CIRCUIT                             | 41 |

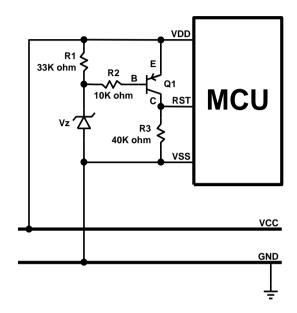

| 3.1.4.3 | ZENER DIODE RESET CIRCUIT                            | 42 |

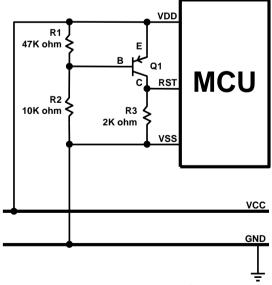

| 3.1.4.4 | VOLTAGE BIAS RESET CIRCUIT                           | 42 |

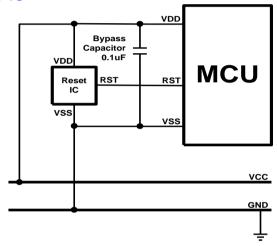

| 3.1.4.5 | EXTERNAL RESET IC                                    | 43 |

| 3.1.5   | SOFTWARE RESET                                       |    |

| 3.2 SYS | TEM CLOCK                                            | 44 |

| 3.2.1   | INTERNAL RC CLOCK SOURCE                             | 44 |

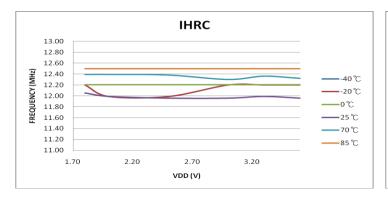

| 3.2.1.1 | Internal High-speed RC Oscillator (IHRC)             | 44 |

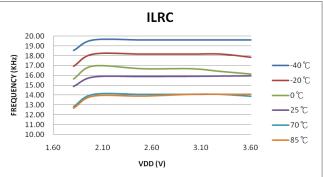

| 3.2.1.2 | Internal Low-speed RC Oscillator (ILRC)              | 44 |

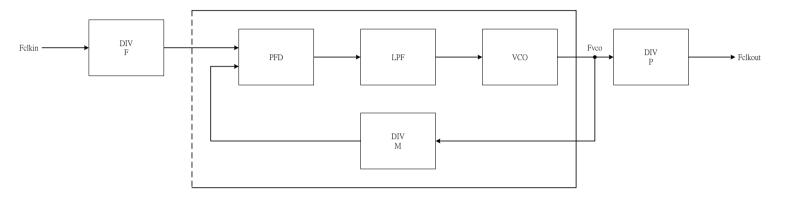

| 3.2.2   | PLL                                                  | 45 |

| 3.2.2.1 | PLL Frequency selection                              | 45 |

| 3.2.3   | EXTERNAL CLOCK SOURCE                                | 46 |

| 3.2.3.1 | External High-speed (EHS) Clock                      | 46 |

| 3.2.3.2 | CRYSTAL/CERAMIC                                      | 46 |

| 3.2.3.3 | Audio External High-speed (AUEHS) Clock              | 47 |

| 3.2.3.4 | External Low-speed (ELS) Clock                       | 47 |

| 3.2.3.5 | CRYSTAL                                              | 47 |

| 3.2.3.6 | Bypass Mode                                          | 48 |

| 3.2.4   | SYSTEM CLOCK (SYSCLK) SELECTION                      |    |

| 3.2.5   | CLOCK-OUT CAPABITITY                                 | 49 |

| 3.3 SYS | TEM CONTROL REGISTERS 0                              | 50 |

| 3.3.1   | Analog Block Control register (SYSO_ANBCTRL)         | 50 |

| 3.3.2   | PLL control register (SYSO_PLLCTRL)                  | 50 |

| 3.3.2.1 | RECOMMEND FREQUENCY SETTING                          | 51 |

| 3.3.3   | Clock Source Status register (SYSO_CSST)             |    |

| 3.3.4   | System Clock Configuration register (SYSO_CLKCFG)    | 52 |

| 3.3.5   | AHB Clock Prescale register (SYSO_AHBCP)             | 52 |

| 3.3.6   | System Reset Status register (SYSO_RSTST)            | 53 |

| 3.3.7   | LVD Control register (SYS0_LVDCTRL)                  | 53 |

| 3.3.8   | External RESET Pin Control register (SYSO_EXRSTCTRL) | 55 |

| 3.3.9   | SWD Pin Control register (SYS0_SWDCTRL)              | 55 |

| 3.4 SYS | TEM CONTROL REGISTERS 1                              | 56 |

| 3.4.1   | AHB Clock Enable register (SYS1_AHBCLKEN)            | 56 |

| 3.4.2   | APB Clock Prescale register 0 (SYS1_APBCP0)          | 57 |

| 3.4.3   | APB Clock Prescale register 1 (SYS1_APBCP1)          | 58 |

| 3.4.4         | Peripheral Reset register (SYS1_PRST)                                  | 59 |

|---------------|------------------------------------------------------------------------|----|

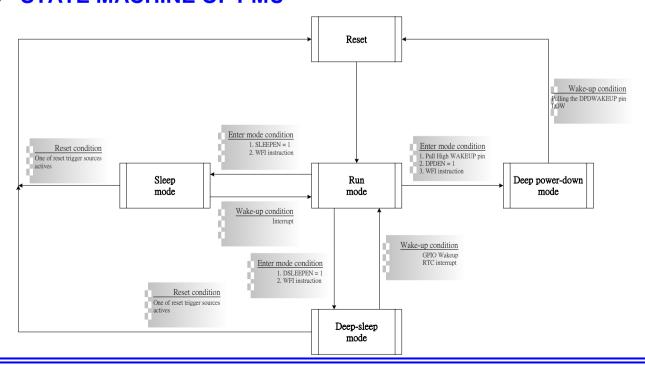

| 4 SYST        | EM OPERATION MODE                                                      | 61 |

| 4.1           | OVERVIEW                                                               | 61 |

| 4.2 N         | NORMAL MODE                                                            | 61 |

| 4.3 L         | OW-POWER MODES                                                         | 61 |

| 4.3.1         | SLEEP MODE                                                             | 61 |

| 4.3.2         | DEEP-SLEEP MODE                                                        | 62 |

| 4.3.3         | DEEP POWER-DOWN (DPD) MODE                                             | 62 |

| 4.3.          | 3.1 Entering Deep power-down mode                                      | 63 |

| 4.3.          | 3.2 Exiting Deep power-down mode                                       | 63 |

| 4.4 V         | VAKEUP INTERRUPT                                                       | 63 |

| 4.5 V         | VAKEUP                                                                 |    |

| 4.5.1         | OVERVIEW                                                               |    |

| 4.5.2         | WAKEUP TIME                                                            |    |

|               | TATE MACHINE OF PMU                                                    |    |

|               | PERATION MODE COMPARSION TABLE                                         |    |

|               | MU REGISTERS                                                           |    |

| 4.8.1         | Backup registers 0 to 15 (PMU_BKP0~15)                                 |    |

| 4.8.2         | Power control register (PMU_CTRL)                                      | 66 |

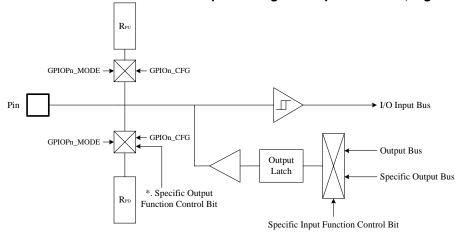

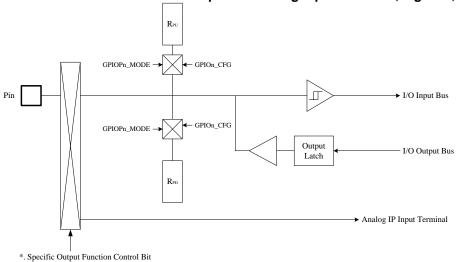

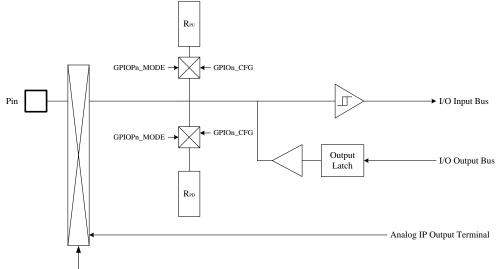

| <b>5</b> GENI | ERAL PURPOSE I/O PORT (GPIO)                                           | 67 |

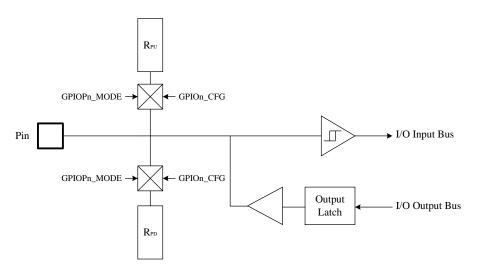

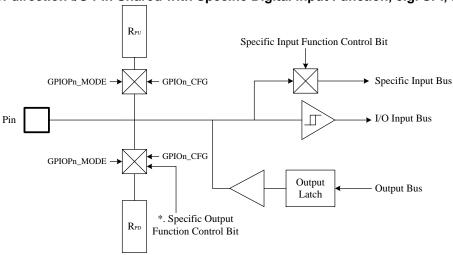

| 5.1           | OVERVIEW                                                               | 67 |

| 5.2           | SPIO MODE                                                              | 67 |

| 5.3           | SPIO REGISTERS                                                         | 68 |

| 5.3.1         | GPIO Port n Data register (GPIOn_DATA) (n=0,1,2,3)                     | 68 |

| 5.3.2         | GPIO Port n Mode register (GPIOn_MODE) (n=0,1,2,3)                     |    |

| 5.3.3         | GPIO Port n Configuration register (GPIOn_CFG) (n=0,1,2,3)             | 68 |

| 5.3.4         | GPIO Port n Interrupt Sense register (GPIOn_IS) (n=0,1,2,3)            | 70 |

| 5.3.5         | GPIO Port n Interrupt Both-edge Sense register (GPIOn_IBS) (n=0,1,2,3) | 70 |

| 5.3.6         | GPIO Port n Interrupt Event register (GPIOn_IEV) (n=0,1,2,3)           |    |

| 5.3.7         | GPIO Port n Interrupt Enable register (GPIOn_IE) (n=0,1,2,3)           |    |

| 5.3.8         | GPIO Port n Raw Interrupt Status register (GPIOn_RIS) (n=0,1,2,3)      |    |

| 5.3.9         | GPIO Port n Interrupt Clear register (GPIOn_IC) (n=0,1,2,3)            |    |

| 5.3.10        |                                                                        |    |

| 5.3.11        |                                                                        |    |

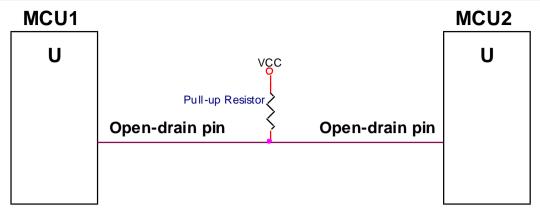

| 5.3.12        | GPIO Port n Open-Drain Control register (GPIOn_ODCTRL) (n=0,1,2,3)     | 71 |

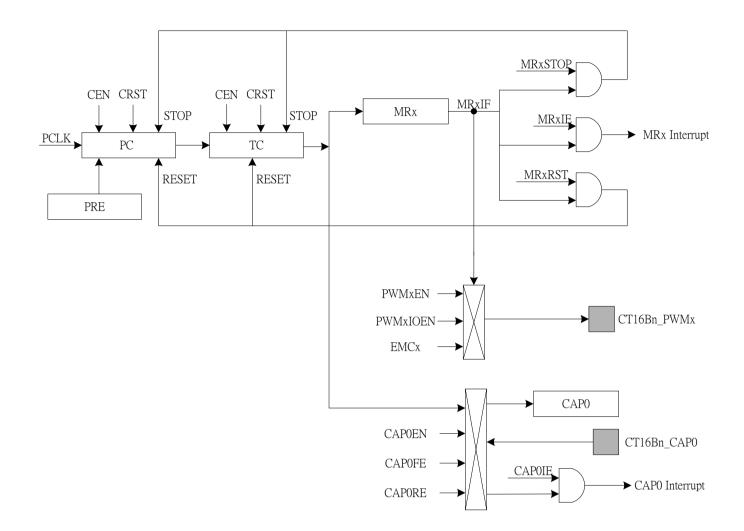

| 6 16-BI       | T TIMER WITH CAPTURE FUNCTION                                          | 74 |

|               | OVERVIEW                                                               |    |

| 6.2 F         | EATURES                                                                | 74 |

| 6.3         | PI   | N DESCRIPTION                                                   | 74 |

|-------------|------|-----------------------------------------------------------------|----|

| 6.4         | BI   | OCK DIAGRAM                                                     | 75 |

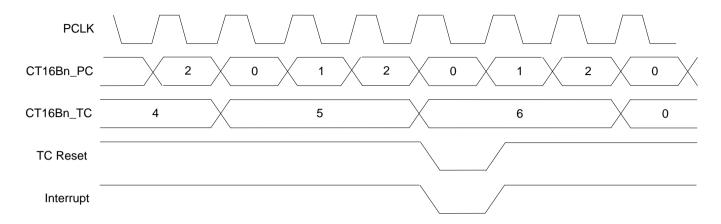

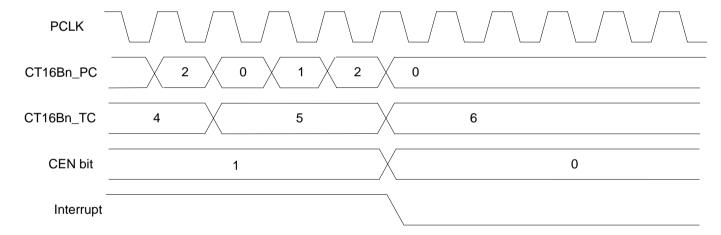

| 6.5         | TI   | MER OPERATION                                                   | 76 |

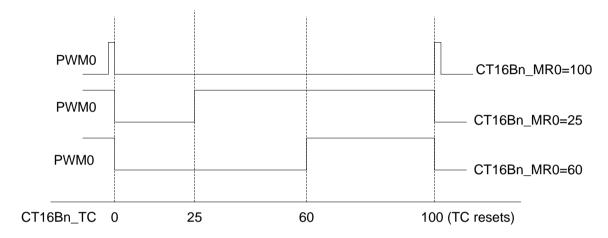

| 6.6         | PV   | VM                                                              | 77 |

| 6.7         | C    | T16BN REGISTERS                                                 | 78 |

| 6.7         | 7.1  | CT16Bn Timer Control register (CT16Bn_TMRCTRL) (n=0,1)          | 78 |

| 6.7         | 7.2  | CT16Bn Timer Counter register (CT16Bn_TC) (n=0,1)               | 78 |

| 6.7         | 7.3  | CT16Bn Prescale register (CT16Bn_PRE) (n=0,1)                   | 78 |

| 6.7         | 7.4  | CT16Bn Prescale Counter register (CT16Bn_PC) (n=0,1)            | 78 |

| 6.7         | 7.5  | CT16Bn Count Control register (CT16Bn_CNTCTRL) (n=0,1)          | 79 |

| 6.7         | 7.6  | CT16Bn Match Control register (CT16Bn_MCTRL) (n=0,1)            | 79 |

| 6.7         | 7.7  | CT16Bn Match register 0~3 (CT16Bn_MR0~3) (n=0,1)                | 80 |

| 6.7         | 7.8  | CT16Bn Capture Control register (CT16Bn_CAPCTRL) (n=0,1)        | 80 |

| 6.7         | 7.9  | CT16Bn Capture 0 register (CT16Bn_CAP0) (n=0,1)                 | 81 |

| 6.7         | 7.10 | CT16Bn External Match register (CT16Bn_EM) (n=0,1)              | 81 |

| 6.7         | 7.11 | CT16Bn PWM Control register (CT16Bn_PWMCTRL) (n=0,1)            | 81 |

| 6.7         | 7.12 | CT16Bn Timer Raw Interrupt Status register (CT16Bn_RIS) (n=0,1) | 82 |

| 6.7         | 7.13 | CT16Bn Timer Interrupt Clear register (CT16Bn_IC) (n=0,1)       | 82 |

| <b>7</b> 32 | -BIT | TIMER WITH CAPTURE FUNCTION                                     | 83 |

| 7.1         | O,   | /ERVIEW                                                         | 83 |

| 7.2         | FE   | ATURES                                                          | 83 |

| 7.3         | PI   | N DESCRIPTION                                                   | 83 |

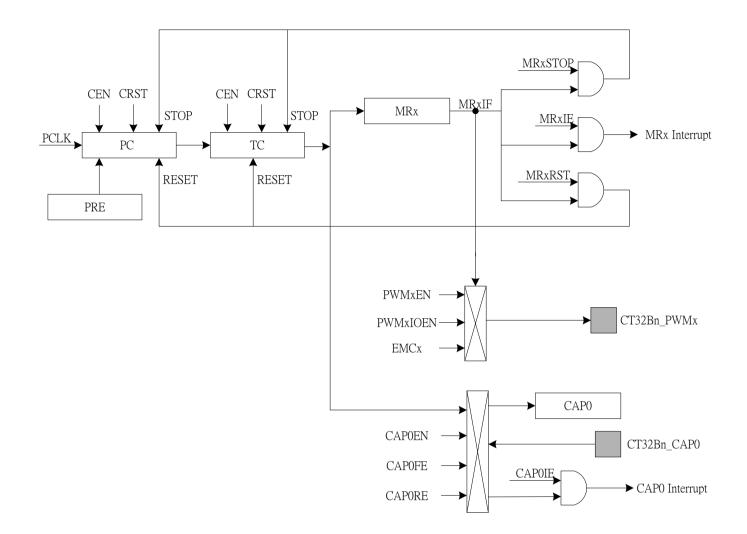

| 7.4         | BI   | OCK DIAGRAM                                                     | 84 |

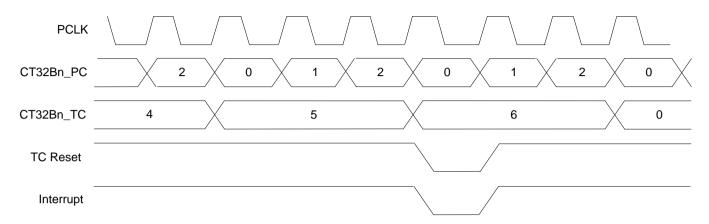

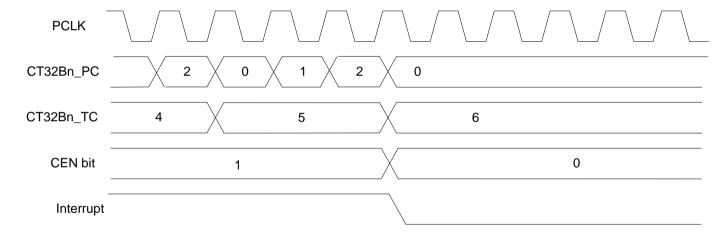

| 7.5         | TI   | MER OPERATION                                                   | 85 |

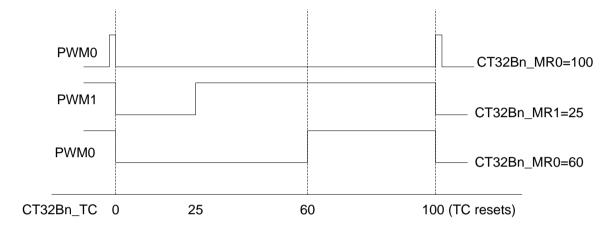

| 7.6         | PV   | VM                                                              | 86 |

| 7.7         | C    | C32BN REGISTERS                                                 | 87 |

| 7.7         | 7.1  | CT32Bn Timer Control register (CT32Bn_TMRCTRL) (n=0,1)          | 87 |

| 7.7         | 7.2  | CT32Bn Timer Counter register (CT32Bn_TC) (n=0,1)               | 87 |

| 7.7         | 7.3  | CT32Bn Prescale register (CT32Bn_PRE) (n=0,1)                   | 87 |

| 7.7         | 7.4  | CT32Bn Prescale Counter register (CT32Bn_PC) (n=0,1)            | 87 |

| 7.7         | 7.5  | CT32Bn Count Control register (CT32Bn_CNTCTRL) (n=0,1)          | 88 |

| 7.7         | 7.6  | CT32Bn Match Control register (CT32Bn_MCTRL) (n=0,1)            | 88 |

| 7.7         | 7.7  | CT32Bn Match register 0~3 (CT32Bn_MR0~3) (n=0,1)                | 89 |

| 7.7         | 7.8  | CT32Bn Capture Control register (CT32Bn_CAPCTRL) (n=0,1)        | 89 |

| 7.7         | 7.9  | CT32Bn Capture 0 register (CT32Bn_CAP0) (n=0,1)                 | 90 |

| 7.7         | 7.10 | CT32Bn External Match register (CT32Bn_EM) (n=0,1)              | 90 |

| 7.7         | 7.11 | CT32Bn PWM Control register (CT32Bn_PWMCTRL) (n=0,1)            | 90 |

| 7.7         | 7.12 | CT32Bn Timer Raw Interrupt Status register (CT32Bn_RIS) (n=0,1) | 91 |

| 7.7         | 7.13 | CT32Bn Timer Interrupt Clear register (CT32Bn_IC) $(n=0,1)$     | 91 |

| 8  | WATC    | CHDOG TIMER (WDT)                                      | 92  |

|----|---------|--------------------------------------------------------|-----|

| 8  | 8.1 O'  | VERVIEW                                                | 92  |

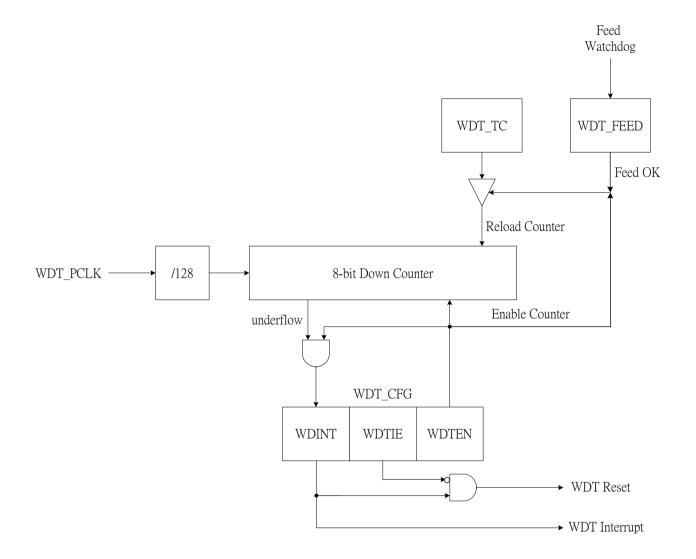

| 8  | 8.2 BI  | LOCK DIAGRAM                                           | 93  |

| 8  | 8.3 W   | DT REGISTERS                                           | 94  |

|    | 8.3.1   | Watchdog Configuration register (WDT_CFG)              | 94  |

|    | 8.3.2   | Watchdog Clock Source register (WDT_CLKSOURCE)         | 94  |

|    | 8.3.3   | Watchdog Timer Constant register (WDT_TC)              | 94  |

|    | 8.3.4   | Watchdog Feed register (WDT_FEED)                      | 95  |

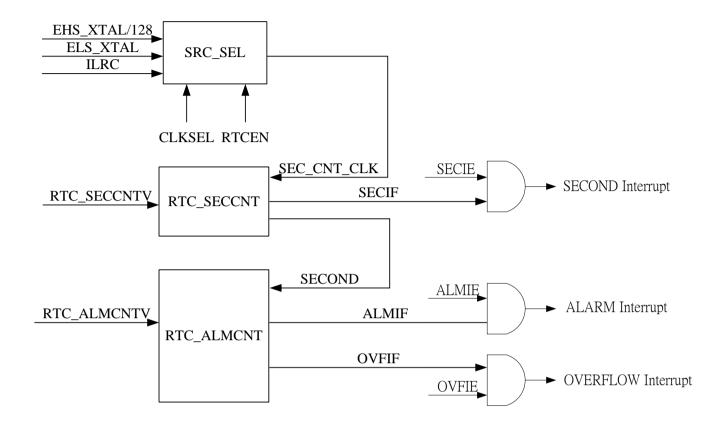

| 9  | REAL.   | TIME CLOCK (RTC)                                       | 96  |

| Ģ  | 9.1 O'  | VERVIEW                                                | 96  |

| 9  | 9.2 FE  | EATURES                                                | 96  |

| 9  | 9.3 FU  | JNCTIONAL DESCRIPTION                                  | 96  |

|    | 9.3.1   | INTRODUCTION                                           |     |

|    | 9.3.2   | RESET RTC REGISTERS                                    |     |

|    | 9.3.3   | RTC FLAG ASSERTION                                     |     |

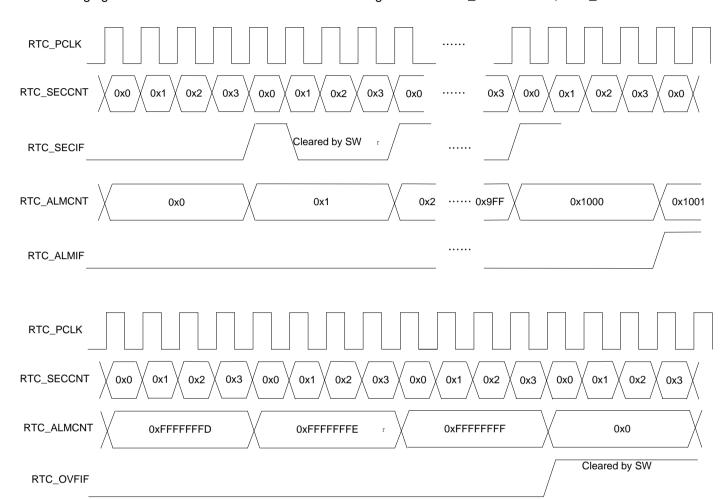

|    | 9.3.4   | RTC OPERATION                                          | 97  |

| Ç  | 9.4 BI  | LOCK DIAGRAM                                           | 98  |

| 9  | 9.5 RT  | TC REGISTERS                                           | 99  |

|    | 9.5.1   | RTC Control register (RTC_CTRL)                        | 99  |

|    | 9.5.2   | RTC Clock Source Select register (RTC_CLKS)            | 99  |

|    | 9.5.3   | RTC Interrupt Enable register (RTC_IE)                 | 99  |

|    | 9.5.4   | RTC Raw Interrupt Status register (RTC_RIS)            | 99  |

|    | 9.5.5   | RTC Interrupt Clear register (RTC_IC)                  |     |

|    | 9.5.6   | RTC Second Counter Reload Value register (RTC_SECCNTV) |     |

|    | 9.5.7   | RTC Second Count register (RTC_SECCNT)                 |     |

|    | 9.5.8   | RTC Alarm Counter Reload Value register (RTC_ALMCNTV)  |     |

|    | 9.5.9   | RTC Alarm Count register (RTC_ALMCNT)                  | 101 |

| 10 | SPI/    | SSP                                                    | 102 |

|    | 10.1 O' | VERVIEW                                                | 102 |

|    | 10.2 FE | EATURES                                                | 102 |

|    | 10.3 PI | N DESCRIPTION                                          | 103 |

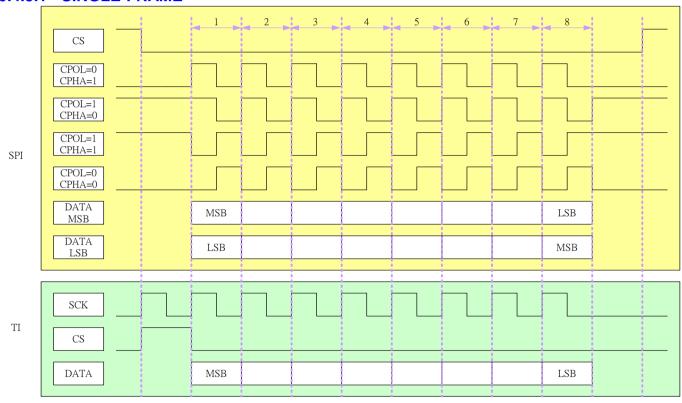

|    | 10.4 IN | TERFACE DESCRIPTION                                    | 104 |

|    | 10.4.1  | SPI                                                    |     |

|    | 10.4.2  | SSI                                                    |     |

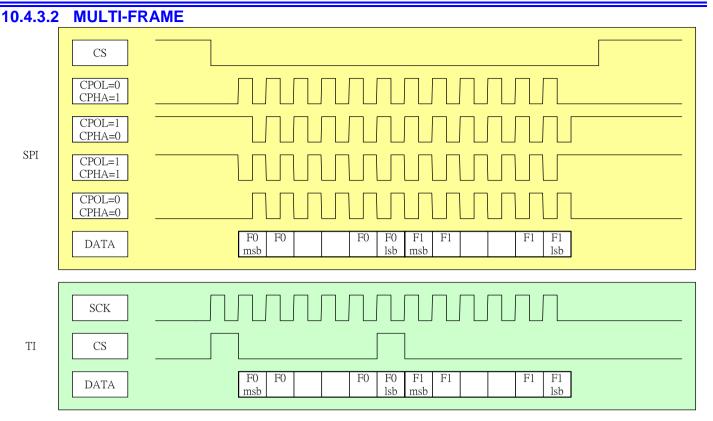

|    | 10.4.3  | COMMUNICATION FLOW                                     | 105 |

|    | 10.4.   | 3.1 SINGLE-FRAME                                       | 105 |

|    | 10.4.   | 3.2 MULTI-FRAME                                        | 106 |

| -  | 10.5 Au | JTO-SEL (AUTO-CS)                                      | 106 |

| 10.6 SSP REGISTERS                                                | 107              |

|-------------------------------------------------------------------|------------------|

| 10.6.1 SSP n Control register 0 (SSPn_CTRL0) (n=0, 1)             |                  |

| 10.6.2 SSP n Control register 1 (SSPn_CTRL1) (n=0, 1)             |                  |

| 10.6.3 SSP n Clock Divider register (SSPn_CLKDIV) (n=0, 1)        |                  |

| 10.6.4 SSP n Status register (SSPn_STAT) (n=0, 1)                 |                  |

| 10.6.5 SSP n Interrupt Enable register (SSPn_IE) (n=0, 1)         |                  |

| 10.6.6 SSP n Raw Interrupt Status register (SSPn_RIS) $(n=0, 1)$  |                  |

| 10.6.7 SSP n Interrupt Clear register (SSPn_IC) $(n=0, 1)$        |                  |

| 10.6.8 SSP n Data register (SSPn_DATA) (n=0, 1)                   | 110              |

| 10.6.9 SSP n Data Fetch register (SSPn_DF) (n=0, 1)               |                  |

| <b>11</b> I2C                                                     |                  |

| 11.1 OVERVIEW                                                     | 111              |

| 11.2 FEATURES                                                     | 111              |

| 11.3 PIN DESCRIPTION                                              | 112              |

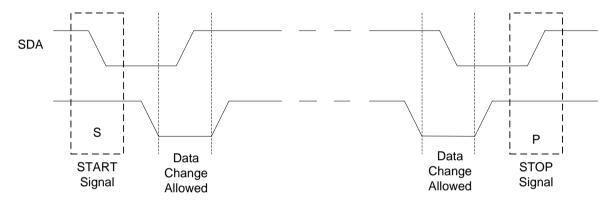

| 11.4 WAVE CHARACTERISTICS                                         | 112              |

| 11.5 I2C MASTER MODES                                             | 113              |

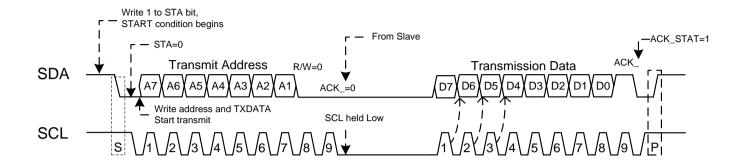

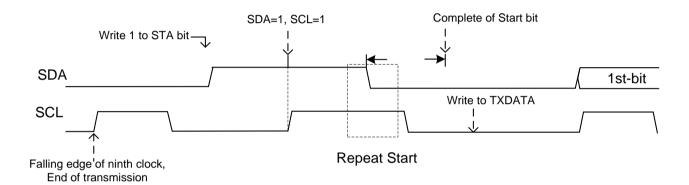

| 11.5.1 MASTER TRANSMITTER MODE                                    |                  |

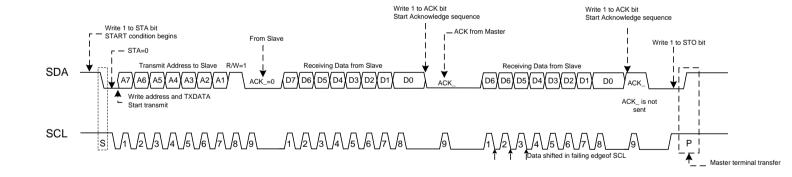

| 11.5.2 MASTER RECEIVER MODE                                       |                  |

| 11.5.3 ARBITRATION                                                |                  |

| 11.6 I2C SLAVE MODES                                              | 114              |

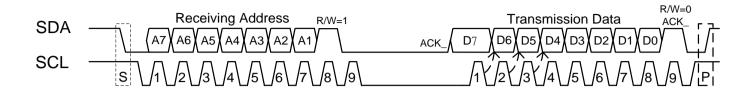

| 11.6.1 SLAVE TRANSMITTER MODE                                     | 114              |

| 11.6.2 SLAVE RECEIVER MODE                                        | 114              |

| 11.7 MONITOR MODE                                                 |                  |

| 11.7.1 INTERRUPT                                                  |                  |

| 11.7.2 LOSS of ARBITRATION                                        |                  |

| 11.8 I2C REGISTERS                                                | 116              |

| 11.8.1 I2C n Control register (I2Cn_CTRL) (n=0,1)                 | 116              |

| 11.8.2 I2C n Status register (I2Cn_STAT) (n=0,1)                  | 117              |

| 11.8.3 I2C n TX Data register (I2Cn_TXDATA) (n=0,1)               | 118              |

| 11.8.4                                                            | 118              |

| 11.8.5 I2C n Slave Address 0 register (I2Cn_SLVADDR0) $(n=0,1)$ . | 118              |

| 11.8.6 I2C n Slave Address 1~3 register (I2Cn_SLVADDR1~3) (n=     | =0,1) 118        |

| 11.8.7 I2C n SCL High Time register (I2Cn_SCLHT) (n=0,1)          |                  |

| 11.8.8 I2C n SCL Low Time register (I2Cn_SCLLT) (n=0,1)           |                  |

| 11.8.9 I2C n Timeout Control register (I2Cn_TOCTRL) (n=0,1)       |                  |

| 11.8.10 I2C n Monitor Mode Control register (I2Cn_MMCTRL) (       | n=0,1)119        |

| 12 UNIVERSAL ASYNCHRONOUS RECEIVER AND TRANSM                     | ITTER (UART) 121 |

|                                                                   |                  |

Page 8

| 12.2 FE  | ATURES                                                              | 121 |

|----------|---------------------------------------------------------------------|-----|

| 12.3 PIN | N DESCRIPTION                                                       | 121 |

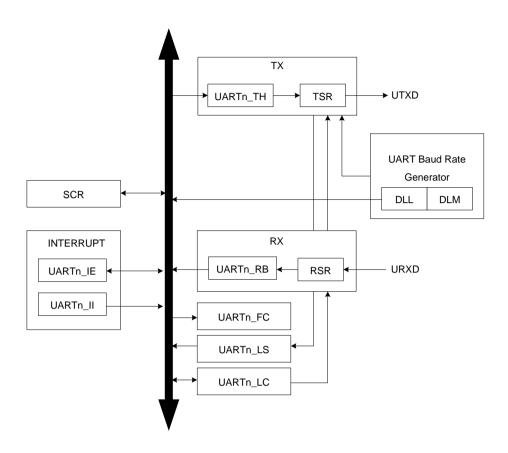

| 12.4 BL  | OCK DIAGRAM                                                         | 122 |

| 12.5 BA  | UD RATE CALCULATION                                                 | 123 |

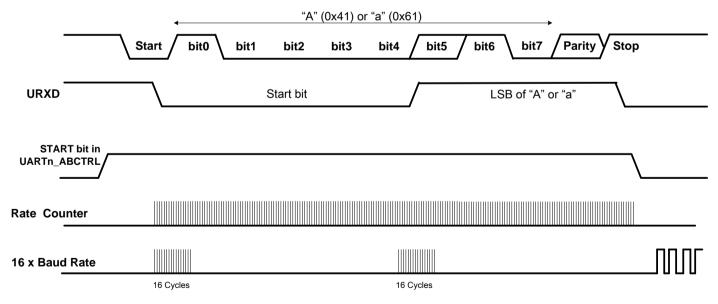

| 12.6 AU  | TO-BAUD FLOW                                                        | 124 |

| 12.6.1   | AUTO-BAUD                                                           | 124 |

| 12.6.2   | AUTO-BAUD MODES                                                     |     |

| 12.7 UA  | RT REGISTERS                                                        | 127 |

| 12.7.1   | UART n Receiver Buffer register (UARTn_RB) (n=0, 1)                 | 127 |

| 12.7.2   | UART n Transmitter Holding register (UARTn_TH) (n=0, 1)             | 127 |

| 12.7.3   | UART n Divisor Latch LSB registers (UARTn_DLL) (n =0, 1)            | 127 |

| 12.7.4   | UART n Divisor Latch MSB register (UARTn_DLM) (n=0,1)               | 127 |

| 12.7.5   | UART n Interrupt Enable register (UARTn_IE) (n=0, 1)                |     |

| 12.7.6   | UART n Interrupt Identification register (UARTn_II) (n=0,1)         |     |

| 12.7.7   | UART n FIFO Control register (UARTn_FIFOCTRL) (n=0,1)               |     |

| 12.7.8   | UART n Line Control register (UARTn_LC) (n=0,1)                     |     |

| 12.7.9   | UART n Line Status register (UARTn_LS) (n=0,1)                      |     |

| 12.7.10  | UART n Scratch Pad register (UARTn_SP) (n=0, 1)                     |     |

| 12.7.11  | UART n Auto-baud Control register (UARTn_ABCTRL) (n=0, 1)           |     |

| 12.7.12  | $UART\ n\ Fractional\ Divider\ register\ (UARTn\_FD)\ (n=0,\ 1)$    |     |

| 12.7.13  | UART n Control register (UARTn_CTRL) (n=0, 1)                       |     |

| 12.7.14  | $UART\ n\ Half-duplex\ Enable\ register\ (UARTn\_HDEN)\ (n=0,\ 1)\$ |     |

| 13 AUD   | IO (I2S/CODEC)                                                      | 135 |

| 13.1 OV  | ERVIEW                                                              | 135 |

| 13.1.1   | I2S Description                                                     |     |

| 13.1.2   | Codec Description                                                   |     |

|          | ATURES                                                              |     |

| 13.2.1   | I2S Features                                                        |     |

| 13.2.2   | Codec Features                                                      |     |

| 13.3 PIN | V DESCRIPTION                                                       |     |

| 13.3.1   | I2S Pin Description                                                 |     |

| 13.3.2   | Codec Pin Description                                               |     |

| 13.3.3   | Audio Clock Pin Description                                         |     |

| 13.4 BL  | OCK DIAGRAM                                                         |     |

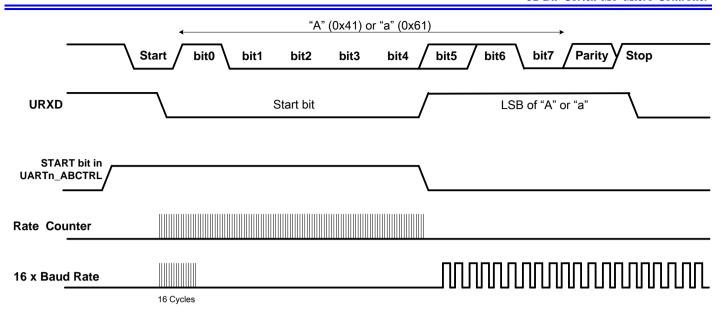

| 13.4.1   | I2S CLCOK CONTROL                                                   |     |

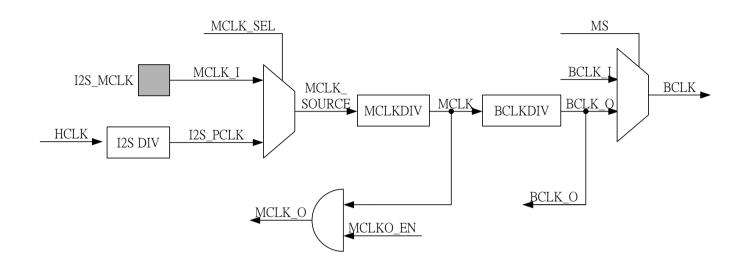

| 13.4.2   | I2S BLOCK DIAGRAM                                                   |     |

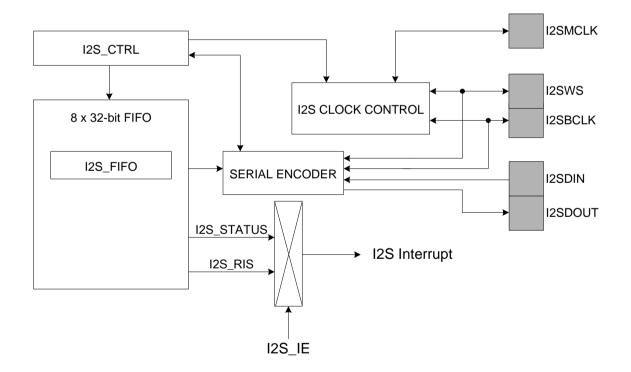

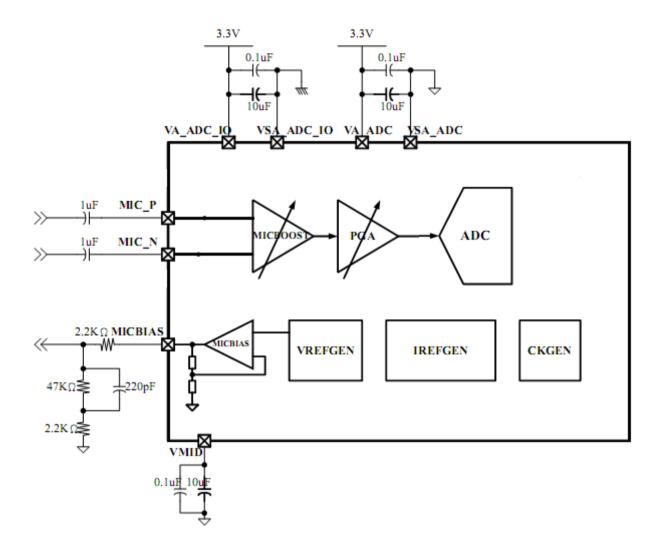

| 13.4.3   | 16-Bit Sigma-Delta ADC BLOCK DIAGRAM                                |     |

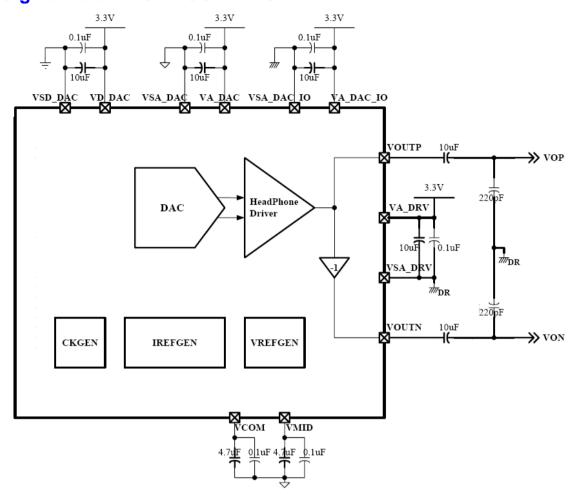

| 13.4.4   | 16-Bit Sigma-Delta DAC BLOCK DIAGRAM                                |     |

| 13.5 FU  | NCTIONAL DESCRIPTION                                                |     |

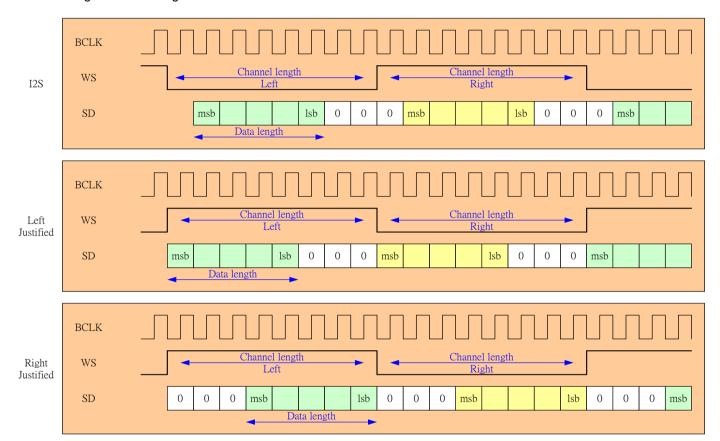

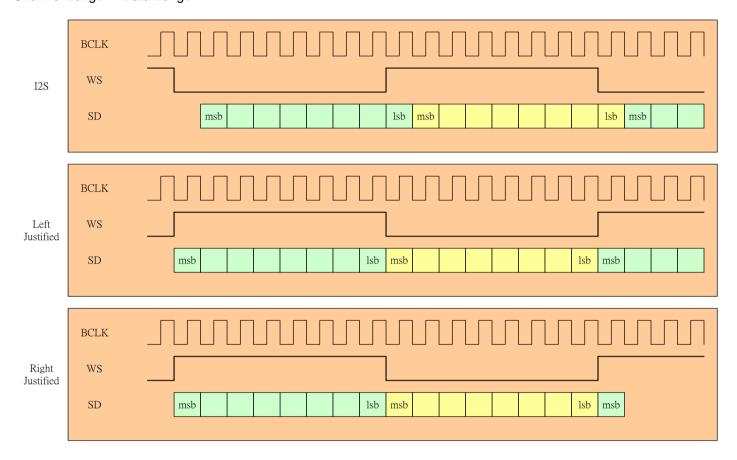

| 13       | 3.5.1  | I2S OPERATION                               | 140 |

|----------|--------|---------------------------------------------|-----|

| 13       | 3.5.2  | I2S FIFO OPERAION                           | 142 |

| 13.5.2.1 |        | .1 MONO                                     | 142 |

|          | 13.5.2 | .2 STEREO                                   | 142 |

| 13.6     | I2S    | REGISTERS                                   | 143 |

| 13       | 3.6.1  | I2S Control register (I2S_CTRL)             | 143 |

| 13       | 3.6.2  | I2S Clock register (I2S_CLK)                | 144 |

| 13       | 3.6.3  | I2S Status register (I2S_STATUS)            | 144 |

| 13       | 3.6.4  | I2S Interrupt Enable register (I2S_IE)      | 145 |

| 13       | 3.6.5  | I2S Raw Interrupt Status register (I2S_RIS) | 145 |

| 13       | 3.6.6  | I2S Interrupt Clear register (I2S_IC)       | 146 |

| 13       | 3.6.7  | I2S RX FIFO register (I2S_RXFIFO)           | 146 |

| 13       | 3.6.8  | I2S TX FIFO register (I2S_TXFIFO)           | 146 |

| 13.7     | CO     | DEC ADC REGISTERS                           | 146 |

| 13       | 3.7.1  | ADC Setting 1 register (ADC_SET1)           |     |

| 13       | 3.7.2  | ADC Setting 2 register (ADC_SET2)           | 147 |

| 13       | 3.7.3  | ADC Setting 3 register (ADC_SET3)           |     |

| 13       | 3.7.4  | ADC Setting 4 register (ADC_SET4)           | 147 |

| 13       | 3.7.5  | ADC Setting 5 register (ADC_SET5)           |     |

| 13       | 3.7.6  | ADC Setting 6 register (ADC_SET6)           | 147 |

| 13       | 3.7.7  | ADC Setting 7 register (ADC_SET7)           |     |

| 13       | 3.7.8  | ADC Setting 8 register (ADC_SET8)           | 148 |

| 13       | 3.7.9  | ADC Setting 9 register (ADC_SET9)           |     |

| 13       | 3.7.10 | ADC Setting 10 register (ADC_SET10)         |     |

| 13       | 3.7.11 | ADC Setting 11 register (ADC_SET11)         | 148 |

| 13       | 3.7.12 | ADC Setting 12 register (ADC_SET12)         | 148 |

| 13       | 3.7.13 | ADC Setting 13 register (ADC_SET13)         | 149 |

|          | 3.7.14 | ADC Setting 14 register (ADC_SET14)         |     |

| 13       | 3.7.15 | ADC Setting 15 register (ADC_SET15)         |     |

|          | 3.7.16 | ADC Setting 16 register (ADC_SET16)         |     |

|          | 3.7.17 | ADC Setting 18 register (ADC_SET18)         |     |

|          | 3.7.18 | ADC Setting 19 register (ADC_SET19)         |     |

|          | 3.7.19 | ADC Setting 20 register (ADC_SET20)         |     |

|          | 3.7.20 | ADC Setting 21 register (ADC_SET21)         |     |

|          | 3.7.21 | ADC Setting 22 register (ADC_SET22)         |     |

|          | 3.7.22 | ADC Setting 23 register (ADC_SET23)         |     |

|          | 3.7.23 | ADC Setting 24 register (ADC_SET24)         |     |

| 13.8     |        | DEC DAC REGISTERS                           |     |

|          | 3.8.1  | DAC Setting 1 register (DAC_SET1)           |     |

| 13       | 3.8.2  | DAC Setting 2 register (DAC_SET2)           | 152 |

| 13.8.3 DAC Setting 3 register (DAC_SET3)              |     |

|-------------------------------------------------------|-----|

| 13.8.4 DAC Setting 4 register (DAC_SET4)              |     |

| 13.8.5 DAC Status register (DAC_STATUS)               |     |

| 13.9 SIGMA-DELTA ADC CONTROL FLOW                     | 153 |

| 13.9.1 Sigma-delta ADC Power-up Sequence              |     |

| 13.9.2 Sigma-delta ADC Power-down Sequence            |     |

| 13.9.3 Sigma-delta ADC Enable Sequence                |     |

| 13.10 SIGMA-DELTA DAC CONTROL FLOW                    | 154 |

| 13.10.1 Sigma-delta DAC Power-up Sequence             |     |

| 13.10.2 Sigma-delta DAC Power-down Sequence           |     |

| 13.10.3 Sigma-delta DAC Enable Sequence               |     |

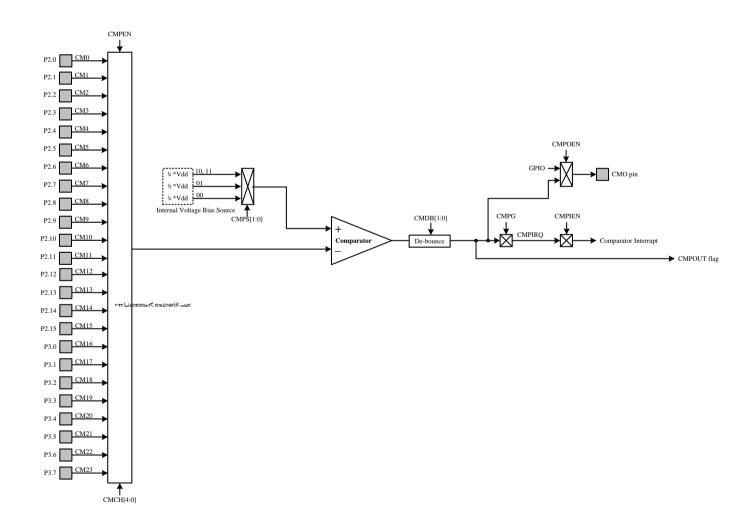

| 14 24-CHANNEL COMPARATOR                              | 155 |

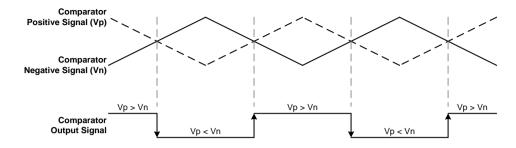

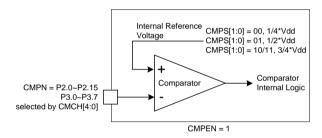

| 14.1 OVERVIEW                                         | 155 |

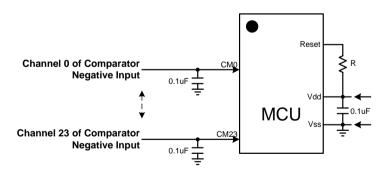

| 14.2 COMPARATOR OPERATION                             | 156 |

| 14.3 COMPARATOR APPLICATION NOTICE                    | 157 |

| 14.4 COMPARATOR CONTROL REGISTERS                     | 157 |

| 14.4.1 Comparator Control register (CMPM)             |     |

| 14.4.2 Comparator Interrupt Enable register (CMP_IE)  |     |

| 14.4.3 Comparator Interrupt Status register (CMP_RIS) |     |

| 14.4.4 Comparator Interrupt Clear register (CMP_IC)   |     |

| 15 FLASH                                              | 160 |

| 15.1 OVERVIEW                                         | 160 |

| 15.2 EMBEDDED FLASH MEMORY                            |     |

| 15.3 FEATURES                                         |     |

| 15.4 ORGANIZATION                                     |     |

| 15.5 READ                                             |     |

| 15.6 PROGRAM/ERASE                                    |     |

| 15.7 EMBEDDED BOOT LOADER                             |     |

| 15.8 FLASH MEMORY CONTROLLER (FMC)                    | 162 |

| 15.8.1 CODE SECURITY (CS)                             |     |

| 15.8.2 PROGRAM FLASH MEMORY                           |     |

| 15.8.3 ERASE                                          |     |

| 15.8.3.1 PAGE ERASE                                   | 163 |

| 15.8.3.2 MASS ERASE                                   | 163 |

| 15.9 READ PROTECTION                                  | 163 |

| 15.10 FMC REGISTERS                                   | 164 |

| 15.10.1 Flash Status register (FLASH_STATUS)          |     |

| 15.10.2 Flash Control register (FLASH_CTRL)           |     |

| 15.         | 10.3 Flash Data register (FLASH_DATA)           | 164 |

|-------------|-------------------------------------------------|-----|

| 15.         | 10.4 Flash Address register (FLASH_ADDR)        | 165 |

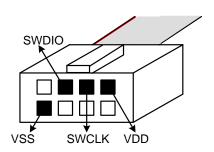

| 16          | SERIAL-WIRE DEBUG (SWD)                         | 166 |

| 16.1        | OVERVIEW                                        | 166 |

| 16.2        | FEATURES                                        | 166 |

| 16.3        | PIN DESCRIPTION                                 | 166 |

| 16.4        | DEBUG NOTE                                      | 166 |

| 16.         | 4.1 LIMITATIONS                                 | 166 |

| 16.         | 4.2 DEBUG RECOVERY                              | 166 |

| 16.         | 4.3 INTERNAL PULL-UP/DOWN RESISTORS on SWD PINS | 167 |

| <b>17</b> I | DEVELOPMENT TOOL                                | 168 |

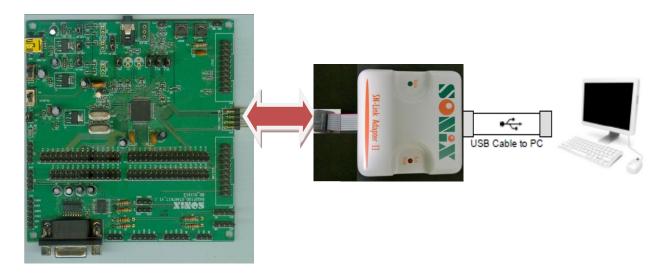

| 17.1        | SN-LINK-V2                                      | 169 |

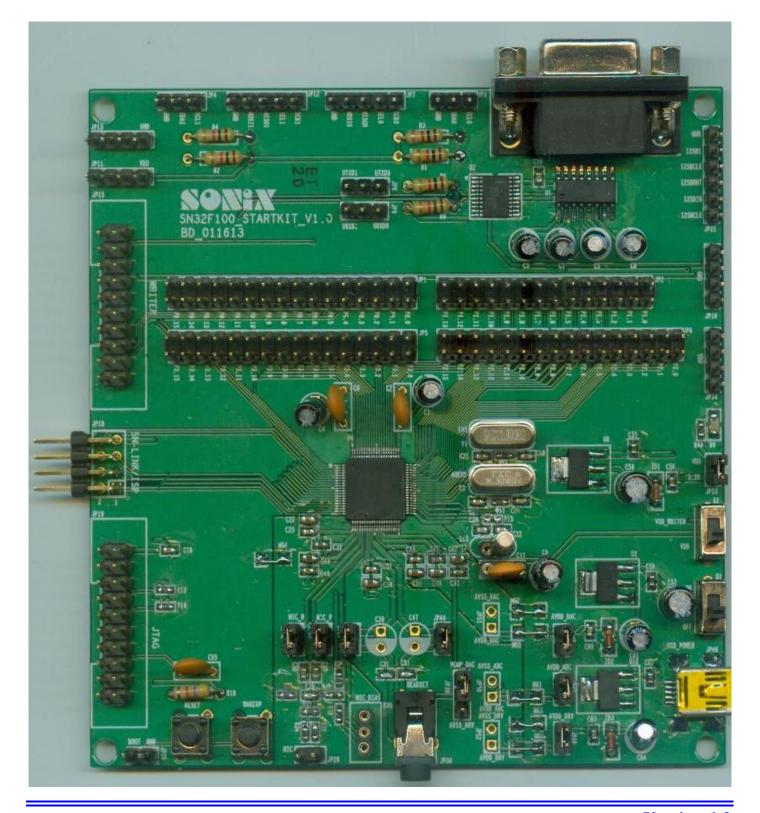

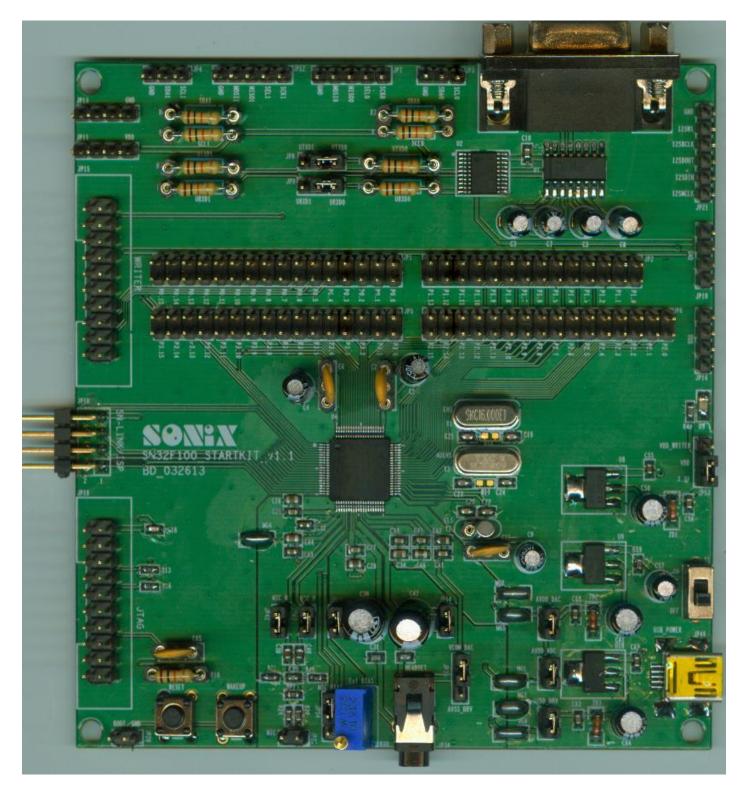

| 17.2        | SN32F100 STARTER-KIT                            | 170 |

| 17.         | 2.1 SN32F100 Start Kit V1.0                     | 170 |

| 17.         | 2.2 SN32F100 Start Kit V1.1/V1.2                |     |

| 18 I        | ELECTRICAL CHARACTERISTIC                       | 174 |

| 18.1        | ABSOLUTE MAXIMUM RATING                         | 174 |

| 18.2        | ELECTRICAL CHARACTERISTIC                       | 174 |

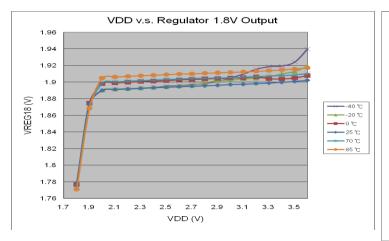

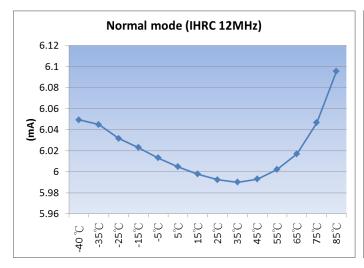

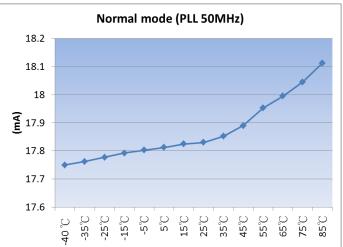

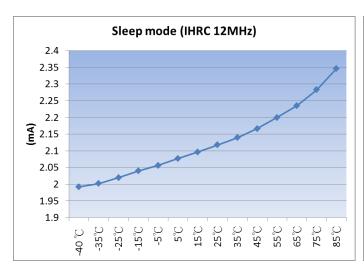

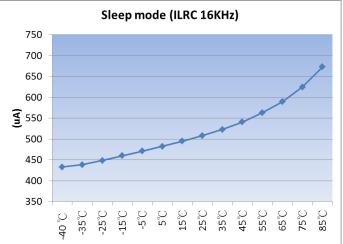

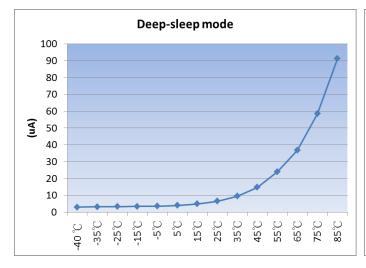

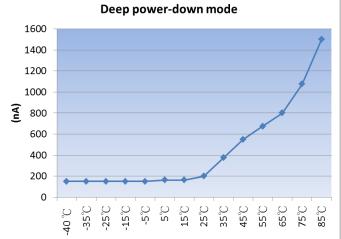

| 18.3        | CHARACTERISTIC GRAPHS                           | 176 |

| 19 I        | FLASH ROM PROGRAMMING PIN                       | 178 |

| <b>20</b> I | PACKAGE INFORMATION                             | 179 |

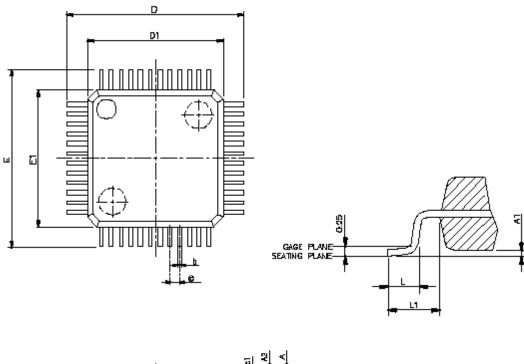

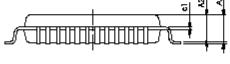

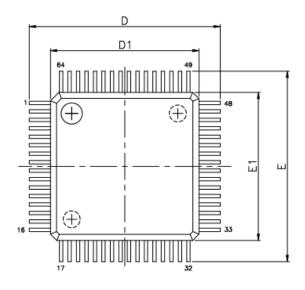

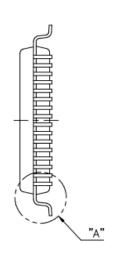

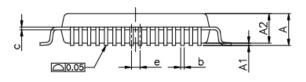

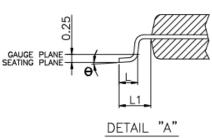

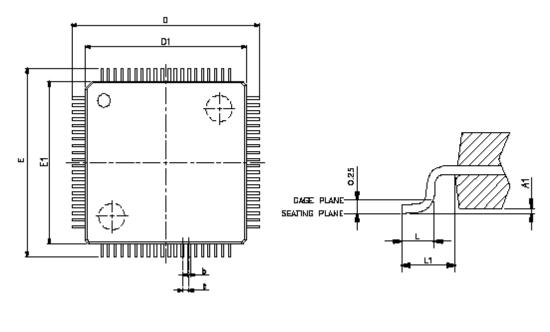

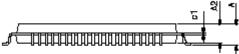

| 20.1        | LQFP 48 PIN                                     | 179 |

| 20.2        | LQFP 64 PIN                                     |     |

| 20.3        | LQFP 80 PIN                                     |     |

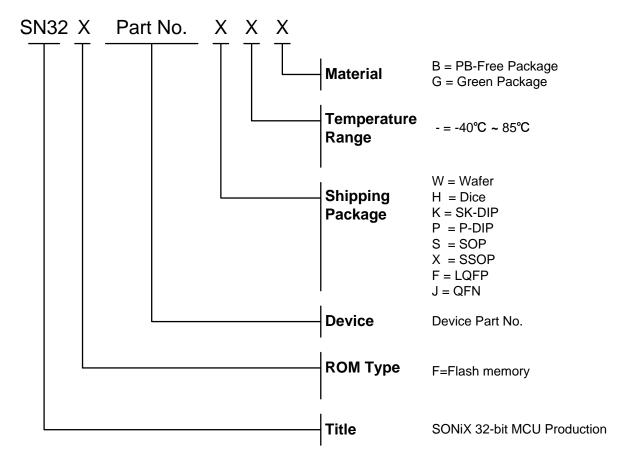

| <b>21</b> N | MARKING DEFINITION                              | 182 |

| 21.1        | INTRODUCTION                                    | 182 |

| 21.2        | MARKING INDETIFICATION SYSTEM                   |     |

| 21.3        | MARKING EXAMPLE                                 |     |

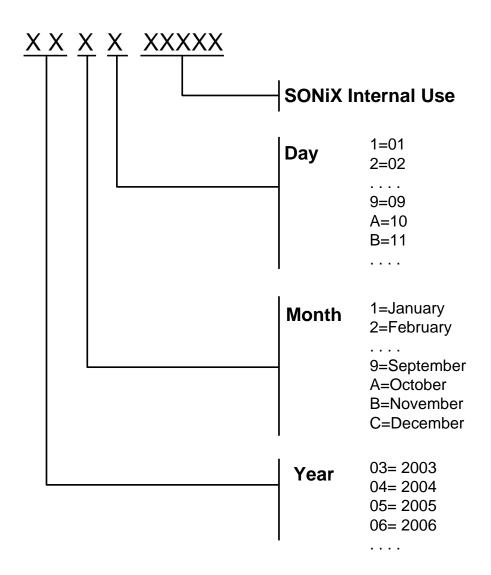

|             | DATECODE SYSTEM                                 | 183 |

# 1 PRODUCT OVERVIEW

### 1.1 FEATURES

### **♦** Memory configuration

64KB on-chip Flash programming memory. 8KB SRAM. 4KB Boot ROM

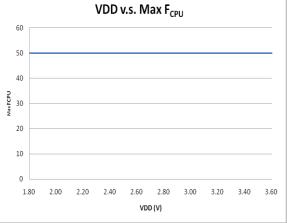

### ♦ Operation Frequency up to 50MHz

### Interrupt sources

ARM Cortex-M0 built-in Nested Vectored Interrupt Controller (NVIC).

### ♦ I/O pin configuration

Up to 62 General Purpose I/O (GPIO) pins with Configurable pull-up/pull-down resistors.

GPIO pins can be used as edge and level sensitive interrupt sources.

High-current source driver (20 mA) Comparator input pin: CM0~CM23. Comparator output pin: CMO.

### Programmable Watchdog Timer (WDT)

Programmable watchdog frequency with watchdog Clock source and divider.

### ♦ System tick timer

24-bit timer.

The system tick timer clock is fixed to the frequency of the system clock.

The SysTick timer is intended to generate a fixed 10-ms interrupt.

### ♦ Real-Time Clock (RTC)

### ♦ LVD with separate thresholds

Reset: 1.65V for  $V_{CORE}$  1.8V, 2.0/2.4/2.7V for VDD Interrupt: 2.0/2.4/2.7/3.0V for VDD

### ♦ Fcpu (Instruction cycle)

$F_{CPU} = F_{HCLK} = F_{SYSCLK}/1$ ,  $F_{SYSCLK}/2$ ,  $F_{SYSCLK}/4$ , ...,  $F_{SYSCLK}/512$ .

### ♦ Working voltage 1.8V ~ 3.6V

### Operating modes

Normal, Sleep, Deep-sleep, and Deep power-down

### ♦ Serial Wire Debug (SWD)

### ♦ In-System Programming (ISP) supported

#### ◆ Timer

Two 16-bit and two 32-bit general purpose timers with a total of four capture inputs, 6PWMs

#### DAC

16-bit Sigma-delta DAC for Audio. Can drive the L/R Channel Earphone. SNR 90dB. THD+N -75dB.

#### ADC

16-bit Sigma-delta ADC for Audio. AGC function. Differential Microphone input. Build-in Microphone Bias Voltage support. SNR 94dB. THD+N -80dB.

### 24-channel Comparator.

#### ◆ Interface

- -Two I2C controllers supporting I2C-bus specification with multiple address recognition and monitor mode.

- -Two UART controllers with fractional baud rate generation.

- -Two SPI controllers with SSP features and multiprotocol capabilities.

- -I2S Function with mono and stereo audio data supported, MSB justified data format supported, and can operate as either master or slave.

### ♦ System clocks

- -External high clock: Crystal type 10MHz~25MHz

- -External Audio high clock: Crystal type 16.384MHz

- -External low clock: Crystal type 32.768 KHz

- -Internal high clock: RC type 12 MHz

- -Internal low clock: RC type 16 KHz

- -PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. May be run from the external high clock or the internal high RC oscillator.

- -Clock output function which can reflect the internal high/low RC oscillator, HCLK, PLL output, and external high/low clock.

### Package (Chip form support)

LQFP 80 pin LQFP 64 pin LQFP 48 pin

Features Selection Table

| Chip      | ROM  | RAM | Boot<br>Loader | F <sub>CPU</sub> .<br>(Max<br>MHz) | UART | SPI | I2C | I2S | TIMER                    | PWM | 16-bit $\Sigma$ - $\delta$ ADC | 16-bit $\Sigma$ - $\delta$ DAC | СМР | GPIO<br>with<br>Wakeup | Package |

|-----------|------|-----|----------------|------------------------------------|------|-----|-----|-----|--------------------------|-----|--------------------------------|--------------------------------|-----|------------------------|---------|

| SN32F107F | 64KB | 8KB | 4KB            | 50                                 | 1    | 1   | 2   | -   | 16-bit x 2<br>32-bit x 2 | 4   | 1                              | 1                              | 8   | 32                     | LQFP48  |

| SN32F108F | 64KB | 8KB | 4KB            | 50                                 | 2    | 1   | 2   | -   | 16-bit x 2<br>32-bit x 2 | 6   | 1                              | 1                              | 17  | 46                     | LQFP64  |

| SN32F109F | 64KB | 8KB | 4KB            | 50                                 | 2    | 2   | 2   | 1   | 16-bit x 2<br>32-bit x 2 | 6   | 1                              | 1                              | 24  | 62                     | LQFP80  |

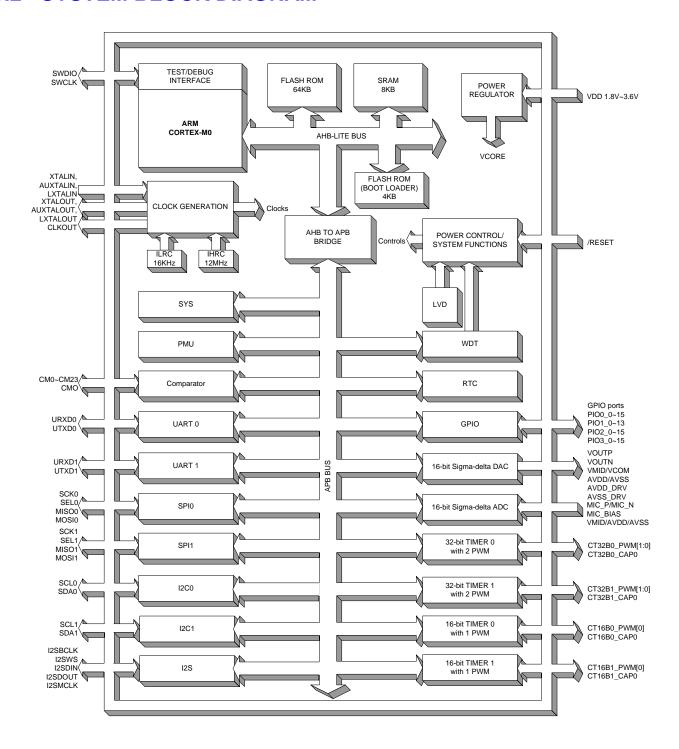

# 1.2 SYSTEM BLOCK DIAGRAM

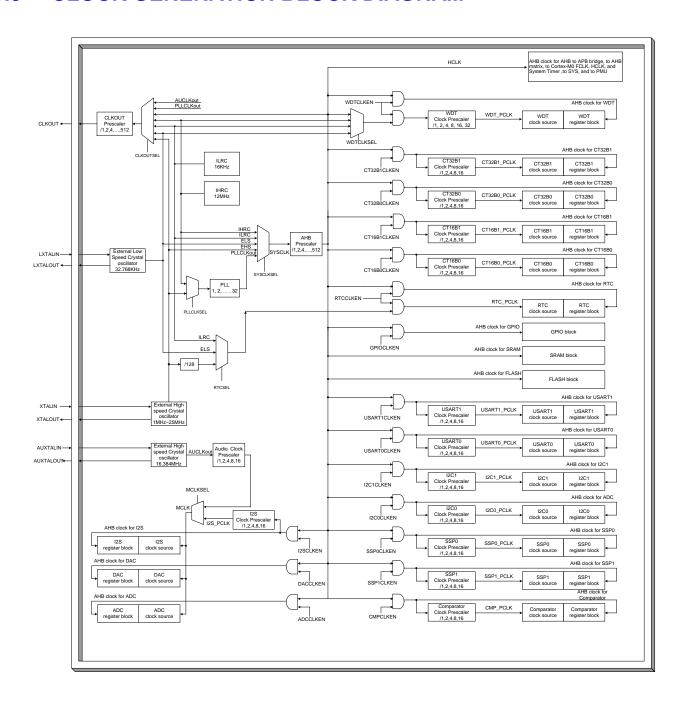

# 1.3 CLOCK GENERATION BLOCK DIAGRAM

# 1.4 PIN ASSIGNMENT

| N32F109F (LQFP 80 pins) |    |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             |    |                |

|-------------------------|----|----------|----------|------------------------|------------------------|------------------|----------|-----------------------|-----------------------|-----------------------|-----------|-------------|-----------|-----------|-----------|--------------|-------------|--------------|--------------|------------|-------------|----|----------------|

|                         |    | VDD      | VSS      | P3.15/SDA1/CT32B1_CAP0 | P3.14/SCL1/CT32B0_CAP0 | P3.9/CT16B0_PWM0 | P3.8/CMO | P3.7/CM23/CT32B1_PWM1 | P3.6/CM22/CT32B0_PWM1 | P3.5/CM21/CT16B1_PWM0 | P3.4/CM20 | P3.3/CM19   | P3.2/CM18 | P3.1/CM17 | P3.0/CM16 | P2.15/CM15   | P2.14/CM14  | P2.13/CM13   | P2.12/CM12   | VSS        | VDD         |    |                |

|                         |    | 80       | 79       | 78                     | 77                     | 76               | 75       | 74                    | 73                    | 72                    | 71        | 70          | 69        | 68        | 67        | 66           | 65          | 64           | 63           | 62         | 61          |    |                |

| P3.10/CT32B0_PWM0       | 1  | •        |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 60 | P2.11/CM11     |

| P3.11/CT32B1_PWM0       | 2  |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 59 | P2.10/CM10     |

| P3.12/URXD1/CT16B0_CAP0 | 3  |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 58 | P2.9/CM9       |

| P3.13/UTXD1/CT16B1_CAP0 | 4  |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 57 | P2.8/CM8       |

| P0.0/URXD0              | 5  |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 56 | P2.7/CM7       |

| P0.1/UTXD0              | 6  |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 55 | P2.6/CM6       |

| P0.2/SCL0               | 7  |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 54 | P2.5/CM5       |

| P0.3/SDA0               | 8  |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 53 | P2.4/CM4       |

| P0.4/SCK0/PGDCLK        | 9  |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 52 | P2.3/CM3       |

| P0.5/SEL0/PGDIN         | 10 |          |          |                        |                        |                  |          |                       |                       | e Ni                  | 321       | <b>-</b> 46 | )OE       |           |           |              |             |              |              |            |             | 51 | P2.2/CM2       |

| P0.6/MISO0/OTPCLK       | 11 |          |          |                        |                        |                  |          |                       | '                     | SIN                   | 321       | - 10        | ЭГ        |           |           |              |             |              |              |            |             | 50 | P2.1/CM1       |

| P0.7/MOSI0/VR_DOUT      | 12 |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 49 | P2.0/CM0       |

| P0.8/SCK1               | 13 |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 48 | P1.13/XTALOUT  |

| P0.9/SEL1               | 14 |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 47 | P1.12/XTALIN   |

| P0.10/MISO1             | 15 |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 46 | P1.1/AUXTALIN  |

| P0.11/MOSI1             | 16 |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 45 | P1.0/AUXTALOUT |

| P0.12/SWCLK             | 17 |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 44 | P1.11/LXTALOUT |

| P0.13/SWDIO             | 18 |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 43 | P1.10/LXTALIN  |

| P0.14/DPDWAKEUP         | 19 |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 42 | vss            |

| P0.15/RESET             | 20 |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             | 41 | VDD            |

|                         |    | 21       | 22       | 23                     | 24                     | 25               | 26       | 27                    | 28                    | 29                    | 30        | 31          | 32        | 33        | 34        | 35           | 36          | 37           | 38           | 39         | 40          |    |                |

|                         |    |          |          |                        |                        |                  |          |                       | Ъ                     |                       | _         |             |           |           |           |              | _           | _            | _            | _          | _           |    |                |

|                         |    | A_       | 回        | A_                     | 5                      | MC               | A_       | ٥                     | VOUTP                 | VOUTN                 | ۵         |             |           | ٥         | ٥         | S<br>S       | SD          | 8            | BC           | 2SV        | Š           |    |                |

|                         |    | VMID_ADC | MIC_BIAS | AVDD_ADC               | P1.8/MIC_N             | P1.7/MIC_P       | AVSS_ADC | AVDD_DRV              | >                     | >                     | AVSS_DRV  | AVDD_DAC    | VMID_DAC  | VCOM_DAC  | AVSS_DAC  | //28         | P1.3/12SDIN | /I2S         | //28         | P1.6/12SWS | 2<br>Z      |    |                |

|                         |    | >        |          | Ā                      | ŗ                      | Ф                | ⋖        | Á                     |                       |                       | ⋖         | Ā           | _         | ×         | ⋖         | P1.2/I2SMCLK | 7           | P1.4/I2SDOUT | P1.5/12SBCLK | ŗ          | P1.9/CLKOUT |    |                |

|                         |    |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           | "            |             | п.           | _            |            | _           |    |                |

|                         |    |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             |    |                |

|                         |    |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             |    |                |

|                         |    |          |          |                        |                        |                  |          |                       |                       |                       |           |             |           |           |           |              |             |              |              |            |             |    |                |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| P3.10/CT32B0_PWM0 1 •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| P3.11/CT32B1_PWM0 P3.12/URXD1/CT16B0_CAP0 P3.13/UTXD1/CT16B1_CAP0 P0.0/URXD0 P0.0/URXD0 P0.1/UTXD0 P0.3/SDA0 P0.4/SCK0/PGDCLK P0.5/SEL0/PGDIN P0.6/MISO0/OTPCLK P0.7/MOSI0/NR_DOUT P0.12/SWCLK P0.13/SWDIO P0.13/SWDIO P0.14/DPDWAKEUP P0.15/RESET P0.15/RESET P0.15/RESET P0.15/CM5 P2.6/CM6 P2.6/ |      |

| P3.12/URXD1/CT16B0_CAP0   3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| P3.13/UTXD1/CT16B1_CAP0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| P0.0/URXD0 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| P0.1/UTXD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

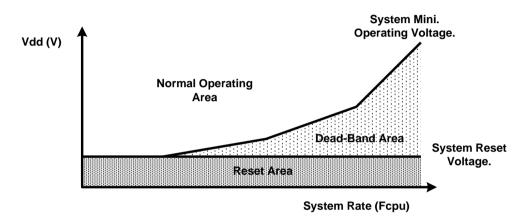

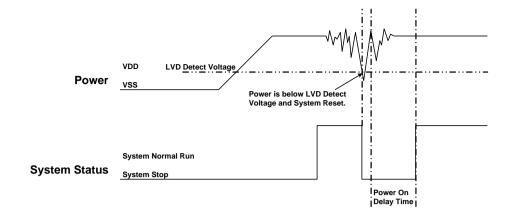

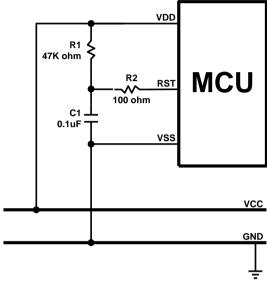

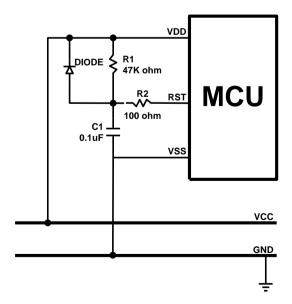

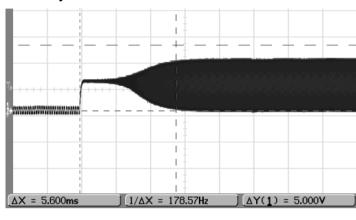

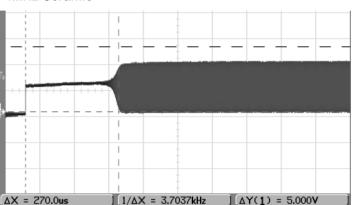

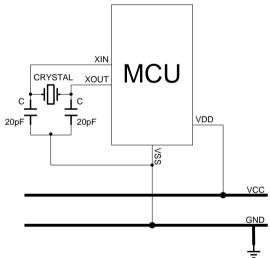

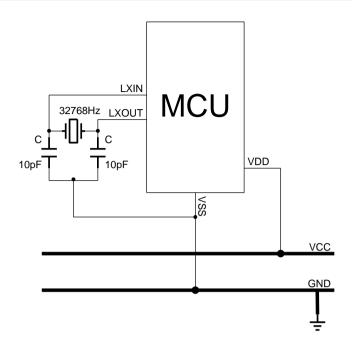

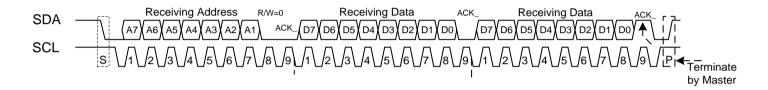

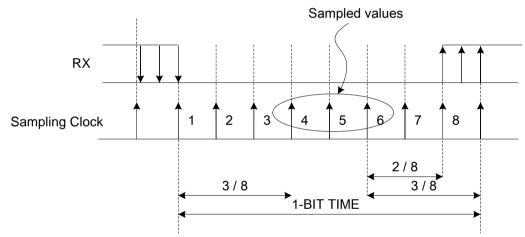

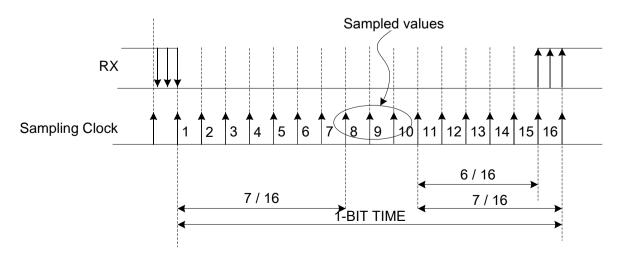

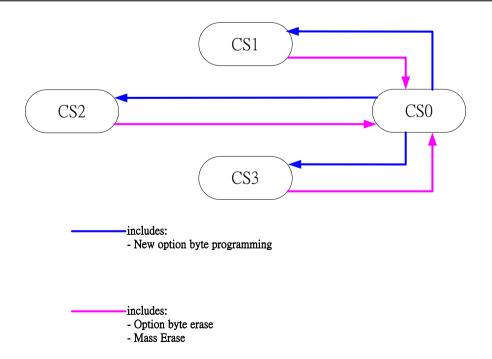

| P0.2/SCL0 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |