## **Stepping Motor Driver IC**

IK6502

#### **General Description**

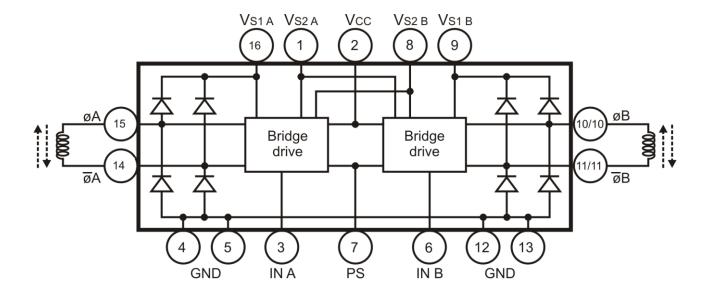

IK6502 is stepping motor driver ICs with MOS output transistors.

The ICs can control two-phase stepping motor forward and reverse by bipolar driving. They have a power-saving circuit and a standby circuit.

#### **Features**

- They are similar substituting products of TB6674.

Both products have same packages and same pin assignments.

- One-chip two-phase bipolar stepping motor driver (including two bridge drivers)

- Power saving operation is available

- Standby operation is available Current consumption ≤ 20 μA (typ.)

- Built-in punch-through current restriction circuit for system reliability and noise suppression

- $\bullet$  TTL-compatible inputs INA, INB, PS, and  $V_{\text{S2B}}$  terminals

- ON resistance PS = L:  $3.0 \Omega$  (Typ.) PS = H:  $8.5 \Omega$  (Typ.)

- · High driving ability

- : Io (START) 350 mA (MAX.): V<sub>S1</sub> ENABLE

- : Io (HOLD) 100 mA (MAX.): V<sub>S2</sub> ENABLE

- Typical PKG SOP16 & DIP16

- GND terminal = HEAT SINK

- Over current shutdown circuit (ISD)

- Thermal shutdown circuit (TSD)

- Under voltage lockout circuit (UVLO)

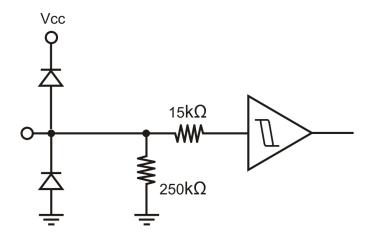

- Pull-down resistance for input terminal (250 kΩ)

# **Block Diagram**

# **Pin Description**

| Pin | No.               | Symbol                                                                  |

|-----|-------------------|-------------------------------------------------------------------------|

| 1   | V <sub>S2A</sub>  | Low-voltage power supply terminal                                       |

| 2   | V <sub>CC</sub>   | Power voltage supply terminal for control                               |

| 3   | IN A              | A-ch forward rotation / reverse rotation signal terminal, Truth Table 1 |

| 4   | GND               | GND terminal                                                            |

| 5   | GND               | GND terminal                                                            |

| 6   | IN B              | B-ch forward rotation / reverse rotation signal terminal, Truth Table 1 |

| 7   | PS                | Power saving signal input terminal                                      |

| 8   | V <sub>S2B</sub>  | Standby signal input terminal, Truth Table 2                            |

| 9   | V <sub>S1B</sub>  | High-voltage power supply terminal                                      |

| 10  | φВ                | Output B                                                                |

| 11  | ФВ                | Output B                                                                |

| 12  | GND               | GND terminal                                                            |

| 13  | GND               | GND terminal                                                            |

| 14  | ΦĀ                | Output A                                                                |

| 15  | φА                | Output A                                                                |

| 16  | V <sub>S1 A</sub> | High-voltage power supply terminal                                      |

#### **Truth Table 1**

| Inj | Input |   | Output                                  |  |  |

|-----|-------|---|-----------------------------------------|--|--|

| PS  | IN    | φ | Φ_                                      |  |  |

| L   | L     | L | H ENABLE V <sub>S1</sub>                |  |  |

| L   | Н     | Н | L ENABLE V <sub>S1</sub>                |  |  |

| Н   | L     | L | H ENABLE V <sub>S2</sub> (Power saving) |  |  |

| Н   | Н     | Н | L ENABLE V <sub>S2</sub> (Power saving) |  |  |

### **Truth Table 2**

| V <sub>S2B</sub> | Mode                     |  |  |  |  |

|------------------|--------------------------|--|--|--|--|

| L                | POWER OFF (Standby mode) |  |  |  |  |

| Н                | OPERATION                |  |  |  |  |

Note: Apply 5V to  $V_{\text{S2A}}$  as a supply terminal.

#### **Terminal circuit**

Input terminal (INA, INB, PS, and  $V_{\text{S2B}}$ )

The diagram is partly-provided and omitted or simplified for explanatory purposes.

#### **Absolute Maximum Ratings (Ta = 25°C)**

| Characteristic    |                       | Symbol                 | Rating                | Unit |

|-------------------|-----------------------|------------------------|-----------------------|------|

|                   |                       | V <sub>cc</sub>        | 6.0                   |      |

| Supply voltage    |                       | V <sub>S1</sub>        | 24.0                  | V    |

|                   |                       | $V_{S2}$               | Up to V <sub>CC</sub> |      |

|                   |                       | I <sub>O (PEAK)</sub>  | ±400                  |      |

| Output current    | IK6502D/N             | I <sub>O (START)</sub> | ±350                  | mA   |

| odirone           |                       | I <sub>O (HOLD)</sub>  | ±100                  |      |

| Input voltage     |                       | $V_{IN}$               | Up to V <sub>CC</sub> | V    |

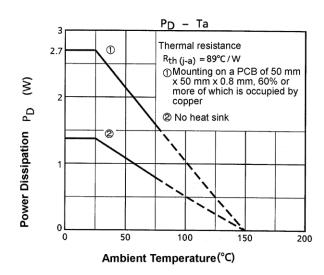

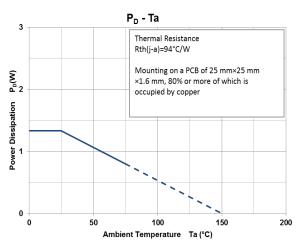

| D                 | IK6502N               |                        | 1.4 (Note 1)          |      |

| Power dissipation |                       | $P_{D}$                | 2.7 (Note 2)          | W    |

| dissipation       | IK6502D               |                        | 1.33 (Note 2)         |      |

| Operating temp    | Operating temperature |                        | -30 to 75             | °C   |

| Storage tempe     | rature                | Tstg                   | -55 to 150            | °C   |

Note 1: IC only

Note 2: This value is obtained if mounting is on a 50 mm  $\times$  50 mm  $\times$  0.8 mm PCB, 60 % or more of which is occupied by copper.

### **Operating Conditions (Ta = 25°C)**

| Characteristic                    | :     | Symbol          | Min. | Тур. | Max.            | Unit |

|-----------------------------------|-------|-----------------|------|------|-----------------|------|

|                                   |       | VCC             | 4.5  | -    | 5.5             |      |

| Supply voltage                    |       | V <sub>S1</sub> | 8.0  | -    | 22.0            | V    |

|                                   |       |                 | 2.7  | -    | 5.5             |      |

| Output IK6502N                    |       | Io              | -    | -    | ±350            | mA   |

| Input voltage                     |       | V <sub>IN</sub> | 0    | -    | V <sub>CC</sub> | V    |

| Maximum frequency of input pulse  |       | f <sub>IN</sub> | -    | -    | 25              | kHz  |

| Minimum resolution of input pulse | ution | tw              | 20   | -    | -               | μs   |

Value of ON resistance tends to increase when the difference between  $V_{\text{S1}}$  and  $V_{\text{S2A}}$  becomes 5 V or less.

#### **Electrical Characteristics**

Unless otherwise specified, Ta = 25°C,  $V_{CC}$  = 5 V,  $V_{S1}$  = 12 V, and  $V_{S2A}$  = 5 V

| Charact                   | eristic            | Symbol              | Test<br>Cir-<br>cuit | Test Condition                                                            |                         | Min  | Тур. | Max | Unit |  |

|---------------------------|--------------------|---------------------|----------------------|---------------------------------------------------------------------------|-------------------------|------|------|-----|------|--|

|                           |                    | I <sub>CC1</sub>    |                      | PS: H, V <sub>S2B</sub> : H                                               |                         |      | 3    | 5   | mA   |  |

| Supply curr               | ent                | I <sub>CC2</sub>    | 1                    | PS: L, V <sub>S2B</sub> : H                                               |                         |      | 3    | 5   | IIIA |  |

|                           |                    | I <sub>CC3</sub>    |                      | V <sub>S2B</sub> : L                                                      |                         |      | 1    | 20  | μΑ   |  |

| Input                     | High               | V <sub>IN H</sub>   |                      |                                                                           |                         | 2.0  |      | Vcc | V    |  |

| voltage                   | Low                | V <sub>IN L</sub>   |                      | INA, INB, PS, V                                                           | S2B                     | -0.2 |      | 0.8 |      |  |

| Input hyster voltage*     | esis               | V <sub>IN</sub> hys | 1                    |                                                                           |                         |      | 90   |     | mV   |  |

| Input ourror              |                    |                     | 1                    | INA, INB, PS, $V_{S2B}$ $V_{IN}$ = 5.0 V<br>Built in pull-down resistance |                         | 5    | 20   | 38  | μΑ   |  |

| Input currer              | IL                 | I <sub>IN (L)</sub> | 1                    | V <sub>IN</sub> = 0 V                                                     |                         |      |      | 1   | μΑ   |  |

| Output                    |                    | Ron <sub>1H</sub>   | 2                    | PS: L, V <sub>S2B</sub> : H                                               | I <sub>OUT</sub> =400mA |      | 3    | 5   |      |  |

| ON resistance             | IK6502N<br>IK6502D | Ron <sub>2H</sub>   | 3                    | PS: H, V <sub>S2B</sub> : H                                               | I <sub>OUT</sub> =100mA |      | 8.5  | 16  | Ω    |  |

| (Note)                    |                    | Ron <sub>L</sub>    | 2                    | V <sub>S2B</sub> : H                                                      | I <sub>OUT</sub> =400mA |      | 0.9  | 3.5 |      |  |

| Diode forwa               | ard                | V <sub>FU</sub>     |                      |                                                                           |                         |      | 1.2  | 2.5 | V    |  |

| voltage                   |                    | V <sub>FL</sub>     | 4                    | I <sub>F</sub> = 350 mA, PS                                               | = L                     |      | 1.0  | 2.2 | V    |  |

| Delevitime                |                    |                     |                      | INI a                                                                     |                         |      | 0.5  |     |      |  |

| Delay time                |                    | tp <sub>HL</sub>    |                      | IN - φ                                                                    |                         |      | 0.5  |     | μs   |  |

| Thermal shutdown circuit* |                    | TSD                 |                      | (Design target o                                                          | nly)                    |      | 160  |     | °C   |  |

| TSD hyster                | esis *             | TSDhys              |                      | (Design target o                                                          | nly)                    |      | 20   |     | °C   |  |

<sup>\* :</sup> IK Semicon does not implement testing before shipping.

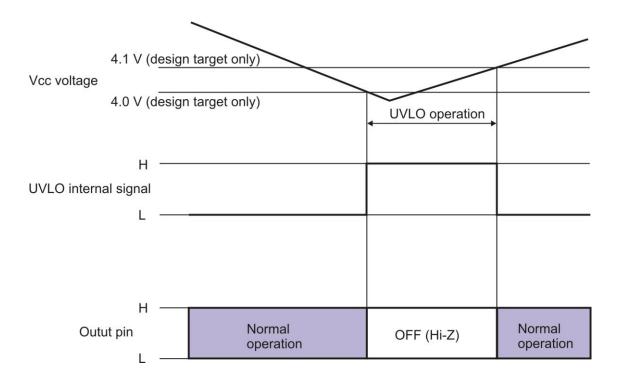

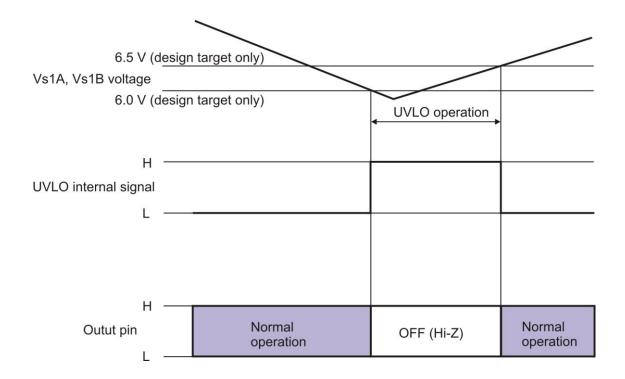

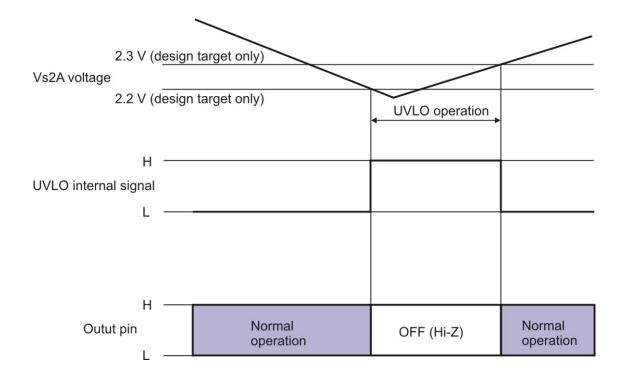

#### **Under voltage Lockout Circuit (UVLO)**

The IK6502 incorporates an under voltage lockout circuit. Outputs are turned off (Hi-Z) under the conditions as follows;

$V_{CC} \le 4.0 \text{ V (Design target)}$  or  $V_{S1A} \le 6.0 \text{ V (Design target)}$  and  $V_{S1B} \le 6.0 \text{ V (Design target)}$  or  $V_{S2A} \le 2.2 \text{ V (Design target)}$

The UVLO circuit has a hysteresis and the function recovers under the conditions as follows;

$V_{CC} = 4.1 \text{ V}$  (Design target),  $V_{S1A/VS1B} = 6.5 \text{ V}$  (Design target),  $V_{S2A} = 2.3 \text{ V}$  (Design target)

### **UVLO** operation

#### **UVLO** operation

### **UVLO** operation

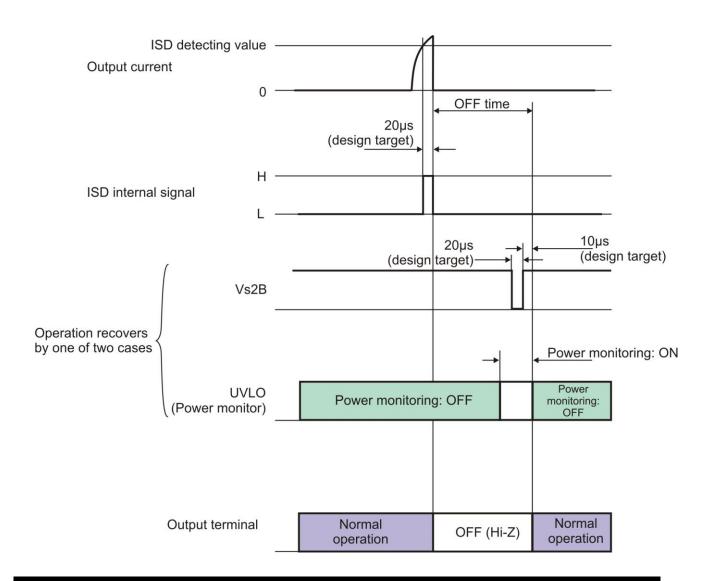

#### **Over Current Protection (ISD) Circuit**

The IC incorporates the over current protection circuit that monitors the current flowing through each output power transistor. If a current, which is out of the detecting current, is sensed at any one of these transistors, all output transistors are turned off (Hi-Z). (However, ISD is not incorporated in upper PchDMOS when PS is high level ( $V_{S2A}$  is 5V usage) because ON resistance is large.

Masking time is 20  $\mu$ s. The operation does not recover automatically (latch method). There are two recovery methods written below.

- (1) Power monitor turns on when any of the power supply decreases and reaches the specified voltage.

- (2)  $V_{S2B}$  is set low level for 20  $\mu s$  or more and then set high. The operation recovers in 10  $\mu s$ .

Reference design target of detecting current is as follows;

$PS = L, V_{S1A} (12 V) : PchDMOS = 0.8 A$

PS = H/PS = L in common: Lower NchDMOS = 1.1 A

Please reduce the external noise to prevent malfunction for ISD.

#### ISD operation

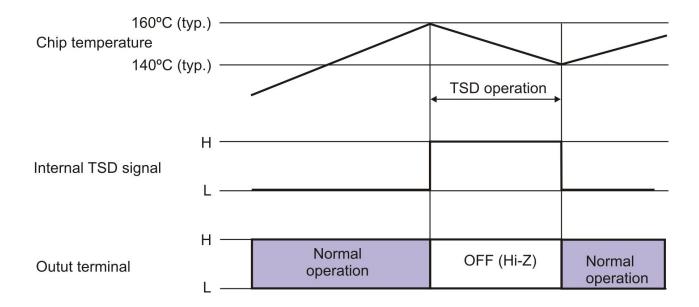

#### **Thermal Shutdown Circuit (TSD)**

The IK6502 incorporates a thermal shutdown circuit. If the junction temperature (Tj) exceeds 160°C (design target only), all the outputs are tuned off (Hi-Z).

It recovers automatically at 140°C. It has a hysteresis width of 20°C.

TSD = 160°C (design target only)

TSD operation

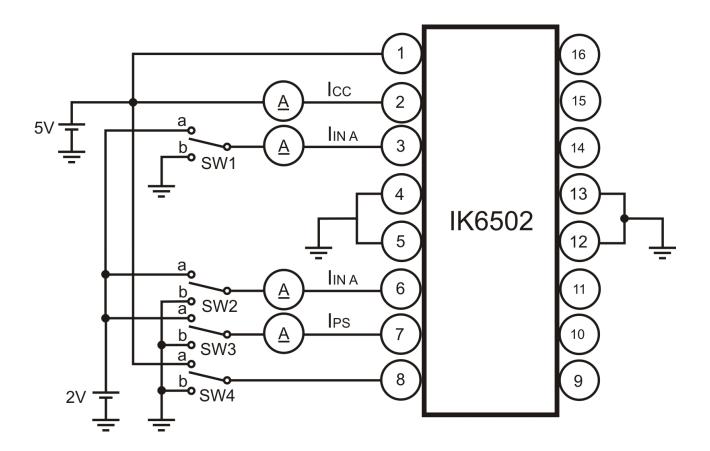

Test Circuit 1.  $I_{CC1}$ ,  $I_{CC2}$ ,  $I_{CC3}$ ,  $I_{IN\,A}$ ,  $I_{IN\,B}$ , and  $I_{PS}$

| Item              | SW <sub>1</sub> | SW <sub>2</sub> | SW <sub>3</sub> | SW <sub>4</sub> |

|-------------------|-----------------|-----------------|-----------------|-----------------|

| I <sub>CC1</sub>  | b               | b               | а               | а               |

| I <sub>CC2</sub>  | b               | b               | b               | а               |

| I <sub>CC3</sub>  | b               | b               | _               | b               |

| I <sub>IN A</sub> | а               | _               | _               | а               |

| I <sub>IN B</sub> | _               | а               | _               | а               |

| I <sub>PS</sub>   | _               | _               | а               | а               |

All terminals of INA, INB, and PS should output low or be connected to the ground terminal in measuring  $I_{\text{CC3}}. \label{eq:loss}$

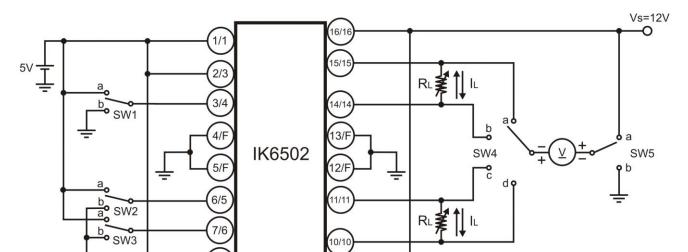

### Test Circuit 2. Ron 1H1, Ron 1H2, Ron L2, and Ron L3

8/8

<sup>\*:</sup> Adjust  $R_L$  to correspond to  $I_L$ .

| Item                 | SW <sub>1</sub> | SW <sub>2</sub> | SW <sub>3</sub> | SW <sub>4</sub> | SW <sub>5</sub> | I <sub>L</sub> (mA) |

|----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------------|

|                      | а               | _               |                 | а               |                 |                     |

| M                    | b               | _               | b               | b               | 0               | 100                 |

| V <sub>SAT 1H1</sub> | _               | а               | D               | d               | а               | 100                 |

|                      | _               | b               |                 | С               |                 |                     |

|                      | а               |                 |                 | а               |                 |                     |

| V                    | b               |                 | b               | b               | а               | 400                 |

| V <sub>SAT 1H2</sub> | _               | а               |                 | d               |                 |                     |

|                      | _               | b               |                 | С               |                 |                     |

|                      | а               |                 |                 | b               | b               | 100                 |

| V <sub>SAT L2</sub>  | b               | _               |                 | а               |                 |                     |

| V SAT L2             | _               | а               | _               | d               |                 |                     |

|                      | _               | b               |                 | С               |                 |                     |

|                      | а               | _               |                 | b               |                 | 400                 |

| V <sub>SAT L3</sub>  | b               | _               | b               | а               | b               |                     |

|                      | _               | a               | l D             | d               |                 | 400                 |

|                      |                 | b               |                 | С               |                 |                     |

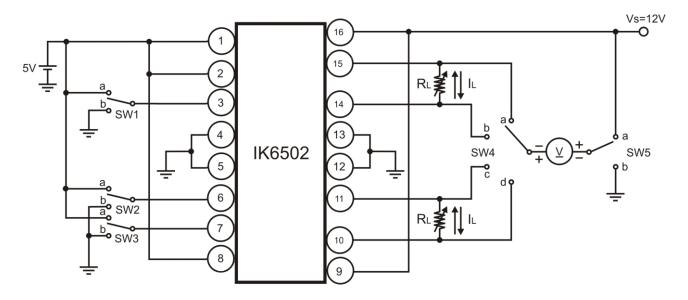

# Test Circuit 3. Ron $_{2\text{H1}},$ Ron $_{2\text{H2}},$ and Ron $_{L1}$

\*: Adjust  $R_L$  to correspond to  $I_L$ .

| Item                 | SW <sub>1</sub> | SW <sub>2</sub> | SW <sub>3</sub> | SW <sub>4</sub> | SW <sub>5</sub> | I∟ (mA) |

|----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------|

|                      | а               | _               |                 | а               |                 |         |

| V                    | b               | _               |                 | b               |                 | 20      |

| $V_{SAT2H1}$         | _               | а               | а               | d               | а               | 20      |

|                      | _               | b               |                 | С               |                 |         |

|                      | а               | _               | a               | а               | a               | 100     |

| V                    | b               | _               |                 | b               |                 |         |

| V <sub>SAT 2H2</sub> | _               | а               |                 | d               |                 |         |

|                      | _               | b               |                 | С               |                 |         |

|                      | а               | _               |                 | b               |                 |         |

| V <sub>SAT L1</sub>  | b               | _               |                 | а               | b               | 20      |

|                      |                 | а               | а               | С               |                 | 20      |

|                      | _               | b               |                 | d               |                 |         |

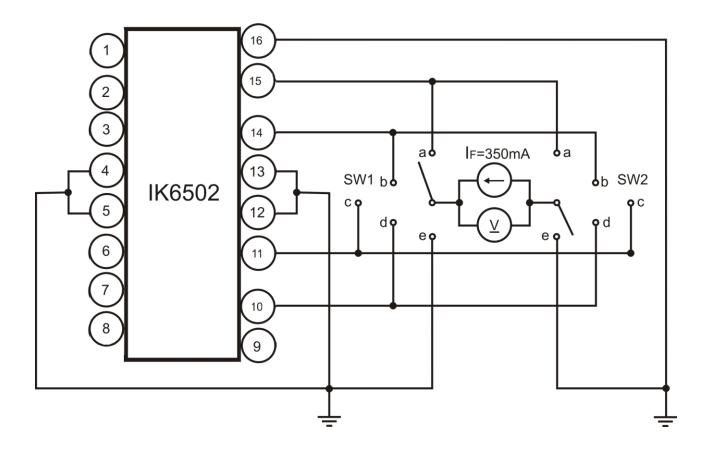

# Test Circuit 4. $V_{\text{FU}}$ , and $V_{\text{FL}}$

### **Measuring Method**

| Item     | SW <sub>1</sub> | SW <sub>2</sub> |

|----------|-----------------|-----------------|

|          | а               |                 |

| $V_{FU}$ | b               | е               |

|          | С               |                 |

|          | d               |                 |

|          |                 | а               |

| $V_{FL}$ | е               | b               |

|          |                 | С               |

|          |                 | d               |

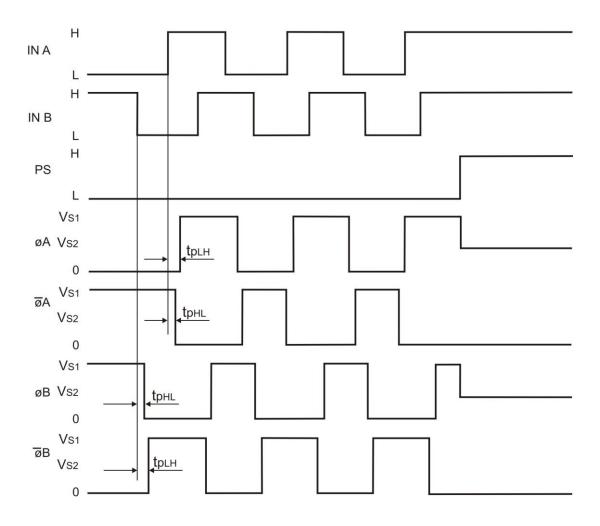

### **Timing Chart (two-phase excitation)**

#### **Thermal Performance Characteristics**

### IK6502N (DIP-16)

### IK6502D (SOP-16)

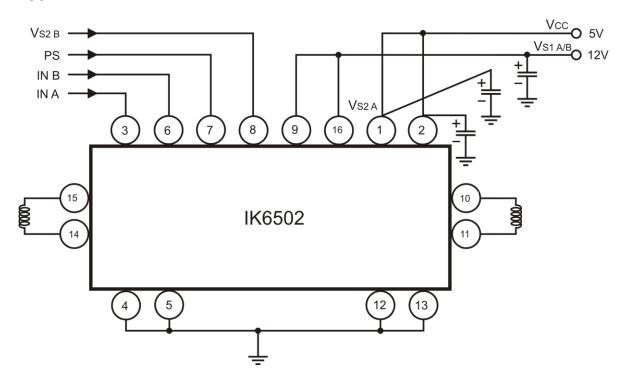

#### **Application Circuit**

Note 1: Connect the V<sub>S2A</sub> terminal to the lower supply voltage (5 V).

Note 2: Supply smoothing capacitor\* should be connected between each supply terminal (Vcc,  $V_{S2A}$ , and  $V_{S1A/B}$ ) and GND terminal.

\*: (Ex.): Capacitors of tens of µF and 0.1 µF which are connected in parallel.

Note 3: Utmost care is necessary in the design of the output, Vcc,  $V_M$ , and GND lines since the IC may be destroyed by short-circuiting between outputs, air contamination faults, or faults due to improper grounding, or by short-circuiting between contiguous terminals.

Note 4: By our short-circuited examination of neighboring terminals, when 9 and 10 terminals or 15 and 16 terminals are short-circuited, in any case might to be destroyed and cause the trouble of smoking etc. Please use an appropriate fuse to the power supply line.

Note 5: Connect  $V_{S1A}$  terminal and  $V_{S1B}$  terminal externally.

Note 6: Connect each GND terminal externally.

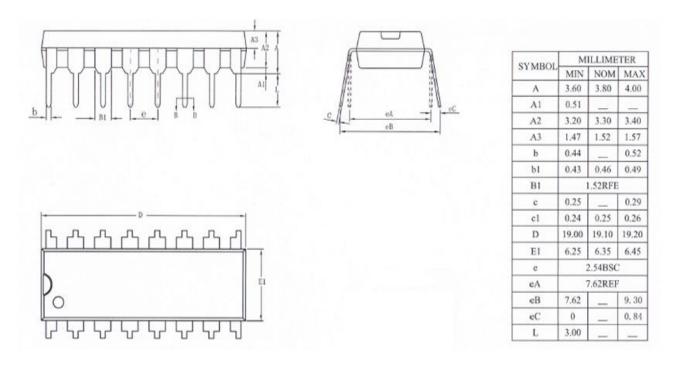

### **Package Dimensions**

### **IK6502N DIP (Dual Line Package)**

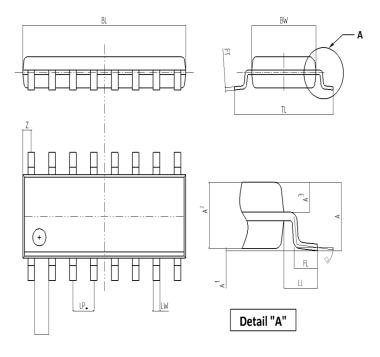

# IK6502D SOP (Small Outline Package)

| SYMBOL   |       | Dimension (mm) |        |

|----------|-------|----------------|--------|

| STIVIDOL | Min   | Тур            | Max    |

| BL       | 9.800 |                | 10.000 |

| BW       | 3.800 |                | 4.000  |

| FT       | 0.195 |                | 0.211  |

| TL       | 5.900 |                | 6.100  |

| LP       | 1.245 |                | 1.295  |

| LW       | 0.375 |                | 0.425  |

| A        |       |                | 1.750  |

| A1       | 0.050 |                | 0.250  |

| A2       | 1.350 |                | 1.550  |

| A3       |       | 0.623          |        |

| Ц        |       | 1.050          |        |

| FL       | 0.500 |                | 0.800  |

| Θ        |       |                | 8.000  |