#### DDR2 AND DDR3/DDR3L SYNCHRONOUS BUCK CONTROLLER WITH 1.5A LDO SUPPORT LOW IQ

### Features

**Buck Controller (VDDQ)**

- High Input Voltages Range from 3V to 28V Input Power

- Provide Adjustable Output Voltage from 0.75V to 5.5V ±1%Accuracy over Temperature

- Integrated MOSFET Drivers and Bootstrap Forward P-CH MOSFET

- Low Quiescent Current (200μA)

- Excellent Line and Load Transient Responses

- PFM Mode for Increased Light Load Efficiency

- Constant On-Time Controller Scheme

Switching Frequency Compensation for PWM Mode

- Adjustable Switching Frequency from 400kHz to 550kHz in PWM Mode with DC Output Current

- S3 and S5 Pins Control The Device in S0, S3 or S4/ S5 State

- Power Good Monitoring

- 70% Under-Voltage Protection (UVP)

- 125% Over-Voltage Protection (OVP)

- Adjustable Current-Limit Protection

Using Sense Low-Side MOSFET's R<sub>DS(ON)</sub>

- TQFN-20 3mmx3mm Thin package

- Lead Free Available (RoHS Compliant) ±1.5A LDO Section (VTT)

- Sourcing or Sinking Current up to 1.5A

- Fast Transient Response for Output Voltage

- Output Ceramic Capacitors Support at least 10μF MLCC

- VTT and VTTREF Track at Half the VDDQSNS by internal divider

- ±20mV Accuracy for VTT and VTTREF

- Independent Over-Current Limit (OCL)

- Thermal Shutdown Protection

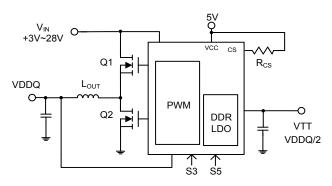

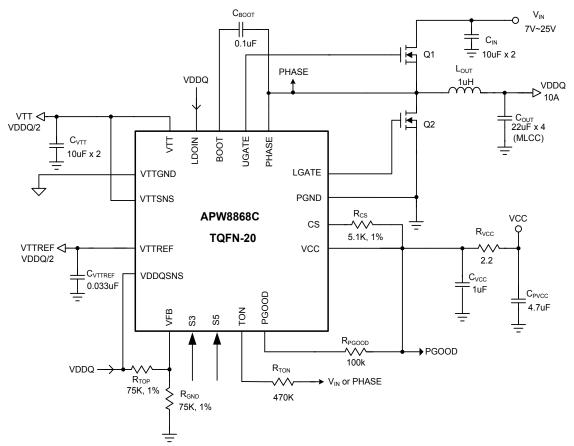

### **Simplified Application Circuit**

### **General Description**

The APW8868C integrates a synchronous buck PWM controller to generate VDDQ, a sourcing and sinking LDO linear regulator to generate VTT. It offers the lowest total solution cost in system where space is at a premium.

The APW8868C provides excellent transient response and accurate DC voltage output in either PFM or PWM Mode. In Pulse Frequency Mode (PFM), the APW8868C provides very high efficiency over light to heavy loads with loading-modulated switching frequencies. On TQFN-20 Package, the Forced PWM Mode works nearly at constant frequency for low-noise requirements.

The APW8868C is equipped with accurate current-limit, output under-voltage, and output over-voltage protections. A Power-On- Reset function monitors the voltage on VCC prevents wrong operation during power on.

The LDO is designed to provide a regulated voltage with bi-directional output current for DDR-SDRAM termination. The device integrates two power transistors to source or sink current up to 1.5A. It also incorporates current-limit and thermal shutdown protection.

The output voltage of LDO tracks the voltage at VREF pin. An internal resistor divider is used to provide a half voltage of VREF for VTTREF and VTT Voltage. The VTT output voltage is only requiring  $20\mu$ F of ceramic output capacitance for stability and fast transient response. The S3 and S5 pins provide the sleep state for VTT (S3 state) and suspend state (S4/S5 state) for device, when S5 and S3 are both pulled low the device provides the soft-off for VTT and VTTREF.

### Applications

- DDR2, and DDR3/DDR3L MemoryPower Supplies

- SSTL-2 SSTL-18 and HSTL Termination

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

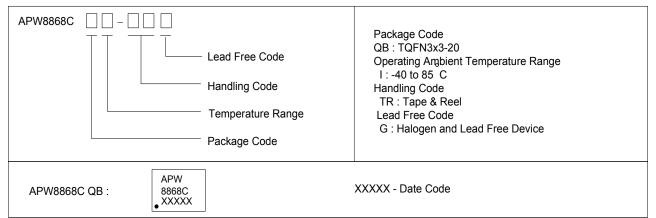

## **Ordering and Marking Information**

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or CI does not exceed 900ppm by weight in homogeneous material and total of Br and CI does not exceed 1500ppm by weight).

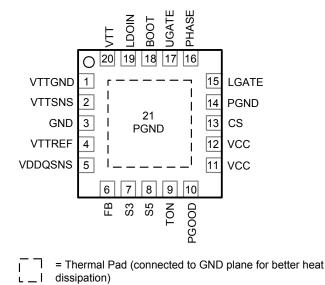

## **Pin Configuration**

### Absolute Maximum Ratings (Note 1.2)

| Symbol                | Parameter                                                                        | Rating                                                       | Unit |

|-----------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------|------|

| V <sub>cc</sub>       | VCC Supply Voltage (VCC to GND)                                                  | -0.3 ~ 7                                                     | V    |

| V <sub>BOOT</sub>     | BOOT Supply Voltage (BOOT to PHASE)                                              | -0.3 ~ 7                                                     | V    |

| V <sub>BOOT-GND</sub> | BOOT Supply Voltage (BOOT to GND)                                                | -0.3 ~ 35                                                    | V    |

|                       | UGATE Voltage (UGATE to PHASE)<br><400ns pulse width<br>>400ns pulse width       | -5 ~ V <sub>BOOT</sub> +0.3<br>-0.3 ~ V <sub>BOOT</sub> +0.3 | V    |

|                       | LGATE Voltage (LGATE to GND)<br><400ns pulse width<br>>400ns pulse width         | -5 ~ VCC+0.3<br>-0.3 ~ VCC+0.3                               | V    |

|                       | PHASE Voltage (PHASE to GND)<br><400ns pulse width<br>>400ns pulse width         | -5 ~ 35<br>-0.3 ~ 28                                         | v    |

|                       | PGND, VTTGND and CS_GND to GND Voltage                                           | -0.3 ~ 0.3                                                   | V    |

|                       | All Other Pins (CS,S3, S5, VTTSNS, VDDQSNS, VLDOIN, VFB, PGOOD, VTT, VTTREF GND) | -0.3 ~ 7                                                     | V    |

| Tj                    | Maximum Junction Temperature                                                     | 150                                                          | °C   |

| T <sub>STG</sub>      | Storage Temperature                                                              | -65 ~ 150                                                    | °C   |

|                       | Maximum Soldering Temperature, 10 Seconds                                        | 260                                                          | °C   |

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability Note 2: The device is ESD sensitive. Handling precautions are recommended.

### Thermal Characteristics (Note 3)

| Symbol          | Parameter                               | Typical Value | Unit |

|-----------------|-----------------------------------------|---------------|------|

| $\theta_{JA}$   | Thermal Resistance -Junction to Ambient | 50            | °C/W |

| θ <sub>JC</sub> | Thermal Resistance -Junction to Case    | 8             | °C/W |

Note 3:  $\theta_{JA}$  and  $\theta_{JC}$  are measured with the component mounted on a high effective the thermal conductivity test board in free air. The exposed pad of package is soldered directly on the PCB

### Recommended Operating Conditions (Note 4)

| Symbol              | Parameter                 | Range        | Unit |

|---------------------|---------------------------|--------------|------|

| $V_{\rm cc}$        | VCC Supply Voltage        | 4.5 ~ 5.5    | V    |

| $V_{\rm IN}$        | Converter Input Voltage   | 3 ~ 28       | V    |

| V <sub>VDDQ</sub>   | Converter Output Voltage  | 0.75 ~5.5V   | V    |

| V <sub>VTT</sub>    | LDO Output Voltage        | 0.375 ~ 2.75 | V    |

| I <sub>OUT</sub>    | Converter Output Current  | 0 ~ 15       | A    |

| I <sub>VTT</sub>    | LDO Output Current        | -1.5 ~ +1.5  | A    |

| C <sub>VCC</sub>    | VCC Capacitance           | 1~           | μF   |

| C <sub>VTT</sub>    | VTT Output Capacitance    | 10~100       | μF   |

| C <sub>VTTREF</sub> | VTTREF Output Capacitance | 0.01~0.1     | μF   |

| T <sub>A</sub>      | Ambient Temperature       | -40 ~ 85     | °C   |

| TJ                  | Junction Temperature      | -40 ~ 125    | °C   |

Note 4: Refer to the typical application circuit.

| Symbol              | Demonster              | Task Qanaditiana                                                              |      | Unit  |     |      |  |

|---------------------|------------------------|-------------------------------------------------------------------------------|------|-------|-----|------|--|

| Symbol              |                        |                                                                               | Min  | Тур   | Max | Unit |  |

| SUPPLY              | CURRENT                |                                                                               |      |       |     |      |  |

| I <sub>vcc</sub>    | VCC Supply Current     | $T_A = 25^{\circ}C$ , $V_{S3} = V_{S5} = 5V$ , no load, VCC Current           | -    | 180   | 220 | μA   |  |

| IVCCSTB             | VCC Standby Current    | $T_A = 25^{\circ}C$ , $V_{S3} = 0V$ , $V_{S5} = 5V$ , no load, VCC<br>Current | -    | 120   | 160 | μA   |  |

| I <sub>VCCSDN</sub> | VCC Shutdown Current   | $T_A = 25^{\circ}C, V_{S3} = V_{S5} = 0V$ , no load                           | -    | 0.1   | 1   | μA   |  |

|                     | LDOIN Supply Current   | $T_A = 25^{\circ}C, V_{S3} = V_{S5} = 5V$ , no load                           | -    | 1     | 10  |      |  |

|                     | LDOIN Standby Current  | $T_A = 25^{\circ}C, V_{S3} = 0V, V_{S5} = 5V$ , no load,                      | -    | 0.1   | 10  | μA   |  |

|                     | LDOIN Shutdown Current | $T_A = 25^{\circ}C, V_{S3} = V_{S5} = 0V$ , no load                           | -    | 0.1   | 1   |      |  |

| POWER-              | ON-RESET               |                                                                               |      |       |     |      |  |

|                     | VCC POR Threshold      | VCC Rising                                                                    | 3.95 | 4.1   | 4.4 | V    |  |

|                     | VCC POR Hysteresis     |                                                                               | -    | 0.1   | -   | V    |  |

| VTT OUT             | IPUT                   |                                                                               |      |       |     | 1    |  |

|                     |                        | $V_{LDOIN} = V_{VDDQSNS} = 1.5V$                                              | -    | 0.75  | -   |      |  |

| $V_{\text{VTT}}$    | VTT Output Voltage     | V <sub>LDOIN</sub> = V <sub>VDDQSNS</sub> = 1.35V                             | -    | 0.675 | -   | V    |  |

|                     |                        | V <sub>LDOIN</sub> = V <sub>VDDQSNS</sub> = 1.2V                              | -    | 0.6   | _   |      |  |

|                     |                        | $V_{LDOIN} = V_{VDDQSNS} = 1.5V, V_{VDDQSNS}/2 - V_{VTT,}$<br>$I_{VTT} = 0A$  | -20  | -     | 20  |      |  |

| N/                  |                        | $V_{LDOIN} = V_{VDDQSNS} = 1.5V, V_{VDDQSNS}/2 - V_{VTT,}$<br>$I_{VTT} = 1A$  | -30  | -     | 30  |      |  |

| V <sub>VTT</sub>    | VTT Output Tolerance   | $V_{LDOIN} = V_{VDDQSNS} = 1.35V, V_{VDDQSNS}/2 - V_{VTT,}$<br>$I_{VTT} = 0A$ | -20  | -     | 20  | - mV |  |

|                     |                        | $V_{LDOIN} = V_{VDDQSNS} = 1.35V, V_{VDDQSNS}/2 - V_{VTT,}$<br>$I_{VTT} = 1A$ | -30  | -     | 30  |      |  |

| Symbol              | Devementer                            | Test Conditions                                                                                                                  |                                                | AF       | Unit  |      |       |

|---------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------|-------|------|-------|

| Symbol              | Parameter                             |                                                                                                                                  |                                                | Min      | Тур   | Max  | Unit  |

| νττ ουτ             | PUT                                   |                                                                                                                                  |                                                |          |       |      |       |

|                     |                                       | $V_{LDOIN} = V_{VDDQSNS} = 1.2V$<br>$I_{VTT} = 0A$                                                                               | V, V <sub>VDDQSNS</sub> /2 - V <sub>VTT,</sub> | -20      | -     | 20   |       |

| V <sub>TT</sub>     | VTT Output Tolerance                  | $V_{LDOIN} = V_{VDDQSNS} = 1.2V$<br>$I_{VTT} = 1A$                                                                               | V, $V_{VDDQSNS}/2 - V_{VTT,}$                  | -30      | -     | 30   | mV    |

| V <sub>SSVTT</sub>  | VTT Soft Start time                   | S3 is go high to 0.95*\                                                                                                          | /TT Regulation                                 | 25       | 30    | 35   | us    |

|                     |                                       | Sourcing Current<br>(V <sub>1 DOIN</sub> =1.5V)                                                                                  | T <sub>J</sub> =25°C                           | 1.2      | 1.8   | 2.6  | Α     |

|                     |                                       | Sinking Current<br>(VIDOIN=1.5V)                                                                                                 | T <sub>J</sub> =25°C                           | -1.3     | -1.8  | -2.6 |       |

| I <sub>LIM</sub>    | Current-Limit                         | Sourcing Current<br>(V <sub>LDOIN</sub> =1.35V)                                                                                  | T <sub>J</sub> =25°C                           | 1.1      | 1.8   | 2.6  |       |

| ·LIM                |                                       | Sinking Current<br>(V <sub>LDOIN</sub> =1.35V)                                                                                   | T <sub>J</sub> =25°C                           | -1.2     | -1.8  | -2.6 | A     |

|                     |                                       | Sourcing Current<br>(V <sub>1DOIN</sub> =1.2V)                                                                                   | T <sub>J</sub> =25°C                           | 1        | 1.8   | 2.6  |       |

|                     |                                       | Sinking Current<br>(V <sub>I DOIN</sub> =1.2V)                                                                                   | T <sub>J</sub> =25°C                           | -1.05    | -1.8  | -2.6 |       |

| R <sub>DS(ON)</sub> | VTT Power MOSFETs R <sub>DS(ON)</sub> | Upper MOSFET                                                                                                                     |                                                | -        | 350   | 500  | mΩ    |

| DS(ON)              |                                       | Lower MOSFET                                                                                                                     |                                                | -        | 350   | 500  | 11152 |

| I <sub>vttlk</sub>  | VTT Leakage Current                   | $V_{VTT} = 1.25V, V_{S3} = 0V,$<br>$T_{A} = 25^{\circ}C$                                                                         | -1.0                                           | -        | 1.0   | μΑ   |       |

| IVTTSNSLK           | VTTSNS Leakage Current                | V <sub>VTT</sub> = 1.25V, T <sub>A</sub> = 25°C                                                                                  | )                                              | -1.00    | 0.01  | 1.00 | μA    |

| VTTREF              | OUTPUT                                |                                                                                                                                  |                                                | <b>!</b> |       |      |       |

|                     |                                       | V <sub>LDOIN</sub> = V <sub>VDDQSNS</sub> = 1.5 <sup>V</sup>                                                                     | V, V <sub>VDDQSNS</sub> /2                     | -        | 0.75  | -    |       |

| V <sub>VTTREF</sub> | VTTREF Output Voltage                 | V <sub>LDOIN</sub> = V <sub>VDDQSNS</sub> = 1.35V, V <sub>VDDQSNS</sub> /2                                                       |                                                | -        | 0.675 | -    | V     |

|                     |                                       | V <sub>LDOIN</sub> = V <sub>VDDQSNS</sub> = 1.2V, V <sub>VDDQSNS</sub> /2                                                        |                                                | -        | 0.6   | -    |       |

|                     |                                       | $-10\text{mA} < I_{\text{VTTREF}} < 10\text{mA}$                                                                                 |                                                | -20      | -     | 20   |       |

| VTTRE               | VTTREF Tolerance                      | $\frac{V_{I DOIN} = V_{VTTREF} = 1.5V}{-10mA < I_{VTTREF} < 10mA}$                                                               |                                                | -20      | -     | 20   | mV    |

|                     |                                       | $\frac{V_{LDOIN} = V_{VDDQSNS} = 1.35V}{-10mA < I_{VTTREF} < 10mA, V_{VDDQSNS}/2 - V_{VTTREF}}$ $V_{LDOIN} = V_{VDDQSNS} = 1.2V$ |                                                | -20      | -     | 20   |       |

| IVTTREF             | VTTREF Source Current                 | V <sub>VTTREF</sub> = 0V                                                                                                         |                                                | -10      | -20   | -50  | mA    |

| IVTTREF             | VTTREF Sink Current                   | V <sub>VTTREF</sub> = 1.5V                                                                                                       |                                                | 10       | 20    | 60   | mA    |

| Symbol             | Baramatar                        | Test Conditions                                                                                                 | APW8868C |      |        | Unit     |

|--------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------|----------|------|--------|----------|

| Symbol             | Parameter                        | Test Conditions                                                                                                 | Min      | Тур  | Max    | Unit     |

| VDDQ O             | UTPUT                            |                                                                                                                 |          |      |        |          |

|                    |                                  | T <sub>A</sub> = 25 °C                                                                                          | 0.745    | 0.75 | 0.757  | V        |

|                    |                                  | $T_A = -40 \text{ °C to } 85 \text{ °C}$                                                                        | 0.7425   | 0.75 | 0.7575 | V        |

| $V_{\text{VFB}}$   | VFB Regulation Voltage           | $T_A = 25 ^{\circ}C,$<br>$V_{VCC} = 4.5V$ to 5.5V, $V_{IN} = 3V$ to 28V                                         | -0.1     | -    | +0.1   | %        |

|                    |                                  | $T_A = 25 ^{\circ}C$ ,<br>Load = 0 to 10A, $V_{VCC} = 4.5V$ to 5.5V                                             | -1       | -    | +1     | %        |

|                    | VFB Input Current                | V <sub>VFB</sub> = 0.78V                                                                                        | -0.1     | -    | +0.1   | μA       |

| РШМ СС             | DNTROLLERS                       | I                                                                                                               | <u> </u> | l    | 1      | <u> </u> |

| $F_{sw}$           | Operating Frequency              | Adjustable Frequency                                                                                            | 400      | -    | 550    | KHz      |

| T <sub>ss</sub>    | Internal Soft Start Time         | S5 is High to 0.9*VOUT Regulation                                                                               | 0.77     | 1.1  | 1.4    | ms       |

| PWM CC             | ONTROLLERS                       |                                                                                                                 |          |      |        |          |

| To                 | Fast on time                     | $V_{IN}$ =19V, $V_{VDDQ}$ =1.5V, $R_{TON}$ =620k $\Omega$                                                       | 175      | 205  | 235    | ns       |

| $T_{OFF(MIN)}$     | Minimum off time                 |                                                                                                                 | -        | 300  | -      | ns       |

| $T_{ON(MIN)}$      | Slow on time                     |                                                                                                                 | 80       | 110  | 140    | ns       |

|                    | Zero-Crossing Threshold          |                                                                                                                 | -9.5     | 0.5  | 10.5   | mV       |

| VDDQ PI            | ROTECTIONS                       | l                                                                                                               |          | 1    |        | 1        |

|                    |                                  | T <sub>A</sub> = 25 °C                                                                                          | 9        | 10   | 11     | μA       |

|                    | CS Pin Sink Current              | Temperature Coefficient,                                                                                        | _        | 4500 |        | ppm/°    |

|                    |                                  | On The Basis of 25°C                                                                                            | -        | 4300 | -      |          |

|                    | OCP Comparator Offset            | $      (V_{\text{VCC}} - V_{\text{CS}}) - (V_{\text{PHASE}} - PGND), \\ V_{\text{VCC}} - V_{\text{CS}} = 60mV $ | -18      | 0    | 18     | mV       |

|                    | VDDQ Current Limit Setting Range | V <sub>VCC</sub> -V <sub>CS</sub>                                                                               | 30       | -    | 200    | mV       |

|                    | VDDQ OVP Trip Threshold          | V <sub>VDDQ</sub> Rising                                                                                        | 120      | 125  | 130    | %        |

|                    | VDDQ OVP Debounce Delay          | V <sub>FB</sub> Rising, DV=10mV                                                                                 | -        | 1.5  | -      | μs       |

|                    | VDDQ UVP Trip Threshold          | V <sub>VDDQ</sub> Falling                                                                                       | 60       | 70   | 80     | %        |

|                    | VDDQ UVP Debounce                |                                                                                                                 | -        | 10   | -      | μS       |

|                    | VLDOIN Discharge Current         | S3=S5=5V,VLDOIN=1.5V                                                                                            | 150      | 300  | -      | mA       |

| PGOOD              |                                  |                                                                                                                 |          |      |        |          |

| V <sub>PGOOD</sub> | PGOOD Threshold                  | PGOOD in from Lower (PGOOD Goes High)                                                                           | 87       | 90   | 93     | %        |

|                    |                                  | PGOOD in from Higher (PGOOD Goes High)                                                                          | 120      | 125  | 130    | %        |

| I <sub>PGOOD</sub> | PGOOD Leakage Current            | V <sub>PGOOD</sub> =5V                                                                                          | -        | 0.1  | 1.0    | μΑ       |

|                    | PGOOD Sink Current               | V <sub>PGOOD</sub> =0.5V                                                                                        | 2.5      | 7.5  | -      | mA       |

|                    | PGOOD Debounce Time              |                                                                                                                 | -        | 63   | -      | μS       |

| Т <sub>SSPOK</sub> | POK Soft Start Time              | S5 is High to POK Ready                                                                                         | 1.5      | 2    | 26     | ms       |

| Symbol             | Parameter                     | Test Conditions                                                   | APW8868C |     |     | Unit |

|--------------------|-------------------------------|-------------------------------------------------------------------|----------|-----|-----|------|

| Symbol             | Parameter                     | Test conditions                                                   | Min      | Тур | Max | Unit |

| GATE DRIV          | /ERS                          |                                                                   |          |     |     |      |

|                    | UGATE Pull-Up Resistance      | BOOT-UGATE=0.5V                                                   | -        | 5   | 7   | Ω    |

|                    | UGATE Sink Resistance         | UGATE-PHASE=0.5V                                                  | -        | 1   | 2.5 | Ω    |

|                    | LGATE Pull-Up Resistance      | PVCC-LGATE=0.5V                                                   | -        | 5   | 7   | Ω    |

|                    | LGATE Sink Resistance         | LGATE-PGND=0.5V                                                   | -        | 1   | 2.5 | Ω    |

|                    | UGATE to LGATE Dead time      | UGATE falling to LGATE rising, no load                            | -        | 20  | -   | ns   |

|                    | LGATE to UGATE Dead time      | LGATE falling to UGATE rising, no load                            | -        | 20  | -   | ns   |

| BOOTSTR            | AP DIODE                      |                                                                   | •        |     | •   |      |

|                    | Forward Voltage               | $V_{VCC} - V_{BOOT}$ , $I_F$ = 10mA, $T_A$ = 25 °C                | -        | 0.3 | 0.5 | V    |

|                    | Reverse Leakage               | $V_{BOOT}$ = 30V, $V_{PHASE}$ = 25V, $V_{VCC}$ =5V, $T_A$ = 25 °C | -        | -   | 0.5 | μA   |

| LOGIC THI          | RESHOLD                       |                                                                   | •        |     | •   |      |

| V <sub>IH</sub>    | S3, S5 High Threshold Voltage | S3, S5 Rising                                                     | 2        | -   | -   | V    |

| V <sub>IL</sub>    | S3, S5 Low Threshold Voltage  | S3, S5 Falling                                                    | -        | -   | 0.8 | V    |

| I <sub>ILEAK</sub> | Logic Input Leakage Current   | $V_{S3} = V_{S5} = 5V, T_A = 25^{\circ}C$                         | -1       | -   | 1   | μA   |

| THERMAL            | SHUTDOWN                      |                                                                   |          |     |     |      |

| TSD                | Thermal Shutdown Temperature  | T, Rising                                                         | -        | 160 | -   | °C   |

|                    | Thermal Shutdown Hysteresis   |                                                                   | -        | 25  | -   | °C   |

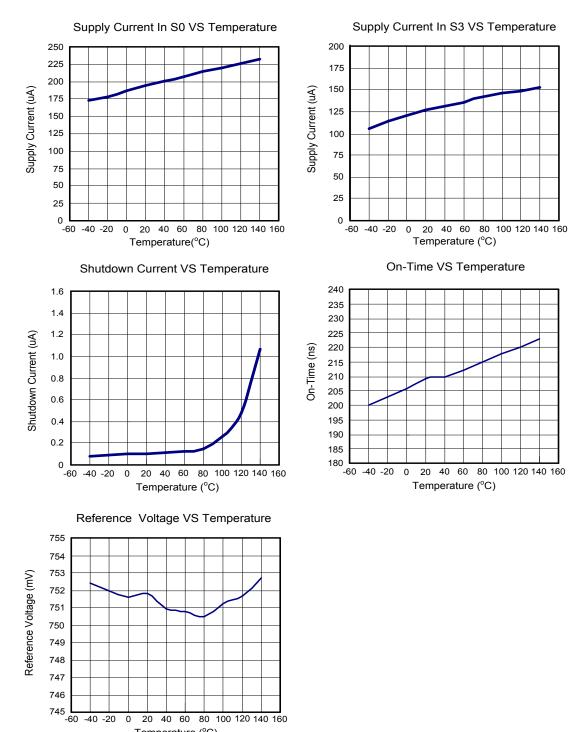

## **Typical Operating Characteristics**

0

20 40 60 80 100 120 140 160

Temperature (°C)

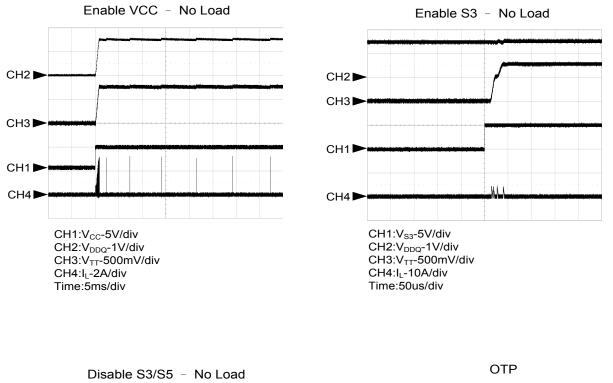

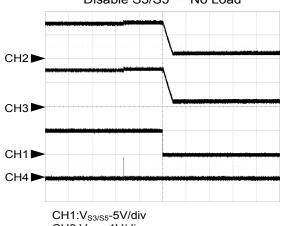

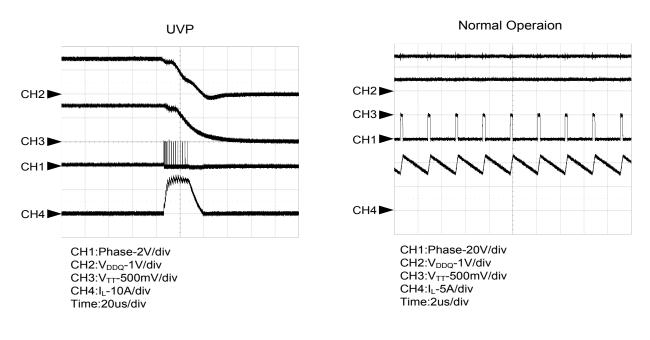

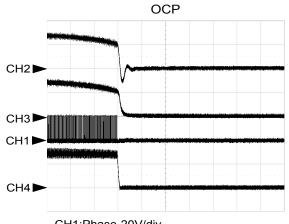

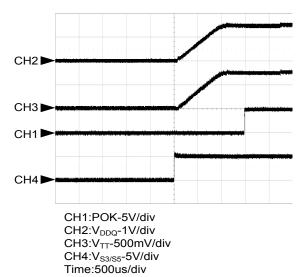

## **Operating Waveforms**

$\begin{array}{l} CH1: V_{S3/S5}\text{-}5V/div\\ CH2: V_{DDQ}\text{-}1V/div\\ CH3: V_{TT}\text{-}500mV/div\\ CH4: I_{L}\text{-}5A/div\\ Time: 1ms/div \end{array}$

CH1► CH2► CH3► CH1:V<sub>DDQ</sub>-1V/div CH1:V<sub>DDQ</sub>-1V/div CH2:V<sub>TT</sub>-500mV/div

$CH2:V_{TT}-500mV/div CH3:I_L-10A/div Time:200ms/div$

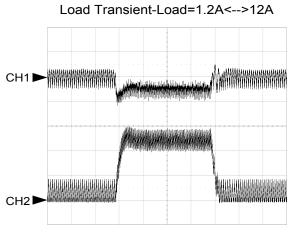

## **Operating Waveforms**

$\label{eq:chi} \begin{array}{l} CH1:Phase-20V/div\\ CH2:V_{DDQ}\text{-}1V/div\\ CH3:V_{TT}\text{-}500mV/div\\ CH4:I_L\text{-}10A/div\\ Time:100us/div \end{array}$

POK-Enable S3/S5

## **Operating Waveforms**

CH1:V<sub>DDQ</sub>-50mV/div CH2:I<sub>L</sub>-5A/div Time:50us/div

## **Pin Description**

| NO.    | NAME    | FUNCTION                                                                                                                                                                                                                                |

|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | VTTGND  | Power ground output for the VTT LDO.                                                                                                                                                                                                    |

| 2      | VTTSNS  | Voltage sense input for the VTT LDO. Connect to plus terminal of the VTT LDO output capacitor.                                                                                                                                          |

| 3      | GND     | Signal Ground                                                                                                                                                                                                                           |

| 4      | VTTREF  | VTTREF buffered reference output.                                                                                                                                                                                                       |

| 5      | VDDQSNS | VDDQ reference input for VTT and VTTREF. Power supply for the VTTREF. Discharge current sinking terminal for VDDQ non-tracking discharge.                                                                                               |

| 6      | FB      | VDDQ output voltage setting pin.                                                                                                                                                                                                        |

| 7      | S3      | S3 signal input.                                                                                                                                                                                                                        |

| 8      | S5      | S5 signal input.                                                                                                                                                                                                                        |

| 9      | TON     | This Pin is Allowed to Adjust The Switching Frequency. Connect a resistor $R_{TON} = 100K\Omega \sim 1.2M\Omega$ from TON pin to PHASE pin.                                                                                             |

| 10     | PGOOD   | Power-good output pin. PGOOD is an open drain output used to Indicate the status of the output voltage.<br>When VDDQ output voltage is within the target range, it is in high state.                                                    |

| 11, 12 | VCC     | 5V power supply voltage input pin for both internal control circuitry and low-side MOSFET gate driver.                                                                                                                                  |

| 13     | CS      | Over-current trip voltage setting input for $R_{DS(ON)}$ current sense scheme if connected to VCC through the voltage setting resistor.                                                                                                 |

| 14     | PGND    | Power ground of the LGATE low-side MOSFET driver. Connect the pin to the Source of the low-side MOSFET.                                                                                                                                 |

| 15     | LGATE   | Output of the low-side MOSFET driver for PWM. Connect this pin to Gate of the low-side MOSFET. Swings from PGND to VCC.                                                                                                                 |

| 16     | PHASE   | Junction point of the high-side MOSFET Source, output filter inductor and the low-side MOSFET Drain. Connect this pin to the Source of the high-side MOSFET. PHASE serves as the lower supply rail for the UGATE high-side gate driver. |

| 17     | UGATE   | Output of the high-side MOSFET driver for PWM. Connect this pin to Gate of the high-side MOSFET.                                                                                                                                        |

| 18     | воот    | Supply Input for the UGATE Gate Driver and an internal level-shift circuit. Connect to an external capacitor and diode to create a boosted voltage suitable to drive a logic-level N-channel MOSFET.                                    |

| 19     | LDOIN   | Supply voltage input for the VTT LDO.                                                                                                                                                                                                   |

| 20     | VTT     | Power output for the VTT LDO.                                                                                                                                                                                                           |

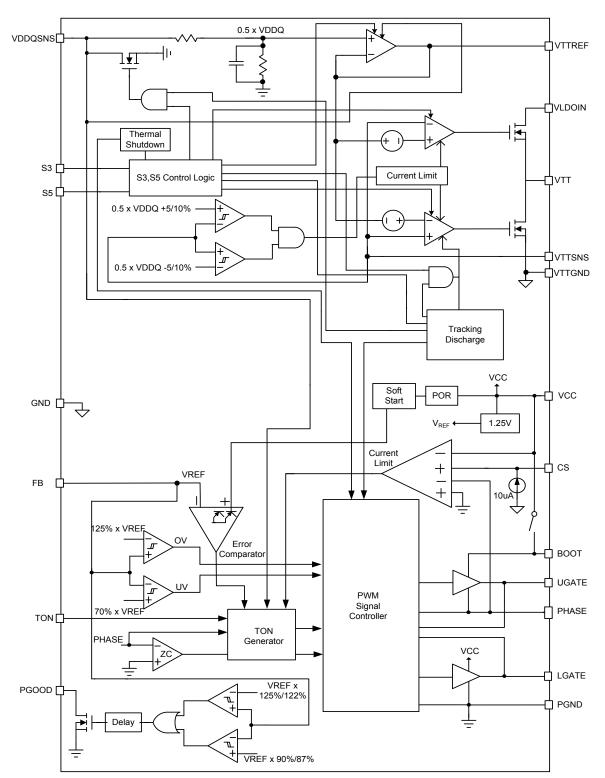

## **Block Diagram**

## **Typical Application Circuit**

## **Function Descriptions**

The APW8868C integrates a synchronous buck PWM controller to generate VDDQ, a sourcing and sinking LDO linear regulator to generate VTT. It provides a complete power supply for DDR2 and DDR3/DDR3L memory system in a 20-pin TQFN package. User defined output voltage is also possible and can be adjustable from 0.75V to 5.5V. Input voltage range of the PWM converter is 3V to 28V. The converter runs an adaptive on-time PWM operation at high-load condition and automatically reduces frequency to keep excellent efficiency down to several mA. The VTT LDO can source and sink up to 1.5A peak current with only  $10\mu$ F ceramic output capacitor. VTTREF tracks VDDQ/2 within 1% of VDDQ. VTT output tracks VTTREF within 20mV at no load condition while 40mV at full load. The LDO input can be separated from VDDO and optionally connected to a lower voltage by using VLDOIN pin. This helps reducing power dissipation in sourcing phase. The APW8868C is fully compatible to JEDEC DDR2 and DDR3/DDR3L specifications at S3/ S5 sleep state (see Table 1). When both VTT and VDDQ are disabled, the non-tracking discharge mode discharges outputs using internal discharge MOSFETs that are connected to VDDQSNS and VTT.

#### Constant-On-Time PWM Controller with Input Feed-Forward

The constant on-time control architecture is a pseudofixed frequency with input voltage feed-forward. This architecture relies on the output filter capacitor's effective series resistance (ESR) to act as a current-sense resistor, so the output ripple voltage provides the PWMramp signal. In PFM operation, the high-side switch on-time controlled by the on-time generator is determined solely by a oneshot whose pulse width is inversely proportional to input voltage and directly proportional to output voltage. In PWM operation, the high-side switch on-time is determined by a switching frequency control circuit in the on-time generator block. The switching frequency control circuit senses the switching frequency of the high-side switch and keeps regulating it at a constant frequency in PWM mode. The design improves the frequency variation and be more outstanding than a conventional constant ontime controller which has large switching frequency variation over input voltage, output current and temperature.

Both in PFM and PWM, the on-time generator, which senses input voltage on PHASE pin, provides very fast ontime response to input line transients.

Another one-shot sets a minimum off-time (typical: 300ns). The on-time one-shot is triggered if the error comparator is high, the low-side switch current is below the current-limit threshold, and the minimum off-time oneshot has timed out.

#### **Power-On-Reset**

A Power-On-Reset (POR) function is designed to prevent wrong logic controls when the VCC voltage is low. The POR function continually monitors the bias supply voltage on the VCC pin if at least one of the enable pins is set high. When the rising VCC voltage reaches the rising POR voltage threshold (4.1V typical), the POR signal goes high and the chip initiates soft-start operations. Should this voltage drop lower than 4V (typical), the POR disables the chip.

#### Soft- Start

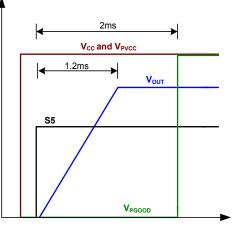

The APW8868C integrates digital soft-start circuits to ramp up the output voltage of the converter to the programmed regulation set point at a predictable slew rate. The slew rate of output voltage is internally controlled to limit the inrush current through the output capacitors during softstart process. The figure 1 shows VDDQ soft-start sequence. When the S5 pin is pulled above the rising S5 threshold voltage, the device initiates a soft-start process to ramp up the output voltage. The soft-start interval is 1.2ms (typical) and independent of the UGATE switching frequency.

Fig1. Soft-Start Sequence

During soft-start stage before the PGOOD pin is ready, the under voltage protection is prohibited. The over voltage and current limit protection functions are enabled. If the output capacitor has residue voltage before startup, both low-side and high-side MOSFETs are in off-state until the internal digital soft start voltage equal the internal feedback voltage. This will ensure the output voltage starts from its existing voltage level.

The VTT LDO part monitors the output current, both sourcing and sinking current, and limits the maximum output current to prevent damages during current overload or short circuit (shorted from VTT to GND or VLDOIN) conditions.

The VTT LDO provides a soft-start function, using the constant current to charge the output capacitor that gives a rapid and linear output voltage rise. If the load current is above the current limit start-up, the VTT cannot start successfully.

APW8868C has an independent counter for each output, but the PGOOD signal indicates only the status of VDDQ and does not indicate VTT power good externally.

#### Power-GoodOutput (PGOOD)

PGOOD is an open-drain output and the PGOOD comparator continuously monitors the output voltage. PGOOD is actively held low in shutdown, and standby.When PWM converter's output voltage is greater than 95% of its target value, the internal open-drain device will be pulled low. After  $63\mu s$  debounce time, the PGOOD goes high. The PGOOD goes low if V<sub>VDDQ</sub> output is 10% below or above its nominal regulation point.

## **Function Descriptions (Cont.)**

#### **Under Voltage Protection**

In the process of operation, if a short-circuit occurs, the output voltage will drop quickly. When load current is bigger than current limit threshold value, the output voltage will fall out of the required regulation range. The undervoltage continually monitors the setting output voltage after 2ms of PWM operations to ensure startup. If a load step is strong enough to pull the output voltage lower than the under voltage threshold (70% of normal output voltage), APW8868C shuts down the output gradually and latches off both high and low side MOSFETs.

#### **Over Voltage Protection (OVP)**

The feedback voltage should increase over 125% of the reference voltage due to the high-side MOSFET failure or for other reasons, and the over voltage protection comparator designed with a 1.5 $\mu$ s noise filter will force the low-side MOSFET gate driver to be high. This action actively pulls down the output voltage and eventually attempts to blow the battery fuse.

When the OVP occurs, the PGOOD pin will pull down and latch-off the converter. This OVP scheme only clamps the voltage overshoot, and does not invert the output voltage when otherwise activated with a continuously high output from low-side MOSFET driver. It's a common problem for OVP schemes with a latch. Once an over-voltage fault condition is set, toggling VCC power-on-reset signal can only reset it.

#### **PWM Converter Current Limit**

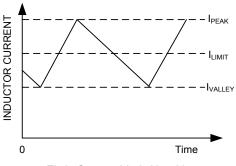

The current-limit circuit employs a unique "valley" current sensing algorithm (Figure 2). CS pin should be connected to VCC through the trip voltage-setting resistor,  $R_{CS}$ . CS terminal sinks 10uA current,  $I_{CS}$ , and the current limit threshold is set to the voltage across the  $R_{CS}$ . The voltage between or CS\_GND pin and PHASE pin monitors the inductor current so that PHASE pin should be connected to the drain terminal of the low side MOSFET. PGND is used as the positive current sensing node so that PGND should be connected to the sense resistor or the source terminal of the low side MOSFET.

If the magnitude of the current-sense signal is above the current-limit threshold, the PWM is not allowed to initiate a new cycle. The actual peak current is greater than the current-limit threshold by an amount equal to the inductor ripple current. Therefore, the exact current- limit characteristic and maximum load capability are a function of the sense resistance, inductor value, and input voltage. The equation for the current limit threshold is as follows:

$$I_{\text{LIMIT}} = \frac{RCS \times 10 uA}{R_{\text{DS(ON)}}} + \frac{(V_{\text{IN}} - V_{\text{VDDQ}})}{2 \times L \times f_{\text{sw}}} \times \frac{V_{\text{VDDQ}}}{V_{\text{IN}}}$$

Where  $I_{\text{LIMIT}}$  is the desired current limit threshold,  $R_{\text{CS}}$  is the value of the current sense resistor connected to VCC and CS pin  $V_{\text{CS}}$  is the voltage across the  $R_{\text{CS}}$  resistor  $I_{\text{RIPPLE}}$  is inductor peak to peak current  $F_{\text{SW}}$  is the PWM switching frequency.

In a current limit condition, the current to the load exceeds the current to the output capacitor thus the output voltage tends to fall down. If the output voltage becomes less than power good level, the  $V_{\rm CS}$  is cut into half and the output voltage tends to be even lower. Eventually, it crosses the under voltage protection threshold and shutdown.

Fig2. Current Limit Algorithm

#### VTT Sink/Source Regulator

The output voltage at VTT pin tracks the reference voltage applied at VTTREF pin. Two internal N-channel MOSFETs controlled by separate high bandwidth error amplifiers regulate the output voltage by sourcing current from VLDOIN pin or sinking current to GND pin. To prevent two pass transistors from shoot-through, a small voltage offset is created between the positive inputs of the two error amplifiers. The VTT with fast response feedback loop keeps tracking to the VTTREF within ±40 mV at all conditions including fast load transient.

#### S3, S5 Control

In the DDR2 and DDR3/DDR3L memory applications, it is important to keep VDDQ always higher than VTT/VTTREF including both start-up and shutdown. The S3 and S5 signals control the VDDQ, VTT, VTTREF states and these pins should be connected to SLP\_S3 and SLP\_S5 signals respectively. The table1 shows the truth table of the S3 and S5 pins. When both S3 and S5 are above the logic threshold voltage, the VDDQ, VTT and VTTREF are turned on at S0 state. When S3 is low and S5 is high, the VDDQ and VTTREF are kept on while the VTT voltage is disabled and left high impedance in S3 state. When both S3 and S5 are low, the VDDQ, VTT and VTTREF are turned off and discharged to the ground.

Table1. The Truth Table of S3 and S5 pins.

|       |    |    |               | •             |               |

|-------|----|----|---------------|---------------|---------------|

| STATE | S3 | S5 | VDDQ          | VTTREF        | VTT           |

| S0    | Н  | н  | 1             | 1             | 1             |

| S3    | L  | н  | 1             | 1             | 0 (high-Z)    |

| S4/5  | L  | L  | 0 (discharge) | 0 (discharge) | 0 (discharge) |

#### Thermal Shutdown

A thermal shutdown circuit limits the junction temperature of APW8868C. When the junction temperature exceeds +160°C, PWMconverter, VTTLDO and VTTREF are shut off, allowing the device to cool down. The regulator regulates the output again through initiation of a new softstart cycle after the junction temperature cools by 25°C, resulting in a pulsed output during continuous thermal overload conditions. The thermal shutdown designed with a 25°C hysteresis lowers the average junction temperature during continuous thermal overload conditions, extending life time of the device. For normal operation, device power dissipation should be externally limited so that junction temperatures will not exceed +125°C.

## Function Descriptions (Cont.)

# Programming the On-Time Control and PWM Switching Frequency

The APW8868C does not use a clock signal to produce PWM. The device uses the constant on-time control architecture to produce pseudo-fixed frequency with input voltage feed-forward. The on-time pulse width is proportional to output voltage  $V_{OUT}$  and inverse proportional to input voltage  $V_{IN}$ . In PWM, the on-time calculation is written as below equation.

$$T_{\rm ON} = 6.3 \times 10^{-12} \times R_{\rm TON} \times \left[\frac{\frac{2}{3} \times V_{\rm VDDQ}}{V_{\rm IN}}\right]$$

Where:

$R_{\text{TON}}$  is the resistor connected from TON pin to PHASE pin. Furthermore, The approximate PWM switching frequency is written as:

$$\Gamma_{\rm ON} = \frac{D}{F_{\rm sw}} = F_{\rm sw} = \frac{V_{\rm out} / V_{\rm in}}{T_{\rm on}}$$

Where:

${\sf F}_{\sf sw}$  is the PWM switching frequency

APW8868C doesn't have VIN pin to calculate on-time pulse width. Therefore, monitoring  $V_{\text{PHASE}}$  voltage as input voltage to calculate on-time when the high-side MOSFET is turned on. And then, use the relationship between on-time and duty cycle to obtain the switching frequency.

## **Application Information**

#### **Output Voltage Selection**

PWM can be also adjusted from 0.75V to 5.5V with a resistor-driver at FB between VDDQSNS and GND. Using 1% or better resistors for the resistive divider is recommended. The FB pin is the inverter input of the error amplifier, and the reference voltage is 0.75V. Take the example, the output voltage of PWM is determined by:

$$V_{\text{OUT}} \!=\! 0.75 \!\times \! \left[ 1 \!+\! \frac{R_{\text{TOP}}}{R_{\text{GND}}} \right]$$

Where  $R_{\text{TOP}}$  is the resistor connected from  $V_{\text{OUT}}$  to FB and  $R_{\text{GND}}$  is the resistor connected from FB to GND.

#### **Output Inductor Selection**

The duty cycle of a buck converter is the function of the input voltage and output voltage. Once an output voltage is fixed, it can be written as:

$$D = \frac{V_{OUT}}{V_{IN}}$$

The inductor value determines the inductor ripple current and affects the load transient response. Higher inductor value reduces the inductor's ripple current and induces lower output ripple voltage. The ripple current and ripple voltage can be approximated by:

$$I_{\text{RIPPLE}} = \frac{V_{\text{IN}} - V_{\text{OUT}}}{F_{\text{SW}} \times L} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}}$$

Where  $F_{sw}$  is the switching frequency of the regulator. Although increase the inductor value and frequency reduce the ripple current and voltage, there is a tradeoff between the inductor's ripple current and the regulator load transient response time.

A smaller inductor will give the regulator a faster load transient response at the expense of higher ripple current. Increasing the switching frequency ( $F_{SW}$ ) also reduces the ripple current and voltage, but it will increase the switching loss of the MOSFETs and the power dissipation of the converter. The maximum ripple current occurs at the maximum input voltage. A good starting point is to choose the ripple current to be approximately 30% of the maximum output current. Once the inductance value has been chosen, selecting an inductor is capable of carrying the required peak current without going into saturation.

In some types of inductors, especially core that is made of ferrite, the ripple current will increase abruptly when it saturates. This will be result in a larger output ripple voltage.

#### **Output Capacitor Selection**

Output voltage ripple and the transient voltage deviation are factors that have to be taken into consideration when selecting an output capacitor. Higher capacitor value and lower ESR reduce the output ripple and the load transient drop. Therefore, selecting high performance low ESR capacitors is intended for switching regulator applications. In addition to high frequency noise related MOSFET turnon and turn-off, the output voltage ripple includes the capacitance voltage drop and ESR voltage drop caused by the AC peak-to-peak current. These two voltages can be represented by:

$$\Delta V_{\text{COUT}} = \frac{I_{\text{RIPPLE}}}{8C_{\text{OUT}}F_{\text{SW}}}$$

$\Delta V_{\text{ESR}} = I_{\text{RIPPLE}} \times R_{\text{ESR}}$

These two components constitute a large portion of the total output voltage ripple. In some applications, multiple capacitors have to be paralleled to achieve the desired ESR value. If the output of the converter has to support another load with high pulsating current, more capacitors are needed in order to reduce the equivalent ESR and suppress the voltage ripple to a tolerable level. A small decoupling capacitor in parallel for bypassing the noise is also recommended, and the voltage rating of the output capacitors must also be considered.

To support a load transient that is faster than the switching frequency, more capacitors have to be used to reduce the voltage excursion during load step change. Another aspect of the capacitor selection is that the total AC current going through the capacitors has to be less than the rated RMS current specified on the capacitors to prevent the capacitor from over-heating.

#### Input Capacitor Selection

The input capacitor is chosen based on the voltage rating and the RMS current rating. For reliable operation, select the capacitor voltage rating to be at least 1.3 times higher than the maximum input voltage. The maximum RMS current rating requirement is approximately  $I_{OUT}/2$ , where  $I_{OUT}$  is the load current. During power up, the input capacitors have to handle large amount of surge current. In low-duty notebook applications, ceramic capacitors are recommended. The capacitors must be connected between the drain of high-side MOSFET and the source of low-side MOSFET with very low-impedance PCB layout.

#### **MOSFET Selection**

The application for a notebook battery with a maximum voltage of 24V, at least a minimum 30V MOSFETs should be used. The design has to trade off the gate charge with the  $R_{DS(ON)}$  of the MOSFET:

- For the low-side MOSFET, before it is turned on, the body diode has been conducted. The low-side MOSFET driver will not charge the miller capacitor of this MOSFET.

- In the turning off process of the low-side MOSFET, the load current will shift to the body diode first. The high dv/dt of the phase node voltage will charge the miller capacitor through the low-side MOSFET driver sinking current path. This results in much less switching loss of the low-side MOSFETs. The duty cycle is often very small in high battery voltage applications, and the low-side MOSFET will conduct most of the switching cycle; therefore, the  $R_{DS(ON)}$  of the lowside MOSFET, the less the power loss. The gate charge for this MOSFET is usually a secondary consideration. The high-side MOSFET does not have this zero voltage switching condition, and because it conducts for less time compared to the lowside MOSFET, the switching loss tends to be dominant. Priority should be given to the MOSFETs with less gate charge, so that both the gate driver loss and switching loss will be minimized.

## **Application Information (Cont.)**

#### **MOSFET Selection (Cont.)**

The selection of the N-channel power MOSFETs are determined by the  $R_{DS(ON)}$ , reversing transfer capacitance  $(C_{RSS})$  and maximum output current requirement. The losses in the MOSFETs have two components: conduction loss and transition loss. For the high-side and lowside MOSFETs, the losses are approximately given by the following equations:

$\mathsf{P}_{\mathsf{high-side}} = \mathsf{IOUT}^2(1+\mathsf{TC})(\mathsf{R}_{\mathsf{DS}(\mathsf{ON})})\mathsf{D} + (0.5)(\mathsf{I}_{\mathsf{OUT}})(\mathsf{V}_{\mathsf{IN}})(\mathsf{t}_{\mathsf{SW}})\mathsf{F}_{\mathsf{SW}}$

$P_{low-side} = IOUT_2(1+TC)(R_{DS(ON)})D(1-D)$

Where

I is the load current

TC is the temperature dependency of  $R_{DS(ON)}$   $F_{SW}$  is the switching frequency  $t_{SW}$  is the switching interval D is the duty cycle

D is the duty cycle

Note that both MOSFETs have conduction losses while the high-side MOSFET includes an additional transition loss. The switching internal,  $t_{SW}$ , is the function of the reverse transfer capacitance  $C_{RSS}$ . The (1+TC) term is to factor in the temperature dependency of the  $R_{DS(ON)}$  and can be extracted from the " $R_{DS(ON)}$  vs Temperature" curve of the power MOSFET.

#### Layout Consideration

In any high switching frequency converter, a correct layout is important to ensure proper operation of the regulator. With power devices switching at higher frequency, the resulting current transient will cause voltage spike across the interconnecting impedance and parasitic circuit elements. As an example, consider the turn-off transition of the PWM MOSFET. Before turn-off condition. the MOSFET is carrying the full load current. During turn-off, current stops flowing in the MOSFET and is freewheeling by the lower MOSFET and parasitic diode. Any parasitic inductance of the circuit generates a large voltage spike during the switching interval. In general, using short and wide printed circuit traces should minimize interconnecting impedances and the magnitude of voltage spike. And signal and power grounds are to be kept separating and finally combined to use the ground plane construction or single point grounding. The best tie-point between the signal ground and the power ground is at the negative side of the output capacitor on each channel, where there is less noise. Noisy traces beneath the IC are not recommended. Below is a checklist for your layout:

- Keep the switching nodes (UGATE, LGATE, BOOT, and PHASE) away from sensitive small signal nodes(VFB, VTTREF, and CS) since these nodes are fast moving signals. Therefore, keep traces to these nodes as short as possible and there should be no other weak signal traces in parallel with theses traces on any layer.

- The signals going through theses traces have both high dv/dt and high di/dt, with high peak charging and discharging current. The traces from the gate drivers to the MOSFETs (UGATE and LGATE) should be short and wide. - Place the source of the high-side MOSFET and the drain of the low-side MOSFET as close as possible. Minimizing the impedance with wide layout plane between the two pads reduces the voltage bounce of the node.

- Decoupling capacitor, the resistor dividers, boot capacitors, and current limit stetting resistor should be close their pins. (For example, place the decoupling ceramic capacitor near the drain of the high-side MOSFET as close as possible. The bulk capacitors are also placed near the drain).

- The input capacitor should be near the drain of the upper MOSFET; the high quality ceramic decoupling capacitor can be put close to the VCC and GND pins; the VTTREF decoupling capacitor should be close to the VTTREF pin and GND; the VDDQ and VTT output capacitors should be located right across their output pin as close as possible to the part to minimize parasitic. The input capacitor GND should be close to the output capacitor GND and the lower MOSFET GND.

- The drain of the MOSFETs (VIN and PHASE nodes) should be a large plane for heat sinking. And PHASE pin traces are also the return path for UGATE. Connect this pin to the converter's upper MOSFET source.

- The APW8868A used ripple mode control. Build the resistor divider close to the VFB pin so that the high impedance trace is shorter. And the VFB pin traces can't be closed to the switching signal traces (UGATE, LGATE, BOOT, and PHASE).

- The PGND trace should be a separate trace, and independently go to the source of the low-side MOSFETs for current limit accuracy.

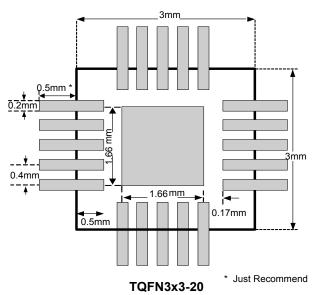

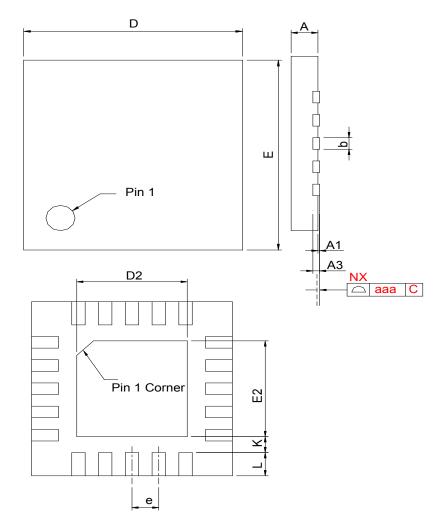

Figure3. Recommended Minimum Footprint

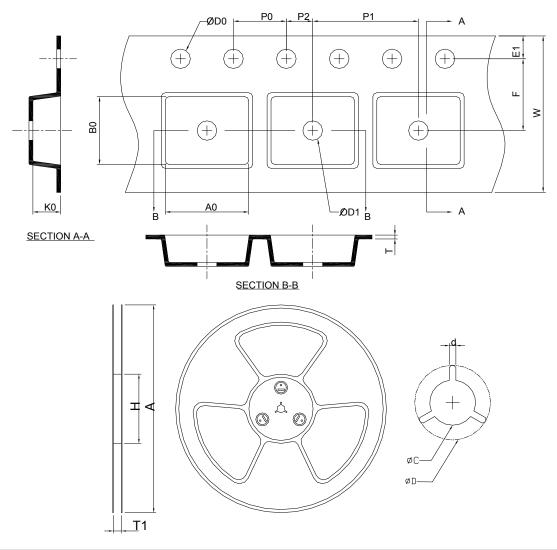

## **Package Information**

TQFN3x3-20

| S      | TQFN3x3-20  |                  |                |       |  |  |  |

|--------|-------------|------------------|----------------|-------|--|--|--|

| SY MBO | MILLIM      | ETERS            | INCH           | ES    |  |  |  |

| P<br>L | MIN.        | MAX.             | MIN.           | MAX.  |  |  |  |

| A      | 0.70        | 0.80             | 0.028          | 0.031 |  |  |  |

| A1     | 0.00        | 0.05             | 0.000          | 0.002 |  |  |  |

| A3     | 0.20        | REF              | 0.008          | REF   |  |  |  |

| b      | 0.15        | 0.25             | 0.006          | 0.010 |  |  |  |

| D      | 2.90        | 3.10             | 0.114          | 0.122 |  |  |  |

| D2     | 1.50        | 1.80             | 0.059          | 0.071 |  |  |  |

| E      | 2.90        | 3.10             | 0.114          | 0.122 |  |  |  |

| E2     | 1.50        | 1.80             | 0.059          | 0.071 |  |  |  |

| е      | 0.40        | BSC              | 0.016          | BSC   |  |  |  |

| L      | 0.30        | 0.50             | 0.012          | 0.020 |  |  |  |

| К      | 0.20        |                  | 0.008          |       |  |  |  |

| aaa    | 0.0         | 08               | 0.00           | 3     |  |  |  |

|        | Note : 1. F | Followed from JE | DEC MO-220 WEE | E     |  |  |  |

Copyright©ANPEC Electronic Corp. Rev. A.4 – Jan., 2021

## **Carrier Tape & Reel Dimensions**

| Application | Α        | Н        | T1                 | С                  | d        | D         | w         | E1        | F         |

|-------------|----------|----------|--------------------|--------------------|----------|-----------|-----------|-----------|-----------|

|             | 330±2.00 | 50 MIN.  | 12.4+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN. | 12.0±0.30 | 1.75±0.10 | 5.5±0.05  |

| TQFN3x3-20  | P0       | P1       | P2                 | D0                 | D1       | Т         | A0        | В0        | K0        |

|             | 4.0±0.10 | 8.0±0.10 |                    | 1.5+0.10           | 1.5 MIN. | 0.6+0.00  | 3.30±0.20 | 3.30±0.20 | 1.00±0.20 |

(mm)

## **Devices Per Unit**

| Package Type | Unit        | Quantity |

|--------------|-------------|----------|

| TQFN3x3-20   | Tape & Reel | 3000     |

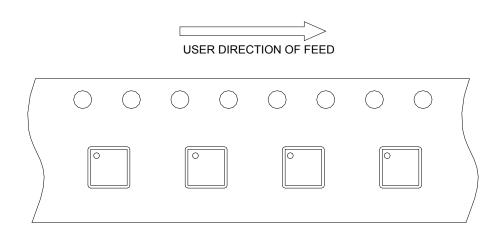

### **Taping Direction Information**

TQFN3x3-20

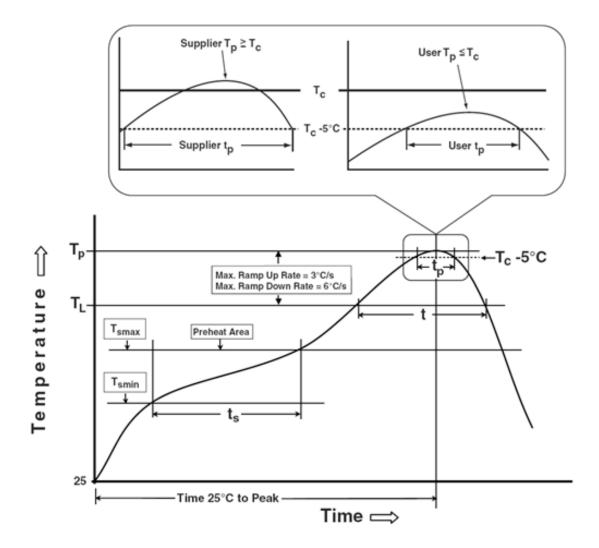

## **Classification Profile**

## **Classification Reflow Profiles**

| Profile Feature                                                                                                                                                                                                                    | Sn-Pb Eutectic Assembly            | Pb-Free Assembly                   |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|--|--|

| $\begin{array}{c} \textbf{Preheat \& Soak} \\ \textbf{Temperature min} (\textbf{T}_{smin}) \\ \textbf{Temperature max} (\textbf{T}_{smax}) \\ \textbf{Time} (\textbf{T}_{smin} \text{ to } \textbf{T}_{smax}) (t_{s}) \end{array}$ | 100 °C<br>150 °C<br>60-120 seconds | 150 °C<br>200 °C<br>60-120 seconds |  |  |

| Average ramp-up rate $(T_{smax} \text{ to } T_P)$                                                                                                                                                                                  | 3 °C/second max.                   | 3°C/second max.                    |  |  |

| Liquidous temperature $(T_L)$<br>Time at liquidous $(t_L)$                                                                                                                                                                         | 183 °C<br>60-150 seconds           | 217 °C<br>60-150 seconds           |  |  |

| Peak package body Temperature $(T_p)^*$                                                                                                                                                                                            | See Classification Temp in table 1 | See Classification Temp in table 2 |  |  |

| Time $(t_P)^{**}$ within 5°C of the specified classification temperature $(T_c)$                                                                                                                                                   | 20** seconds                       | 30** seconds                       |  |  |

| Average ramp-down rate ( $T_p$ to $T_{smax}$ )                                                                                                                                                                                     | 6 °C/second max.                   | 6 °C/second max.                   |  |  |

| Time 25°C to peak temperature                                                                                                                                                                                                      | 6 minutes max.                     | 8 minutes max.                     |  |  |

| * Tolerance for peak profile Temperature $(T_p)$ is defined as a supplier minimum and a user maximum.                                                                                                                              |                                    |                                    |  |  |

| ** Tolerance for time at peak profile temperature ( $t_p$ ) is defined as a supplier minimum and a user maximum.                                                                                                                   |                                    |                                    |  |  |

Table 1. SnPb Eutectic Process – Classification Temperatures (Tc)

| Package   | Volume mm <sup>3</sup> | Volume mm <sup>3</sup> |  |

|-----------|------------------------|------------------------|--|

| Thickness | <350                   | <u>&gt;</u> 350        |  |

| <2.5 mm   | 235 °C                 | 220 °C                 |  |

| ≥2.5 mm   | 220 °C                 | 220 °C                 |  |

Table 2. Pb-free Process – Classification Temperatures (Tc)

| Package         | Volume mm <sup>3</sup> | Volume mm <sup>3</sup> | Volume mm <sup>3</sup> |

|-----------------|------------------------|------------------------|------------------------|

| Thickness       | <350                   | 350-2000               | >2000                  |

| <1.6 mm         | 260 °C                 | 260 °C                 | 260 °C                 |

| 1.6 mm – 2.5 mm | 260 °C                 | 250 °C                 | 245 °C                 |

| ≥2.5 mm         | 250 °C                 | 245 °C                 | 245 °C                 |

### Reliability Test Program

| Test item     | Method             | Description                            |

|---------------|--------------------|----------------------------------------|

| SOLDERABILITY | JESD-22, B102      | 5 Sec, 245°C                           |

| HOLT          | JESD-22, A108      | 1000 Hrs, Bias @ T <sub>i</sub> =125°C |

| PCT           | JESD-22, A102      | 168 Hrs, 100%RH, 2atm, 121°C           |

| TCT           | JESD-22, A104      | 500 Cycles, -65°C~150°C                |

| HBM           | MIL-STD-883-3015.7 | $VHBM \ge 2KV$                         |

| MM            | JESD-22, A115      | $VMM \ge 200V$                         |

| Latch-Up      | JESD 78            | 10ms, $1_{tr} \ge 100 \text{mA}$       |

### **Customer Service**

#### Anpec Electronics Corp.

Head Office : No.6, Dusing 1st Road, SBIP, Hsin-Chu, Taiwan, R.O.C. Tel : 886-3-5642000 Fax : 886-3-5642050

Taipei Branch : 2F, No. 11, Lane 218, Sec 2 Jhongsing Rd., Sindian City, Taipei County 23146, Taiwan Tel : 886-2-2910-3838 Fax : 886-2-2917-3838

Copyright©ANPEC Electronic Corp. Rev. A.4 – Jan., 2021