Peak 5A, 18V, 500kHz Synchronous Step-Down Converter

#### **Features**

- Input Voltage range: 4.5V to 18V.

- Peak 5A Output Current, continue 4.3A.

- Typical 0.6V ±1% Internal Reference Voltage.

- Optimized Upper and Lower MOSFETs R<sub>DS\_on</sub> for max Efficiency:

- N-CH MOSFET (65m $\Omega$ ) for High Side

- N-CH MOSFET (35mΩ) for Low Side

- Built in OVP, UVP, Current Limit and OTP.

- Low Cost TSOT23-8 package.

- Lead Free and Green Devices Available (RoHS Compliant).

### **General Description**

The APW9114 is a high efficiency synchronous buck converter with integrated  $65m\Omega/35m\Omega$  of upper/lower power MOSFET and offers 4.3A continuous current capability.

The APW9114 uses a peak current mode control scheme to regulate the output voltage. The internal switching frequency is set at 500kHz.

The APW9114 is also equipped with Power-on-reset, soft start, and whole protections (over-temperature, overvoltage, under-voltage, over-current) into a single package.

The APW9114 is offered in a TSOT23-8 package allowing small size while having an excellent thermal capability for power dissipation.

# **Applications**

- Digital Subscriber Line

- Set-Top-Box

- Passive Optical Network

- G.fast

- General DC to DC Converter Applications

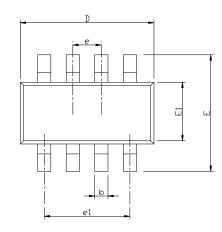

# Pin Configuration (Top View)

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

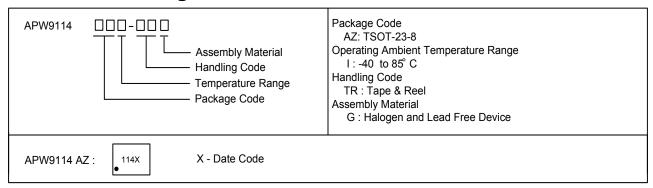

# **Order and Marking Information**

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by weight).

# **Absolute Maximum Ratings (Note 1)**

| Symbol           | Parameter                                      | Rating             | Unit |

|------------------|------------------------------------------------|--------------------|------|

| $V_{\text{VIN}}$ | VIN to GND                                     | -0.3 ~ 19          | V    |

| V <sub>BS</sub>  | BST to LX                                      | -0.3 ~ 5.5         | V    |

| V <sub>LX</sub>  | LX to GND                                      | -1 ~ 19            | V    |

| V <sub>I/O</sub> | VCC, EN, FB to GND                             | -0.3 ~ 6           | V    |

| PD               | Power Dissipation                              | Internally Limited | W    |

| T <sub>J</sub>   | Junction Temperature                           | 150                | °C   |

| T <sub>STG</sub> | Storage Temperature                            | -65 ~ 150          | °C   |

| T <sub>SDR</sub> | Maximum Lead Soldering Temperature(10 Seconds) | 260                | °C   |

Note 1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Thermal Characteristics**

| Symbol        | Parameter                                           | Typical Value | Unit |

|---------------|-----------------------------------------------------|---------------|------|

| $\theta_{JA}$ | Junction-to-Ambient Resistance in free air (Note 2) | 100           | °C/W |

| $\theta_{JA}$ | Junction-to-Ambient Resistance in free air (Note 3) | 65            | °C/W |

Note 2:  $\theta_{JA}$  is measured on 4 layers test board following the EIA/JESD51-7.

Note 3:  $\theta_{\mbox{\tiny JA}}$  is measured on Anpec evaluation board in free air.

# **Recommended Operating Conditions (Note 4)**

| Symbol           | Parameter                | Range     | Unit |

|------------------|--------------------------|-----------|------|

| V <sub>IN</sub>  | VIN supply voltage       | 4.5 ~ 18  | V    |

| V <sub>EN</sub>  | EN input voltage         | 0 ~ 5     | V    |

| V <sub>out</sub> | Converter output voltage | 0.6 ~ 5   | V    |

| I <sub>out</sub> | Converter output current | 4.3       | Α    |

| T <sub>A</sub>   | Ambient Temperature      | -40 ~ 85  | °C   |

| T <sub>J</sub>   | Junction Temperature     | -40 ~ 125 | °C   |

Note 4: Refer to the typical application circuit.

# **APW9114**

## **Electrical Characteristics**

Unless otherwise specified, these specifications apply over VIN=12V,  $T_A$ =25°C.

| 0                      | B                               | T- 4 distan                  | S    | pecificatio | n    | Unit |

|------------------------|---------------------------------|------------------------------|------|-------------|------|------|

| Symbol                 | Parameter                       | Test condition               | Min. | Тур.        | Max. | Unit |

| SUPPLY                 |                                 | ·                            |      |             |      |      |

| V <sub>UVLO_R</sub>    | UVLO Upper Threshold            | VIN Rising                   | -    | 4.2         | -    | V    |

| V <sub>UVLO_HYS</sub>  | UVLO Hysteresis Voltage         | VIN Falling                  | -    | 0.4         | -    | V    |

| I <sub>VIN</sub>       | VIN Input Current               | V <sub>FB</sub> =0.7V, LX=NC | -    | 100         | -    | μA   |

| I <sub>VIN_SHDN</sub>  | VIN Shutdown Current            | EN=GND                       |      | 3           | -    | μA   |

| EN Thresh              | old                             |                              |      |             |      |      |

| $V_{\text{EN\_H}}$     | EN Input Threshold High Voltage |                              | -    | 1           | 1.15 | V    |

| $V_{\text{EN\_Hys}}$   | EN Input Hysteresis Voltage     |                              | -    | 0.25        | -    | V    |

| T <sub>DB_EN_OFF</sub> | EN Turn Off Debounce Time       |                              | -    | 20          | -    | μs   |

| T <sub>D_EN</sub>      | EN Turn On Delay Time           | When EN High to LX Switching | -    | 550         | -    | μs   |

| I <sub>EN</sub>        | EN Input Current                | VEN=2V                       | -    | 2           | -    | μA   |

| R <sub>DIS</sub>       | Discharge Resistor              | When EN goes Low             | -    | 20          | -    | Ω    |

| REGULATO               | OR AND VCC                      |                              |      |             |      |      |

| $V_{REF}$              | Reference Voltage               | T <sub>J</sub> =25°C         | 594  | 600         | 606  | mV   |

|                        | Load Regulation                 | IOUT=10mA~4.3A               | -    | 0.8         | -    | %    |

| $V_{POR}$              | VCC POR Threshold Voltage       | VCC Rising                   | -    | 4           | -    | V    |

| $V_{POR\_Hys}$         | VCC POR Hysteresis Voltage      | VCC Falling                  | -    | 0.4         | -    | V    |

| $V_{\text{vcc}}$       | VCC Regulator Output Voltage    | I <sub>VCC</sub> =0A         | -    | 5           | -    | V    |

|                        | VCC Load Regulation             | I <sub>vcc</sub> =10mA       | -    | 3           | -    | %    |

|                        | VCC Maximum Current             | When VCC drop to 4.75V       | 40   | -           | -    | mA   |

| t <sub>ss</sub>        | Output Soft Start Time          | VOUT form 0% to 90%          | -    | 1           | -    | ms   |

| OSCILLAT               | OR FREQUENCY                    |                              |      |             |      |      |

| Fosc                   | Oscillator Frequency            |                              | -    | 500         | -    | kHz  |

|                        | Frequency Accuracy              | T <sub>J</sub> =-40~125°C    | -20  | -           | +20  | %    |

|                        | Minimum on Time                 |                              | -    | 70          | -    | ns   |

|                        | Maximum Duty                    | (Note5)                      | -    | 90          | -    | %    |

# **Electrical Characteristics (Cont.)** Unless otherwise specified, these specifications apply over VIN=12V, $T_A$ =25°C.

| Symbol                       | Parameter                           | Took oo maliki oo                                  | 5    | Specification |      |                   |

|------------------------------|-------------------------------------|----------------------------------------------------|------|---------------|------|-------------------|

| Symbol                       |                                     | Test condition                                     | Min. | Тур.          | Max. | Unit              |

| POWER M                      | OSFET                               |                                                    | ·    |               |      | -                 |

|                              | High Side MOSFET Resistance         |                                                    | -    | 65            | -    | mΩ                |

|                              | Low Side MOSFET Resistance          |                                                    | -    | 35            | -    | mΩ                |

|                              | High Side MOSFET Leakage<br>Current | V <sub>EN</sub> =0V, V <sub>LX</sub> =AGND         | -    | -             | 1    | μA                |

|                              | Low Side MOSFET Leakage Current     | V <sub>EN</sub> =5V, V <sub>LX</sub> =VIN, FB=0.7V | -    | -             | 1    | μA                |

| BOOTSTR                      | AP POWER                            |                                                    |      |               |      |                   |

| $R_{\scriptscriptstyle BST}$ | BST Switch On Resistance            |                                                    | -    | 14            | -    | Ω                 |

|                              | BST Leakage Current                 | V <sub>BST-LX</sub> =5V                            | -    | -             | 1    | μA                |

| PROTECT                      | IONS                                |                                                    |      |               |      |                   |

| I <sub>LIM</sub>             | High Side MOSFET current-limit      |                                                    | -    | 6             | -    | А                 |

|                              | Over-temperature Trip Point         |                                                    | -    | 150           | -    | °C                |

|                              | Over-temperature Hysteresis         |                                                    | -    | 30            | -    | °C                |

|                              | Under Voltage Protection            |                                                    | -    | 50            | -    | %V <sub>REF</sub> |

|                              | Over Voltage Protection             |                                                    | -    | 125           | -    | %V <sub>REF</sub> |

|                              | Hiccup Count Times                  |                                                    | -    | 11            | -    | t <sub>ss</sub>   |

Note5: Typical value is designed for switching frequency 500kHz

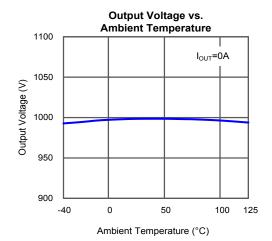

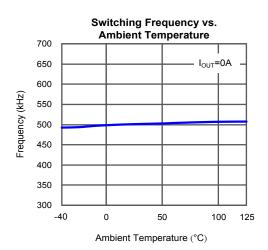

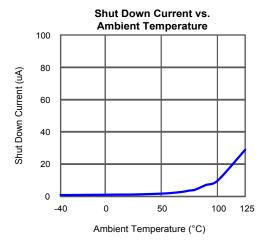

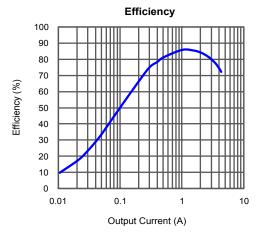

# **Typical Operating Characteristics**

Refer to the typical application circuit. The test condition is  $V_{IN}$ =12V,  $V_{OUT}$ =1V,  $C_{OUT}$ =22 $\mu$ F\*2,  $T_A$ = 25°C unless otherwise specified.

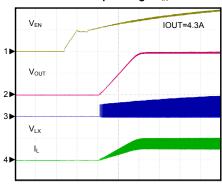

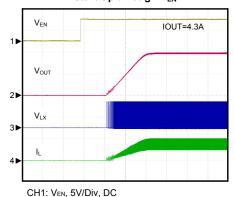

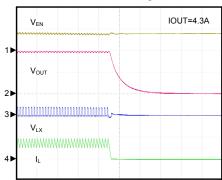

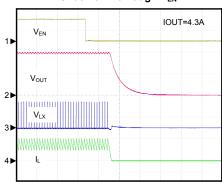

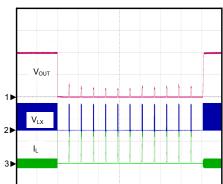

# **Operating Waveforms**

Refer to the typical application circuit. The test condition is  $V_{IN}$ =12V,  $V_{OUT}$ =1V,  $C_{OUT}$ =22 $\mu$ F\*2,  $T_A$ = 25°C unless otherwise specified.

#### Start Up through V<sub>IN</sub>

CH1: V<sub>IN</sub>, 5V/Div, DC CH2: V<sub>OUT</sub>, 500mV/Div, DC CH3: V<sub>LX</sub>, 10V/Div, DC CH4: I<sub>L</sub>, 5A/Div, DC TIME: 500µs/Div

#### Start Up through $V_{\text{EN}}$

CH1: VEN, 50/INV, DC

CH2: Vout, 500mV/Div, DC

CH3: VLx, 10V/Div, DC

CH4: IL, 5A/Div, DC

TIME: 500µs/Div

#### Shut Down through V<sub>IN</sub>

CH1:  $V_{IN}$ , 5V/Div, DC CH2:  $V_{OUT}$ , 500mV/Div, DC CH3:  $V_{LX}$ , 10V/Div, DC CH4:  $I_{L}$ , 5A/Div, DC TIME: 20 $\mu$ s/Div

#### Shut Down through $V_{\text{EN}}$

CH1:  $V_{EN}$ , 2V/Div, DCCH2:  $V_{OUT}$ , 500mV/Div, DCCH3:  $V_{LX}$ , 10V/Div, DCCH4:  $I_L$ , 5A/Div, DCTIME:  $20\mu s/Div$

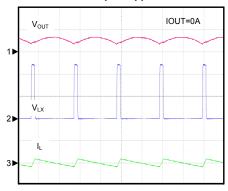

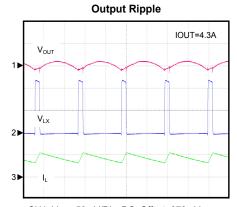

# **Operating Waveforms (Cont.)**

Refer to the typical application circuit. The test condition is  $V_{IN}$ =12V,  $V_{OUT}$ =1V,  $C_{OUT}$ =22 $\mu$ F\*2,  $T_A$ = 25°C unless otherwise specified.

CH1: Vout, 50mV/Div, DC, Offset=870mV

CH2:  $V_{LX}$ , 5V/Div, DC CH3:  $I_L$ , 5A/Div, DC TIME:  $1\mu s$ /Div

CH1: Vout, 50mV/Div, DC, Offset=870mV

CH2:  $V_{LX}$ , 5V/Div, DC CH3:  $I_L$ , 5A/Div, DC TIME:  $1\mu s$ /Div

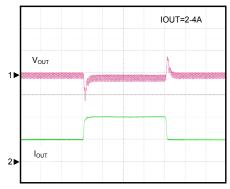

#### **Load Transient**

CH1: Vout, 100mV/Div, DC, Offset= -900mV

CH2: Iout, 2A/Div, DC TIME: 50µs/Div

#### **Short Circuit Protection**

CH1: Vout, 500mV/Div, DC CH2: VLX, 10V/Div, DC CH3: IL, 5A/Div, DC

TIME: 20ms/Div

# **APW9114**

# **Pin Description**

| Р        | ·IN  |                                                                                                                                                                                                                                                                            |  |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. NAME |      | FUNCTION                                                                                                                                                                                                                                                                   |  |

| 1        | AGND | Analog Small-Signal Ground This pin must be isolated with GND Pin.                                                                                                                                                                                                         |  |

| 2        | VIN  | Power Input Pin. VIN supplies the power to the buck converter.                                                                                                                                                                                                             |  |

| 3        | LX   | Power Switching Output. This pin is the junction of the high side power MOSFET and the low side power MOSFET. Connect this pin to the output inductor.                                                                                                                     |  |

| 4        | GND  | Power Ground. This pin must be connected directly to the GND plane of the PCB using low inductance vias.                                                                                                                                                                   |  |

| 5        | BST  | High-Side Gate Driver Supply Voltage Input Pin. A 0.1uF X5R ceramic capacitor is connected from this pin to the LX pin to provide a bootstrap voltage for the gate driver to drive the upper MOSFET.                                                                       |  |

| 6        | EN   | Enable Input Pin. Drive EN high to turn the converter on and drive it low to turn it off. The EN pin cannot be left floating.                                                                                                                                              |  |

| 7        | VCC  | Internal Regulator Output Pin. The VCC pin is the output of an internal 5V regulator for internal control circuitry. It is recommended to connect a 1uF X5R capacitor from the VCC pin to ground to ensure stability and regulation. Do not apply an external load to VCC. |  |

| 8        | FB   | Output Feedback Pin. FB senses the output voltage and regulates it. Connect the resistor divider from the output through FB to the ground to set the output voltage.                                                                                                       |  |

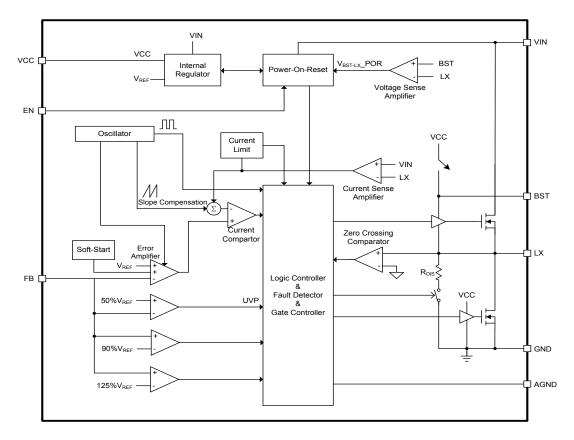

# **Block Diagram**

Figure 1: Block diagram of APW9114

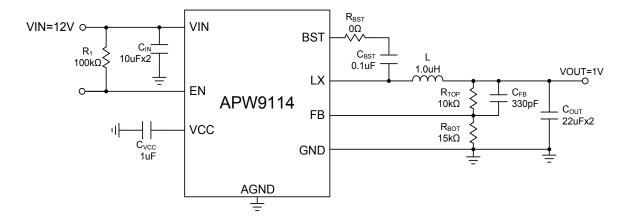

# **Typical Application Circuit**

### **Components Selection for Different Output Voltage**

| VIN<br>(V) | VOUT<br>(V) | IOUT<br>(A) | C <sub>IN</sub> (F) | L<br>(H) | С <sub>оит</sub><br>(F) | $R_{TOP} \ (\Omega)$ | $R_{\mathtt{BOT}}$ $(\Omega)$ | С <sub>FВ</sub> (F) |

|------------|-------------|-------------|---------------------|----------|-------------------------|----------------------|-------------------------------|---------------------|

| 12         | 1           | 0 ~ 4.3A    | 10µ × 2             | 1.0µ     | 22µ × 2                 | 10k (1%)             | 15k (1%)                      | 330p                |

# **Function Descriptions**

#### **Main Control Loop**

The IC uses current mode control to regulate the output voltage. The output voltage is measured at FB through a resistor divider and amplified by an internal transconductance error amplifier. The output of the transconductance error amplifier is compared to the switching current to adjust the duty cycle to control the output voltage. The benefit of current mode control is the ability to quickly adjust the duty cycle as the output current increases rapidly for fast load transient response.

#### VIN Under Voltage Lock Out (UVLO)

When the IC is powered up, the internal circuitry except VCC remains inactive until the VIN voltage exceeds the VIN UVLO high threshold voltage. When VIN is below the VIN UVLO low threshold voltage, the IC is turned off and the output discharge is triggered.

#### VCC Power-On-Reset (POR)

VCC is an internal voltage regulator that is activated when the IC is powered by VIN and EN goes high. The IC continuously monitors the voltage on the VCC pin. The soft start is activated, when the VCC voltage is higher than the POR threshold and the VIN voltage is higher than the UVLO threshold and the EN voltage is higher than the enable threshold.

VCC POR is used to protect the IC from erroneous operation with insufficient VCC voltage. VCC POR also has hysteresis to resist ripple on the VCC voltage.

#### Over-Voltage Protection (OVP)

The IC monitors the output voltage through the FB pin to implement the OVP function. When the FB voltage exceeds the OVP high threshold voltage, OVP will be triggered and the IC will be turned off until the FB voltage is lower than the OVP low threshold voltage. At this time, the OVP will be disabled and the IC will resume normal operation.

#### **Over-Temperature Protection (OTP)**

The IC features over-temperature protection to monitor junction temperature and prevent damage to the chip when operating at extremely high temperatures. Then the junction temperature exceeds the OTP threshold, the IC will be turned off to lower the junction temperature. The OTP circuit has hysteresis that allows the IC to restart when the junction temperature is below the OTP low threshold temperature.

#### Soft-Start

The IC has a built-in soft-start function that controls the rise time of the output voltage during start-up to reduce input current surges and prevent output overshoot. The soft start function will be enabled when any condition that can initiate an output start-up, such as VIN power to the IC or toggle the EN pin, and when the converter is restarted from the OTP and hiccup mode.

#### **Enable/Shutdown Controls**

The IC provides the EN pin, which is a digital input that turns the converter on or off. Drive EN high to turn the converter on and drive it low to turn it off.

#### **Over-Current-Protection and Hiccup**

The IC monitors the current through the high-side power MOSFET to limits the peak inductor current to prevent IC from being damaged in the event of an overload or short circuit. When the current limit protection is activated, the output current will be limited and the output voltage will drop. When the output voltage drops below the UVP threshold, UVP is triggered and the converter enters hiccup mode. In hiccup mode, the converter will restart periodically. This protection mode is especially useful when the output is shorted to ground. The average short-circuit current is greatly reduced to alleviate thermal issues and protect the IC. Once the over current condition is removed, the IC will exit the hiccup mode.

#### **Fast Discharge**

When the EN signal goes low or the VIN voltage falls below the UVLO threshold, the IC is turned off and the output fast discharge is triggered. The discharge MOSFET between the LX of the converter and ground is turned on, allowing the output capacitor to be quickly discharged through this MOSFET.

# **Application Information**

#### **Input Capacitor Selection**

The input capacitor is chosen based on the voltage rating and the RMS current rating. For reliable operation, select the capacitor voltage rating to be at least 1.3 times higher than the maximum input voltage.

Use low ESR capacitors for the best performance. Ceramic capacitors with X5R or X7R dielectrics are recommended highly because of their low ESR and small temperature coefficients.

Since the input capacitor (CIN) absorbs the input-switching current, it requires an adequate ripple-current rating. The RMS current in the input capacitor can be estimated by:

$$I_{\text{CIN}} = I_{\text{OUT}} \times \sqrt{\frac{V_{\text{OUT}}}{V_{\text{IN}}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)}$$

The worst-case condition occurs at VIN = 2VOUT, where:

$$I_{CIN} = \frac{I_{OUT}}{2}$$

For simplification, choose an input capacitor with a RMS current rating greater than half of the maximum load current. The input capacitor can be electrolytic, tantalum or ceramic. When using electrolytic or tantalum capacitors, a small, high-quality ceramic capacitor (e.g.  $0.1\mu F$ ) should be placed as close to the IC as possible. When using ceramic capacitors, make sure that they have enough capacitance to provide sufficient charge in order to prevent excessive voltage ripple at the input. The input voltage ripple caused by the capacitance can be estimated by:

$$\Delta V_{\text{IN}} = \frac{I_{\text{OUT}}}{F_{\text{OSC}} \times C_{\text{IN}}} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

### **Output Capacitor Selection**

The output capacitor is required to filter the output and provide load transient current. The higher capacitance value will provide the smaller output ripple and better load transient.

Ceramic electrolytic capacitors with X5R or X7R dielectrics and low ESR are recommended to keep the output voltage ripple low. The output voltage ripple caused by the capacitance can be estimated by:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{F_{\text{OSC}} \times L} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times \left(R_{\text{ESR}} + \frac{1}{8 \times F_{\text{OSC}} \times C_{\text{OUT}}}\right)$$

Where L is the inductor value and  $R_{\text{ESR}}$  is the equivalent series resistance (ESR) value of the output capacitor.

#### **Output Inductor Selection**

The inductance value will determine the inductor ripple current and affects the load transient response and output ripple voltage.

The larger inductance value will result in a smaller ripple current, which will result in a lower output ripple voltage but a slower transient response, while a smaller inductance value will have opposite result.

A good rule is to choose the inductor ripple current that is about 30% of the maximum output current. Use the following equation to derive the inductance value for most designs:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_{L} \times F_{OSC}}$$

Where,  $\Delta I_{L}$  is the inductor-ripple current.

To avoid inductor saturation, the inductor current rating should be at least the converter's maximum output current plus the inductor ripple current. The maximum inductor peak current can be estimated by:

$$I_{L(MAX)} = I_{OUT} + \frac{\Delta I_{L}}{2}$$

In addition, choosing an inductor with a smaller DCR will provide better efficiency, and it is recommended that the inductor's DCR should be less than 15m ohms.

#### **Output Voltage Setting**

The output voltage is set by a resistor voltage divider between output terminal and ground. For detailed voltage divider settings, please refer to "Typical Application Circuits" The output voltage can be calculated as follows:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_{TOP}}{R_{ROT}}\right)$$

# **Application Information (Cont.)**

#### **Layout Consideration**

For all switching power supplies, the layout is an important step in the design; especially at high peak currents and switching frequencies. If the layout is not carefully done, the regulator might show noise problems and duty cycle jitter.

- 1. The VIN input capacitor should be placed close to the VIN and PGND pins. Connecting the capacitor and VIN/PGND pins with short and wide trace without any via holes for good input voltage filtering. The distance between VIN / PGND to capacitor less than 2mm respectively is recommended.

- 2. Place the inductor as close as possible to the LX pin to minimize noise coupling into other circuits.

- 3. The ground of the output capacitor and input capacitor and the PGND of the IC should be as close as possible.

- 4. Place the feedback resistor divider as close as possible to the FB pin to minimize FB high impedance trace. In addition, the FB pin trace cannot be routed close to the switching signal.

- 5. For better heat dissipation, it is strongly recommended to enlarge the thermal pad area as much as possible and place a large ground plane on each PCB layer below the thermal pad position, and place as many vias as possible from the top layer to the bottom layer on the thermal pad and around the ground plane.

- 6. It is recommended to place the input capacitor, output capacitor and inductor on top layer, and use a large power GND plane to connect the ground of the input capacitor, the ground of the output capacitor, and the PGND of the IC.

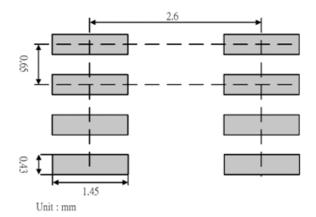

#### **Recommended Minimum Footprint**

#### (Top View)

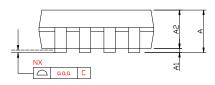

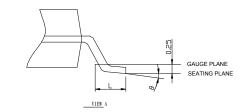

# **Package Information**

**TSOT-23-8A**

| S      |           |         |        |        |  |

|--------|-----------|---------|--------|--------|--|

| SYMBOL | MILL      | IMETERS | INCHES |        |  |

| O<br>L | MIN.      | MAX     | MIN.   | MAX    |  |

| Α      | 0.70      | 1.00    | 0.028  | 0.039  |  |

| A1     | 0.01      | 0.10    | 0.000  | 0.004  |  |

| A2     | 0.70      | 0.90    | 0.028  | 0.035  |  |

| b      | 0.22      | 0.40    | 0.009  | 0.016  |  |

| С      | 0.08      | 0.20    | 0.003  | 0.008  |  |

| D      | 2.70      | 3.10    | 0.106  | 0.122  |  |

| Е      | 2.60      | 3.00    | 0.102  | 0.118  |  |

| E1     | 1.40      | 1.80    | 0.055  | 0.071  |  |

| е      | 0.6       | 5 BSC   | 0.0    | 26 BSC |  |

| e1     | 1. 95 BSC |         | 0.0    | 77 BSC |  |

| L      | 0.30      | 0.60    | 0.012  | 0.024  |  |

| Ф      | 0°        | 8°      | 0°     | 8°     |  |

| aaa    | 0.        | 10      | 0.     | 004    |  |

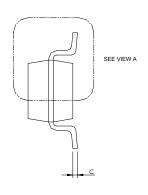

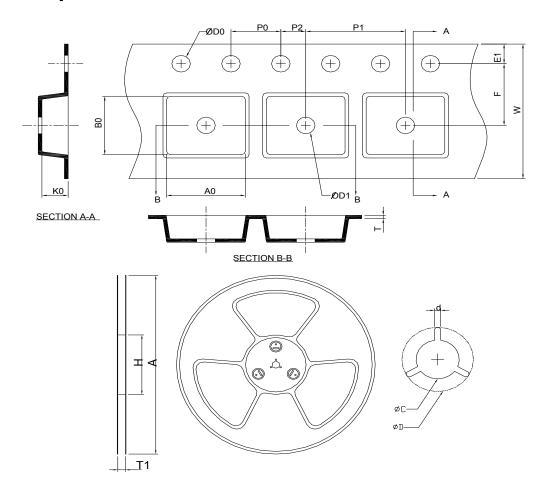

# **Carrier Tape & Reel Dimensions**

| Application  | A          | Н        | T1                | C                  | d        | D                 | W         | E1        | F         |

|--------------|------------|----------|-------------------|--------------------|----------|-------------------|-----------|-----------|-----------|

|              | 178.0±2.00 | 50 MIN.  | 8.4+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 8.0±0.30  | 1.75±0.10 | 3.5±0.05  |

| TSOT 23-8(A) | P0         | P1       | P2                | D0                 | D1       | Т                 | A0        | В0        | K0        |

|              | 4.0±0.10   | 4.0±0.10 | 2.0±0.05          | 1.5+0.10<br>-0.00  | 1.0 MIN. | 0.6+0.00<br>-0.40 | 3.20±0.20 | 3.10±0.20 | 1.20±0.20 |

(mm)

# **Devices Per Unit**

| Package type | Packing     | Quantity |

|--------------|-------------|----------|

| TSOT-23-8(A) | Tape & Reel | 3000     |

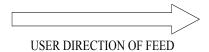

# **Taping Direction Information**

**TSOT-23-8A**

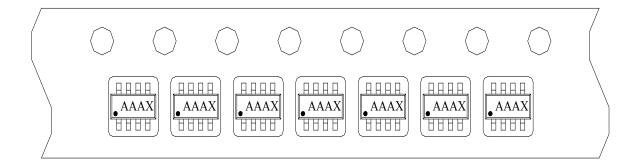

## **Classification Profile**

## **Classification Reflow Profiles**

| Profile Feature                                                                                                  | Sn-Pb Eutectic Assembly            | Pb-Free Assembly                   |

|------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|

| Preheat & Soak Temperature min $(T_{smin})$ Temperature max $(T_{smax})$ Time $(T_{smin}$ to $T_{smax})$ $(t_s)$ | 100 °C<br>150 °C<br>60-120 seconds | 150 °C<br>200 °C<br>60-120 seconds |

| Average ramp-up rate (T <sub>smax</sub> to T <sub>P</sub> )                                                      | 3 °C/second max.                   | 3°C/second max.                    |

| Liquidous temperature (T <sub>L</sub> )<br>Time at liquidous (t <sub>L</sub> )                                   | 183 °C<br>60-150 seconds           | 217 °C<br>60-150 seconds           |

| Peak package body Temperature $(T_p)^*$                                                                          | See Classification Temp in table 3 | See Classification Temp in table 4 |

| Time (t <sub>P</sub> )** within 5°C of the specified classification temperature (T <sub>c</sub> )                | 20** seconds                       | 30** seconds                       |

| Average ramp-down rate (T <sub>p</sub> to T <sub>smax</sub> )                                                    | 6 °C/second max.                   | 6 °C/second max.                   |

| Time 25°C to peak temperature                                                                                    | 6 minutes max.                     | 8 minutes max.                     |

<sup>\*</sup> Tolerance for peak profile Temperature  $(T_p)$  is defined as a supplier minimum and a user maximum.

Table 3. SnPb Eutectic Process – Classification Temperatures (Tc)

| Package   | Volume mm <sup>3</sup> | Volume mm <sup>3</sup> |

|-----------|------------------------|------------------------|

| Thickness | <350                   | ≥350                   |

| <2.5 mm   | 235 °C                 | 220 °C                 |

| ≥2.5 mm   | 220 °C                 | 220 °C                 |

Table 4. Pb-free Process – Classification Temperatures (Tc)

| Package         | Volume mm³ | Volume mm <sup>3</sup> | Volume mm <sup>3</sup> |

|-----------------|------------|------------------------|------------------------|

| Thickness       | <350       | 350-2000               | >2000                  |

| <1.6 mm         | 260 °C     | 260 °C                 | 260 °C                 |

| 1.6 mm – 2.5 mm | 260 °C     | 250 °C                 | 245 °C                 |

| ≥2.5 mm         | 250 °C     | 245 °C                 | 245 °C                 |

# **Reliability Test Program**

| Test item     | Method             | Description                              |

|---------------|--------------------|------------------------------------------|

| SOLDERABILITY | JESD-22, B102      | 5 Sec, 245°C                             |

| HOLT          | JESD-22, A108      | 1000 Hrs, Bias @ T <sub>i</sub> =125°C   |

| PCT           | JESD-22, A102      | 168 Hrs, 100%RH, 2atm, 121°C             |

| TCT           | JESD-22, A104      | 500 Cycles, -65°C~150°C                  |

| HBM           | MIL-STD-883-3015.7 | VHBM ≥ 2KV                               |

| MM            | JESD-22, A115      | VMM ≧ 200V                               |

| Latch-Up      | JESD 78            | $10$ ms, $1$ <sub>tr</sub> $\geq 100$ mA |

<sup>\*\*</sup> Tolerance for time at peak profile temperature (t<sub>o</sub>) is defined as a supplier minimum and a user maximum.

# **APW9114**

## **Customer Service**

**Anpec Electronics Corp.**

Head Office:

No.6, Dusing 1st Road, SBIP, Hsin-Chu, Taiwan, R.O.C.

Tel: 886-3-5642000 Fax: 886-3-5642050

Taipei Branch:

2F, No. 11, Lane 218, Sec 2 Jhongsing Rd., Sindian City, Taipei County 23146, Taiwan

Tel: 886-2-2910-3838 Fax: 886-2-2917-3838