20W Stereo Digital Class-D Audio Power Amplifier with EQ and DRC

### Features

- Operating Voltage: 8.0V~24V for PVDD – 3.0V~3.6V for DVDD and AVDD

- High Efficiency Class-D Operation Eliminate the Need of Heatsinks

- Digital Serial Audio Input (Stereo Output)

- I<sup>2</sup>C Control Interface

- Sampling Rate can Support from 32kHz to 192kHz

- Separated Volume Control from 24dB to Mute

- Soft Mute (50% Duty Cycle)

- Shutdown and Mute Function

- Thermal and Over-Current Protections with Auto-Recovery

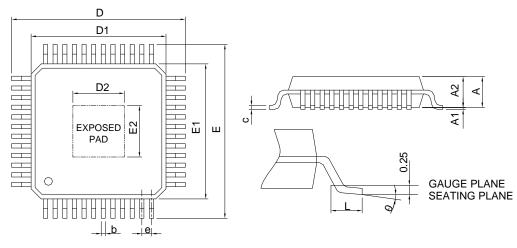

- Space Saving Package TQFP7x7-48P

- Lead Free and Green Devices Available

(RoHS Compliant)

### **General Description**

The APA3163A is a digital input, stereo, high efficiency, Class-D audio amplifier available in a TQFP7x7-48P package.

The APA3163A accepts the digital serial audio data and using the digital audio processor to convert the audio data becomes the stereo Class-D output speaker amplifier. This provides the seamless integration between the codec and the speaker amplifier.

The APA3163A is a slave device receiving clocks from external source, and the Class-D's PWM switching frequency is 352.8kHz for the sampling rate 44.1kHz or 384 kHz for sampling 48kHz, depend on the input signal's sampling rate.

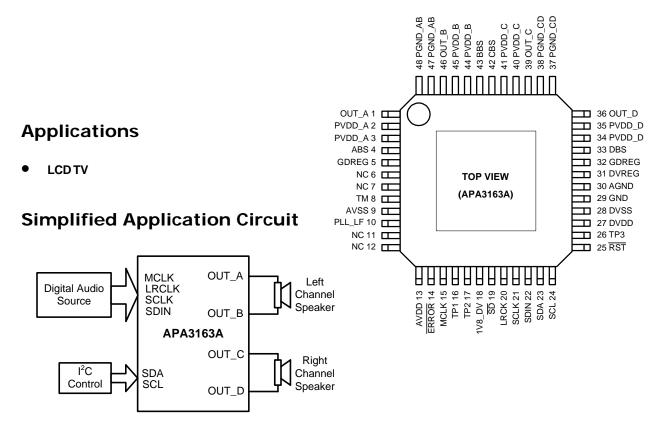

## **Pin Configuration**

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

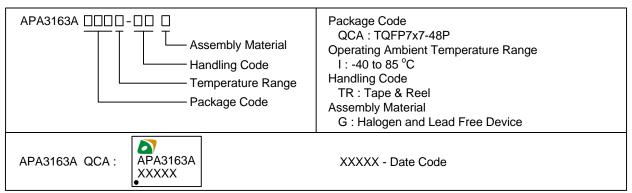

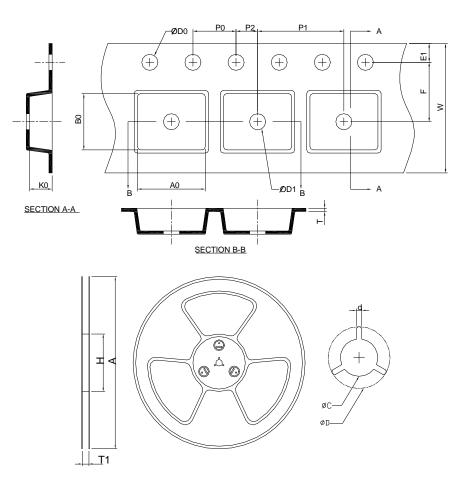

## **Ordering and Marking Information**

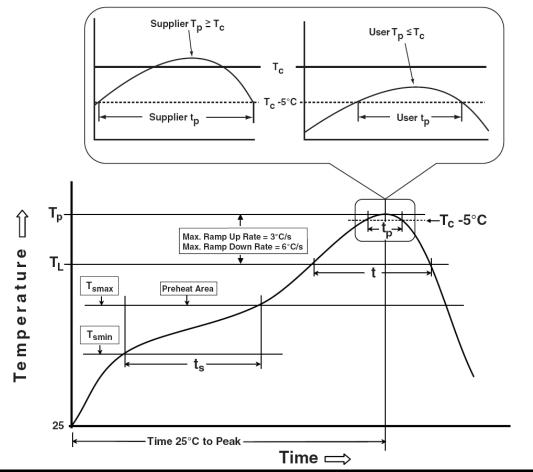

Note : ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or CI does not exceed 900ppm by weight in homogeneous material and total of Br and CI does not exceed 1500ppm by weight).

### Absolute Maximum Ratings (Note 1)

| Symbol    | Parameter                                                    | Rating             | Unit |

|-----------|--------------------------------------------------------------|--------------------|------|

|           | Supply Voltage (PVDD_X to PGND_XX)                           | -0.3 to 26         |      |

|           | Supply Voltage (DVDD to DVSS)                                | -0.3 to 3.6        | ]    |

|           | Supply Voltage (AVDD to AVSS)                                | -0.3 to 3.6        | ]    |

|           | Input Voltage (MCLK to AVSS)                                 | -0.5 to AVDD+2.5   | V    |

|           | Input Voltage (SD, RST, LRCLK, SCLK, SDIN, SDA, SCL to DVSS) | -0.5 to DVDD+2.5   |      |

|           | Input Voltage (OUT_X to PGND_XX)                             | -0.3 to +26        | 1    |

|           | Input Voltage (XBS to PGND_XX)                               | -0.3 to +31        |      |

|           | Input Voltage (AVSS, DVSS, AGND to PGND_XX)                  | -0.3 to +0.3       |      |

| TJ        | Maximum Junction Temperature                                 | 150                | °C   |

| $T_{STG}$ | Storage Temperature Range                                    | -65 to +150        | °C   |

| $T_{SDR}$ | Soldering Temperature Range, 10 seconds                      | 260                | °C   |

| PD        | Power Dissipation                                            | Internally Limited | W    |

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

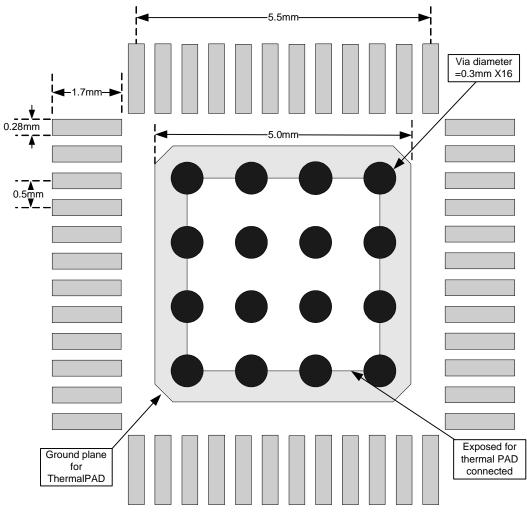

## Thermal Characteristics

| Symbol        | Parameter                                                          | Typical Value | Unit |

|---------------|--------------------------------------------------------------------|---------------|------|

| $\theta_{JA}$ | Junction-to-Ambient Resistance in Free Air (Note 2)<br>TQFP7x7-48P | 25            | °C/W |

Note 2:  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. The exposed pad of TQFP7X7-48P is soldered directly on the PCB.

Note 3: The case temperature is measured at the center of the exposed pad on the underside of the TQFP7X7-48P package.

## **Recommended Operating Conditions**

| Symbol           | Pa                               | rameter                                                                | Rai  | nge  | Unit |

|------------------|----------------------------------|------------------------------------------------------------------------|------|------|------|

| Symbol           | Га<br>                           | Tameter                                                                | Min. | Max. |      |

| V <sub>DD</sub>  | Supply Voltage                   |                                                                        | 3    | 3.6  |      |

| PV <sub>DD</sub> | Full Bridge Stage Supply Voltage | (PVDD_X)                                                               | 8    | 24   |      |

| V <sub>IH</sub>  | High Level Threshold Voltage     | SD, MCLK, LRCLK, SCLK, SDIN,       SDA, SCL, RST                       | 2    | 5    | V    |

| V <sub>IL</sub>  | Low Level Threshold Voltage      | Low Level Threshold Voltage SD, MCLK, LRCLK, SCLK, SDIN, SDA, SCL, RST |      | 1    |      |

| T <sub>A</sub>   | Ambient Temperature Range        |                                                                        | -40  | 85   | °C   |

| TJ               | Junction Temperature Range       | -40                                                                    | 125  |      |      |

| R∟               | Speaker Resistance               | 6                                                                      | -    | Ω    |      |

| Lo               | Output Low Pass Filter Inductant | ce                                                                     | 10   | -    | μH   |

## **PWM Operating Conditions**

| Symbol         | Parameter          | Test Conditions                     | Value | Unit |

|----------------|--------------------|-------------------------------------|-------|------|

|                |                    | 32 kHz Data Rate ±2%                | 256   |      |

| f <sub>S</sub> | Output Sample Rate | 44.1k/88.2k/176.4 kHz Data Rate ±2% | 352.8 | kHz  |

|                |                    | 48k/96k/192 kHz Data Rate ±2%       | 384   |      |

## PLL Input Parameters and External Filter Components

| Symbol            | Parameter                                   | arameter Test Conditions |        | Unit |        |       |

|-------------------|---------------------------------------------|--------------------------|--------|------|--------|-------|

| Symbol            |                                             | Test Conditions          | Min.   | Тур. | Max.   | Unit  |

| f <sub>MCLK</sub> | MCLK Frequency                              |                          | 2.8224 | -    | 24.576 | MHz   |

|                   | MCLK Duty Cycle                             |                          | 40     | 50   | 60     | %     |

| tr/tf (MCLK)      | Rise/Fall Time for MCLK                     |                          | -      | -    | 5      | ns    |

|                   | LRCLK Allowable Drift before<br>LRCLK Reset |                          | -      | -    | 4      | MCLKs |

|                   | External PLL Filter Capacitor C1            | SMD 0603 Y5V             | -      | 47   | -      | nF    |

|                   | External PLL Filter Capacitor C2            | SMD 0603 Y5V             | -      | 4.7  | -      | ПГ    |

|                   | External PLL Filter Resistor R              |                          | -      | 470  | -      | Ω     |

## **Electrical Characteristics**

$T_{A}=25^{\circ}C$ ,  $PV_{DD}=18V$ ,  $V_{DD}=3.3V$  (AVDD and DVDD),  $R_{L}=8\Omega$ , BD Mode,  $f_{S}=48kHz$  (unless otherwise noted)

| Symbol            | Parameter                  | Test Conditions                                                                      |      | APA3163A |      | Unit |  |  |  |  |

|-------------------|----------------------------|--------------------------------------------------------------------------------------|------|----------|------|------|--|--|--|--|

| Symbol            | Faianetei                  |                                                                                      | Min. | Тур.     | Max. | Onit |  |  |  |  |

| DC CHARA          | DC CHARACTERISTICS         |                                                                                      |      |          |      |      |  |  |  |  |

|                   | 3.3V Supply Current (AVDD, | Normal Mode (No load)                                                                | -    | 10       | 20   |      |  |  |  |  |

| I <sub>DD</sub>   | DVDD)                      | Reset (No load)                                                                      | -    | 7.2      | 14.5 | mA   |  |  |  |  |

|                   | Full Bridge Stage Supply   | Normal Mode (No load)                                                                | -    | 18       | 36   | IIIA |  |  |  |  |

| I <sub>PVDD</sub> | Current (PVDD_X)           | Reset (No load)                                                                      | -    | 0.5      | 1    |      |  |  |  |  |

| IIL               | Low Level Input Current    | $V_{\text{I}}\text{<}V_{\text{IL}},V_{\text{DD}}\text{=}3.6\text{V}$ (AVDD and DVDD) | -    | 150      | -    | μA   |  |  |  |  |

## **Electrical Characteristics (Cont.)**

$T_{A}=25^{\circ}C$ ,  $PV_{DD}=18V$ ,  $V_{DD}=3.3V$  (AVDD and DVDD),  $R_{L}=8\Omega$ , BD Mode,  $f_{S}=48kHz$  (unless otherwise noted)

| Cumulant                | Parameter Test Conditions                   |                                                                  |                                              |                       | Unit |      |                   |  |

|-------------------------|---------------------------------------------|------------------------------------------------------------------|----------------------------------------------|-----------------------|------|------|-------------------|--|

| Symbol                  | Parameter                                   | Test Co                                                          | onditions                                    | Min.                  | Тур. | Max. | Unit              |  |

| DC CHARA                | CTERISTICS (CONT.)                          |                                                                  |                                              |                       |      | •    |                   |  |

| I <sub>IH</sub>         | High Level Input Current                    | V <sub>I</sub> >V <sub>IH</sub> , V <sub>DD</sub> =3.6'<br>DVDD) | V (AVDD and                                  | -                     | 150  | -    | μA                |  |

| r <sub>DS(ON)</sub>     | Drain to source resistance,LS               | T <sub>J</sub> =25°C, include resistance                         | es metallization                             | -                     | 180  | -    | mΩ                |  |

| ()                      | Drain to source resistance,HS               | T <sub>J</sub> =25°C, include resistance                         | es metallization                             | -                     | 180  | -    | mΩ                |  |

|                         | Thermal Protection Threshold                |                                                                  |                                              | -                     | 160  | 170  |                   |  |

| T <sub>TP</sub>         | Thermal Protection Threshold<br>Hysteresis  |                                                                  |                                              | -                     | 25   | -    | °C                |  |

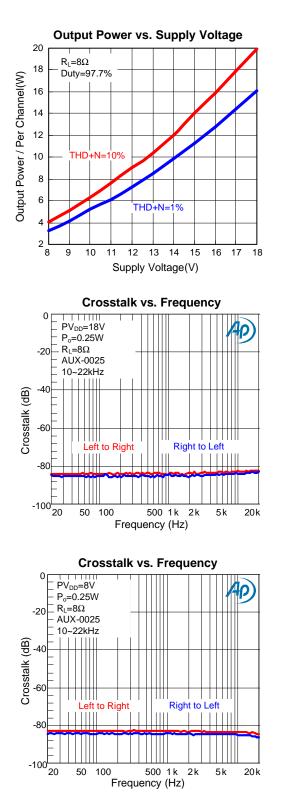

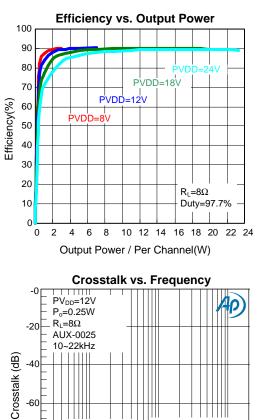

| η                       | Efficiency                                  | Stereo, $R_L=8\Omega$ ,                                          | P <sub>o</sub> =18W                          | -                     | 88   | -    | %                 |  |

| R <sub>OUT</sub>        | Internal Pull-Down Resistance at Each OUT_X |                                                                  |                                              | -                     | 3    | -    | kΩ                |  |

| AC CHARA                | CTERISTICS                                  |                                                                  |                                              |                       |      |      |                   |  |

|                         |                                             | THD+N=1%                                                         | PV <sub>DD</sub> =18V                        | 14.5                  | 16   | -    |                   |  |

|                         |                                             | 1                                                                | f <sub>in</sub> =1kHz,                       | PV <sub>DD</sub> =12V | 6.5  | 7.2  | -                 |  |

|                         |                                             | $R_L=8\Omega$                                                    | PV <sub>DD</sub> =8V                         | 2.9                   | 3.2  | -    |                   |  |

|                         |                                             | THD+N=1%<br>$f_{in}$ =1kHz,<br>$R_L$ =6 $\Omega$                 | PV <sub>DD</sub> =12V                        | 8.1                   | 9    | -    |                   |  |

| Po                      | Output Power                                | THD+N=10%                                                        | PV <sub>DD</sub> =18V                        | -                     | 20   | -    | W                 |  |

|                         |                                             | $f_{in}=1kHz$ ,                                                  | PV <sub>DD</sub> =12V                        | -                     | 9    | -    | 1                 |  |

|                         |                                             | $R_L=8\Omega$                                                    | PV <sub>DD</sub> =8V                         | -                     | 4    | -    | 1                 |  |

|                         |                                             | THD+N=10%<br>$f_{in}$ =1kHz,<br>$R_L$ =6 $\Omega$                | PV <sub>DD</sub> =12V                        | -                     | 11   | -    |                   |  |

|                         |                                             |                                                                  | PV <sub>DD</sub> =18V,<br>P <sub>O</sub> =1W | -                     | 0.06 | -    |                   |  |

| THD+N                   | Total Harmonic Distortion Plus<br>Noise     | f <sub>in</sub> =1kHz,<br>R <sub>L</sub> =8Ω                     | PV <sub>DD</sub> =12V,<br>P <sub>O</sub> =1W | -                     | 0.13 | -    | %                 |  |

|                         |                                             | PV <sub>c</sub><br>Po=                                           |                                              | -                     | 0.2  | -    | 1                 |  |

| Crosstalk               | Channel Separation                          | $P_0=0.25W, R_L=8\Omega, f_{in}=1kHz$                            |                                              | -                     | -82  | -    |                   |  |

| Att <sub>Mute</sub>     | Mute Attenuation                            | $f_{in}=1kHz, R_L=8\Omega, V_O=1V_{rms}$                         |                                              | -                     | -70  | -    | 1                 |  |

| Att <sub>shutdown</sub> | Shutdown Attenuation                        | $f_{in}=1kHz, R_L=8\Omega, V_O=1V_{rms}$                         |                                              | -                     | -110 | -    | dB                |  |

| S/N                     | Signal to Noise Ratio                       | R <sub>L</sub> =8Ω, P <sub>O</sub> =16W<br>A-Weighting Filt      | -                                            | 97                    | -    | ]    |                   |  |

| Vn                      | Noise Output Voltage                        | With A-Weightin                                                  | ng Filter (A <sub>v</sub> =0dB)              | -                     | 150  | -    | μV <sub>rms</sub> |  |

## Serial Audio Ports Slave Mode

Over recommended operating conditions (unless otherwise noted)

| Symbol              | Parameter                                      | Test Conditions      |       | APA3163A | 1      | Unit |

|---------------------|------------------------------------------------|----------------------|-------|----------|--------|------|

| Symbol              | Farameter                                      | Test Conditions      |       | Тур.     | Max.   | Unit |

| f <sub>SCLK</sub>   | Frequency, SCLK $32xf_S$ , $48xf_S$ , $64xf_S$ | C <sub>L</sub> =30pF | 1.024 | -        | 12.288 | MHz  |

| t <sub>Setup1</sub> | Setup Time, LRCLK to SCLK<br>Rising Edge       |                      | 10    | -        | -      | 2    |

| t <sub>Hold1</sub>  | Hold Time, LRCLK to SCLK<br>Rising Edge        | 10                   |       |          | -      | ns   |

## Serial Audio Ports Slave Mode

Over recommended operating conditions (unless otherwise noted)

| Cumphiel              | Parameter                                                    | Test Conditions |      | APA3163/ | ۹.   | Unit           |

|-----------------------|--------------------------------------------------------------|-----------------|------|----------|------|----------------|

| Symbol                | Parameter Test Conditions                                    | Test Conditions | Min. | Тур.     | Max. | Unit           |

| t <sub>Setup2</sub>   | Setup Time, SDIN to SCLK<br>Rising Edge                      |                 | 10   | -        | -    |                |

| t <sub>Hold</sub>     | Hold Time, SDIN to SCLK Rising<br>Edge 10                    |                 |      |          |      | ns             |

|                       | LRCLK Frequency 8K 48K 4                                     |                 | 48K  | kHz      |      |                |

|                       | LRCLK Duty Cycle                                             |                 | 40   | 50       | 60   | %              |

|                       | SCLK Duty Cycle                                              |                 | 40   | 50       | 60   | %              |

|                       | SCLK Rising Edges Between<br>LRCLK Riding Edges              |                 | 32   | 32 - 64  |      | SCLK<br>edges  |

| t <sub>(edge)</sub>   | LRCLK Clock Edge With Respect<br>To The Falling Edge of SCLK |                 | -1/4 | -        | 1/4  | SCLK<br>period |

| tr/tf<br>(SCLK/LRCLK) | Rise/Fall Time for SCLK/LRCLK                                |                 | 8    |          |      | ns             |

## **Reset Timing**

Control signal parameters over recommended operating conditions (unless otherwise noted). Please refer to "Recommended Use Model" section on usage of all terminals.

| Symbol Parameter        |                                 | Test Conditions |      | APA3163A |      | Unit  |

|-------------------------|---------------------------------|-----------------|------|----------|------|-------|

| Symbol                  | Falameter                       | Test conditions | Min. | Тур.     | Max. | Offic |

| $t_{p(\overline{RST})}$ | Pulse Duration, RST Active.     | No Load         | 100  | -        | -    | μs    |

| $t_{d(12C\_Ready)}$     | Time to Enable I <sup>2</sup> C |                 | -    | -        | 13.5 | ms    |

# I<sup>2</sup>C Serial Control Port Operation

Timing characteristics for I<sup>2</sup>C Interface signals over recommended operating conditions (unless otherwise noted)

| Cumhal              | Deveryorien                                       | Test Canditions |           | APA3163/ | 4    | 11   |

|---------------------|---------------------------------------------------|-----------------|-----------|----------|------|------|

| Symbol              | Parameter                                         | Test Conditions | Min. Typ. |          | Max. | Unit |

| f <sub>SCL</sub>    | Frequency, SCL                                    | No Wait States  | -         | -        | 400  | kHz  |

| t <sub>W(H)</sub>   | Pulse Duration, SCL High                          |                 | 0.6       | -        | -    |      |

| t <sub>W(L)</sub>   | Pulse Duration, SCL Low                           |                 | 1.3       | -        | -    | μs   |

| tr                  | Rise Time, SCL and SDA                            |                 | -         | -        | 300  |      |

| t <sub>f</sub>      | Fall Time, SCL and SDA                            |                 | -         | -        | 300  |      |

| t <sub>setup1</sub> | Setup Time, SCL to SDA                            |                 | 100       | -        | -    | ns   |

| t <sub>hold1</sub>  | Hold Time, SCL to SDA                             |                 | 0         | -        | -    |      |

| t <sub>(buf)</sub>  | Bus Free Time Between Stop<br>and Start Condition |                 | 1.3       | -        | -    |      |

| t <sub>setup2</sub> | Setup Time, SCL to Start<br>Condition             |                 | 0.6       | -        | -    | μs   |

| t <sub>hold2</sub>  | Hold Time, Start condition to SCL                 |                 | 0.6       | -        | -    |      |

| t <sub>setup3</sub> | Setup Time, SCL to Stop<br>Condition 0.6          |                 | -         |          |      |      |

| CL                  | Load Capacitance for Each Bus<br>Line             |                 | -         | -        | 400  | pF   |

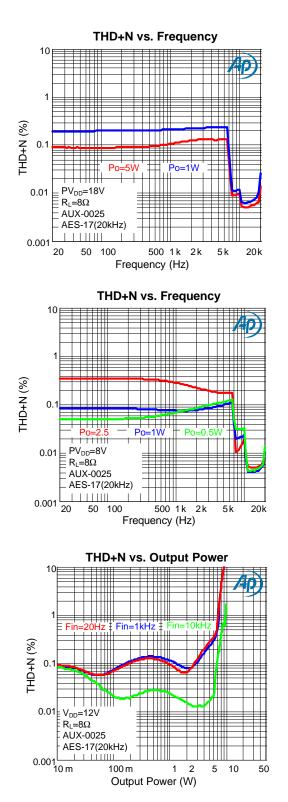

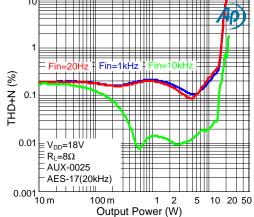

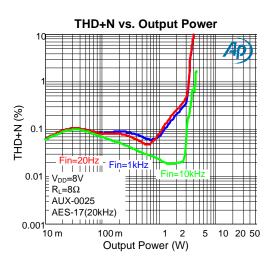

## **Typical Operating Characteristics**

**THD+N vs. Frequency** 10 Ħ 1 THD+N (%) 0.1 Po=0.5W ++++++++PV<sub>DD</sub>=12V 0.01  $R_L = 8\Omega$ AUX-0025 AES-17(20kHz) 0.001 20 50 100 500 1 k 2 k 5k 20k Frequency (Hz) THD+N vs. Output Power 10 p 1111

Copyright  $\circledcirc$  ANPEC Electronics Corp. Rev. A.1 - Mar., 2013

## **Typical Operating Characteristics (Cont.)**

Frequency (Hz)

Copyright  $\circledcirc$  ANPEC Electronics Corp. Rev. A.1 - Mar., 2013

# **Pin Description**

| P      | IN      |       |                                                                                                                                                                           |

|--------|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.    | NAME    | I/O/P | FUNCTION                                                                                                                                                                  |

| 1      | OUT_A   | 0     | Output of half bridge A.                                                                                                                                                  |

| 2, 3   | PVDD_A  | Р     | Power supply for half bridge A.                                                                                                                                           |

| 4      | ABS     | I/O   | High side bootstrap supply for half bridge A.                                                                                                                             |

| 5, 32  | GDREG   | O/P   | Internal regulator output of gate driver.                                                                                                                                 |

| 6      | NC      | -     | No connection.                                                                                                                                                            |

| 7      | NC      | -     | No connection.                                                                                                                                                            |

| 8      | ТМ      | I     | Test mode digital input pin.                                                                                                                                              |

| 9, 11  | AVSS    | Р     | Analog power supply's ground.                                                                                                                                             |

| 10     | PLL_LF  | 0     | PLL negative loop filter pin.                                                                                                                                             |

| 12     | 2V5_AV  | O/P   | Internal regulated 2.5V for analog block's supply, Not for power external device.                                                                                         |

| 13     | AVDD    | Р     | Analog powers supply and connects to 3.3V.                                                                                                                                |

| 14     | ERROR   | 0     | When over temperature, over current over voltage and under voltage occur, this pin will be pull low; and it will be reset to high when the fault condition has be remove. |

| 15     | MCLK    | I     | Master clock input.                                                                                                                                                       |

| 16     | TP1     | I/O   | Test mode digital input/output pin.                                                                                                                                       |

| 17     | TP2     | I/O   | Test mode digital input/output pin.                                                                                                                                       |

| 18     | 1V8_DV  | O/P   | Internal regulated 1.8V for digital block's supply, Not for power external device.                                                                                        |

| 19     | SD      | 1     | Active LOW, Shutting down the noise shaper and initiating PWM stop sequence.                                                                                              |

| 20     | LRCLK   | I     | Input serial audio data left/right clock. (Sample rate clock), it's weak pull down terminal.                                                                              |

| 21     | SCLK    | I     | Serial audio data clock (shift clock). SCLK is the serial audio port input data bit clock.                                                                                |

| 22     | SDIN    | I     | Serial audio data input.                                                                                                                                                  |

| 23     | SDA     | 10    | l <sup>2</sup> C serial control data interface input/output.                                                                                                              |

| 24     | SCL     | I     | I <sup>2</sup> C serial control clock input.                                                                                                                              |

| 25     | RST     | I     | Reset control, place a logic low to this pin, will reset the APA3163A to its default condition. It's weak pull-up terminal.                                               |

| 26     | TP3     | I/O   | Test mode digital input/output pin.                                                                                                                                       |

| 27     | DVDD    | Р     | Digital powers supply and connects to 3.3V.                                                                                                                               |

| 28     | DVSS    | Р     | Digital power supply's ground.                                                                                                                                            |

| 29     | GND     | Р     | Power stage's analog ground.                                                                                                                                              |

| 30     | AGND    | Р     | Power stage's analog ground.                                                                                                                                              |

| 31     | DVREG   | O/P   | Digital voltage regulator's output, only for internal used.                                                                                                               |

| 33     | DBS     | I/O   | High side bootstrap supply for half bridge D.                                                                                                                             |

| 34, 35 | PVDD_D  | Р     | Power supply for half bridge D.                                                                                                                                           |

| 36     | OUT_D   | 0     | Output of half bridge D.                                                                                                                                                  |

| 37, 38 | PGND_CD | Р     | Power Ground connection for half bridge C and D.                                                                                                                          |

| 39     | OUT_C   | 0     | Output of half bridge C.                                                                                                                                                  |

| 40, 41 | PVDD_C  | Р     | Power supply for half bridge C.                                                                                                                                           |

| 42     | CBS     | I/O   | High side bootstrap supply for half bridge C.                                                                                                                             |

| 43     | BBS     | I/O   | High side bootstrap supply for half bridge B.                                                                                                                             |

## Pin Description (Cont.)

| Р      | IN      | I/O/P | FUNCTION                                         |  |  |  |

|--------|---------|-------|--------------------------------------------------|--|--|--|

| NO.    | NAME    | 1/0/F | FUNCTION                                         |  |  |  |

| 44, 45 | PVDD_B  | Р     | Power supply for half bridge B.                  |  |  |  |

| 46     | OUT_B   | 0     | Output of half bridge B.                         |  |  |  |

| 47, 48 | PGND_AB | Р     | Power Ground connection for half bridge A and B. |  |  |  |

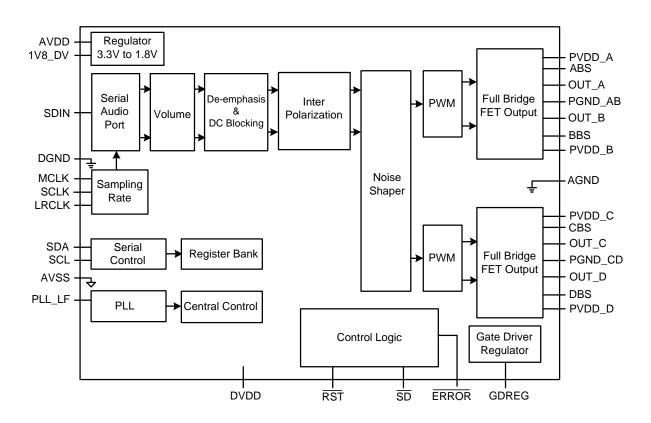

## **Block Diagram**

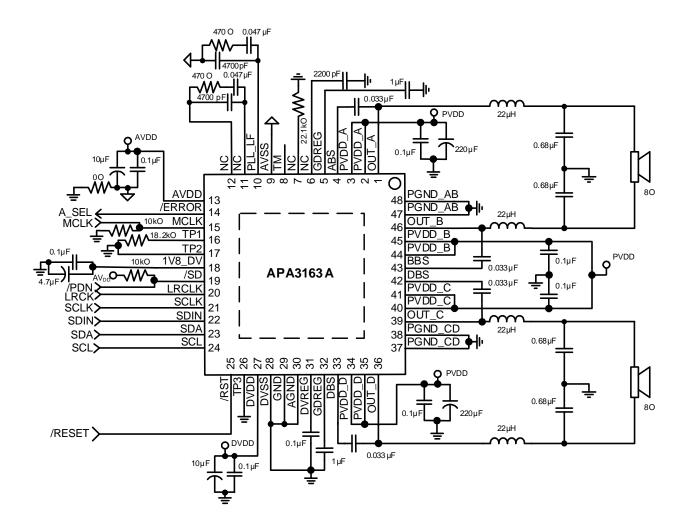

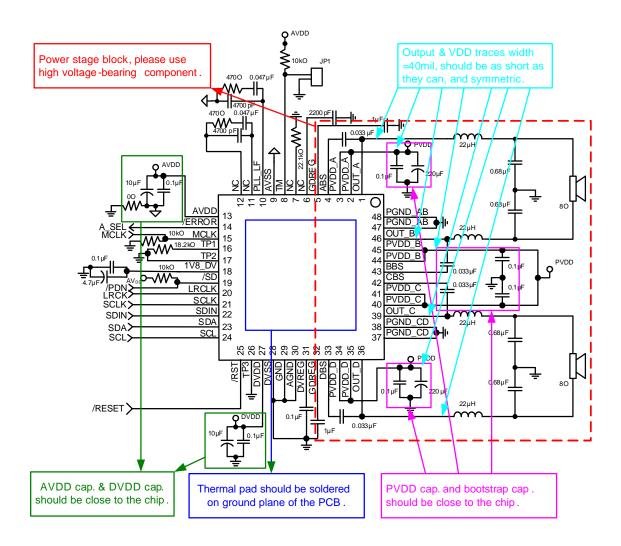

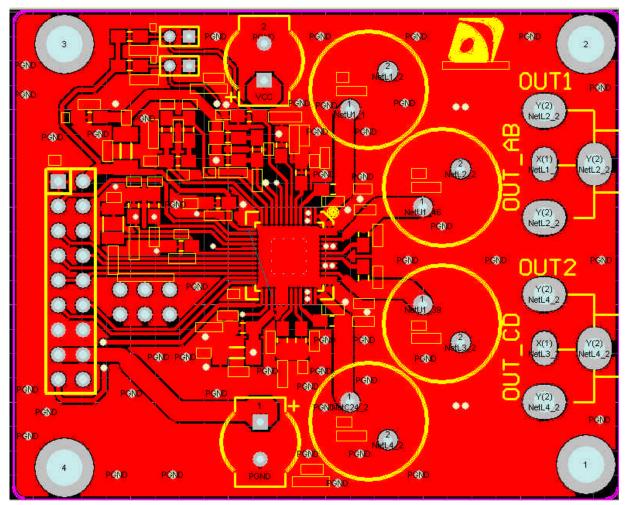

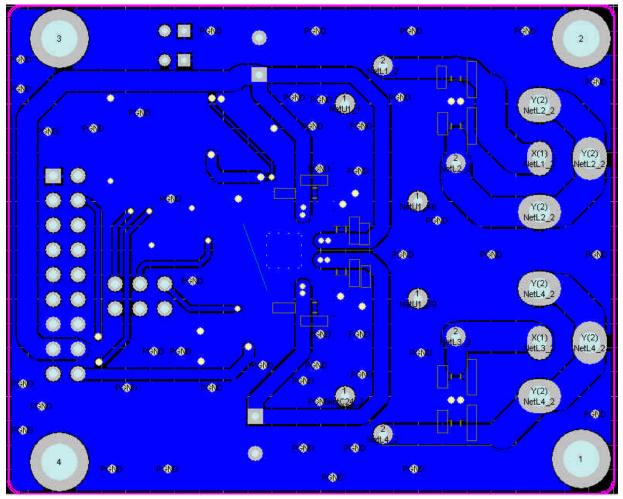

# **Typical Application Circuit**

## **Function Description**

### **Clock And PLL**

The APA3163A is a slave device and receives signals from MCLK, SCLK, and LRCLK. The digital audio processor (DAP) provides all sample rates and MCLK rates which defined in the clock control register.

The APA3163A checks to verify that SCLK is a particular value of  $32f_s$ ,  $48f_s$ , or  $64f_s$ . The DAP only provides a  $1 \times f_s$  LRCLK. The timing relationship of these clocks to SDIN is shown in subsequent sections.

#### Serial Data Interface

Serial data is an input transmitted to SDIN. The PWM outputs are derived from SDIN. Besides, the APA3163A DAP receives left-justified, right-justified, and I<sup>2</sup>S serial data formats with 16, 20, or 24 bit.

#### **PWM Section**

The APA3163A DAP device is a high power efficiency and high-performance digital audio reproduction. A noise shaper is used to increase dynamic range and SNR in the audio band. The PWM section receives 24bit PCM data from the DAP and outputs two BTL PWM audio output channels.

The PWM section has individual channel dc blocking filters that can be enabled and disabled. The low pass filter cutoff frequency is less than 1Hz. Besides, the PWM section includes individual channel de-emphasis filters for 44.1 and 48 kHz and can be enabled and disabled.

The adjustable maximum modulation limit of PWM section is from 93.8% to 98.4%.

#### I<sup>2</sup>C Compatible Serial Control Interface

The APA3163A DAP receives commands from a system controller through an I<sup>2</sup>C serial control slave interface. The serial control interface supports both normal-speed 100kHz and high-speed 400kHz operations without waiting states. As an added feature, even though the MCLK is absent, the interface operates.

For status registers, the serial control interface provides both single-byte and multi-byte read and write operations; and for the general control registers, they associated with the PWM.

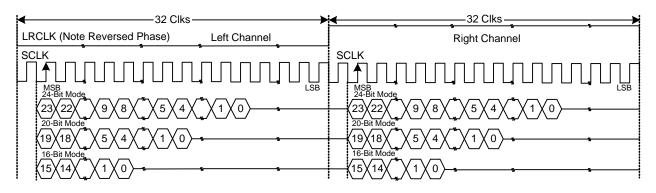

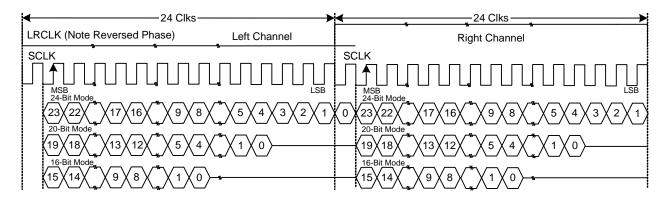

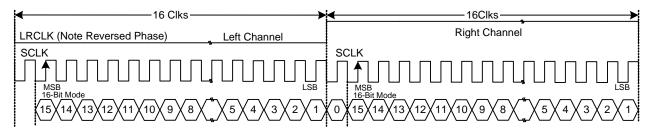

#### Serial Interface Control And Timing I<sup>2</sup>S Timing

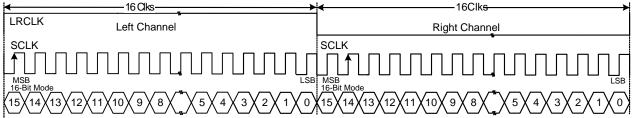

I<sup>2</sup>S timing uses LRCLK to define the data for the left channel and the right channel when the data being transmitted. For the left channel, the LRCLK is low; for the right channel, the LRCLK is high. A bit clock running at 32, 48, or  $64 \times f_s$  is used to clock in the data. When the LRCLK signal changes state, there is a delay of one bit clock from the time which the first bit of data on the data lines. The data is written MSB first and is valid on the rising edge of bit clock. The DAP masks unused trailing data bit positions.

Figure 1. I<sup>2</sup>S 64 f<sub>s</sub> Format

Figure 2. I<sup>2</sup>S 48 f<sub>s</sub> Format

Figure 3. I<sup>2</sup>S 32 f<sub>s</sub> Format

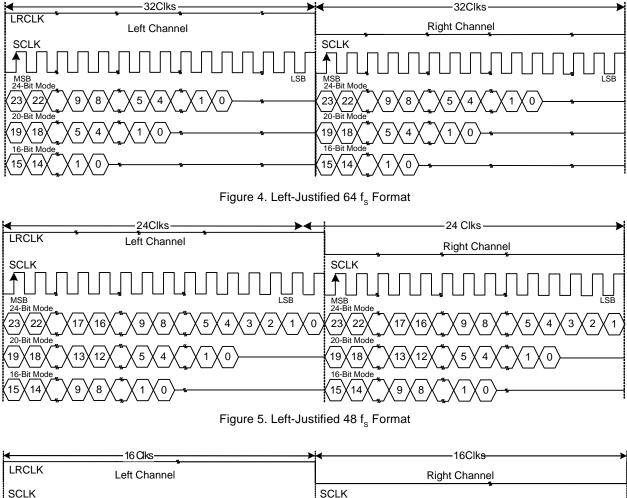

### Left-Justified

Left-justified (LJ) timing uses LRCLK to define the data for the left channel and the right channel when the data being transmitted. For the left channel, the LRCLK is high; for the right channel, the LRCLK is low. A bit clock running at 32, 48, or  $64 \times f_s$  is used to clock in the data. The first bit of data appears on the data lines when LRCLK toggles. The data is written MSB first and is valid on the rising edge of the bit clock. The DAP masks unused trailing data bit positions.

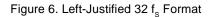

### **Right-Justified**

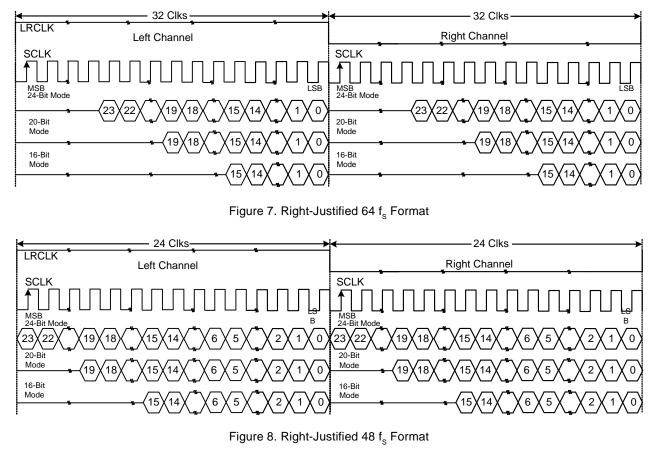

Right-justified (RJ) timing uses LRCLK to define the data for the left channel and the right channel when the data being transmitted. For the left channel, the LRCLK is high; for the right channel, the LRCLK low. A bit clock running at 32, 48, or 64  $\times$  f<sub>s</sub> is used to clock in the data. After LRCLK toggles, for 24bit data, the first bit of data appears on the data 8 bit-clock. In RJ mode, the LSB of data is always clocked by the last bit clock before LRCLK transitions. The data is written MSB first and is valid on the rising edge of bit clock. The DAP masks unused leading data bit positions.

Figure 9. Right-Justified 32 f<sub>s</sub> Format

#### I<sup>2</sup>C Serial Control Interface

The APA3163A DAP has a bidirectional I<sup>2</sup>C interface that compatible with the I<sup>2</sup>C (Inter IC) bus protocol. Besides, it provides both 100kHz and 400kHz data transfer rates to single and multiple bytes write and read operations.

This is a slave only device, and it doesn't support a multi-master bus environment or wait state insertion. The function of the control interface is to read device status and to program the registers of the device.

The DAP supports the standard-mode I<sup>2</sup>C bus operation (100kHz maximum) and the fast I<sup>2</sup>C bus operation (400kHz maximum). Without I<sup>2</sup>C wait cycles, the DAP performs I<sup>2</sup>C operations.

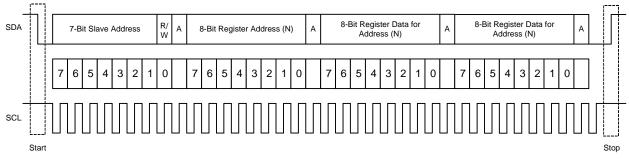

#### General I<sup>2</sup>C Operation

The I<sup>2</sup>C bus uses SDA (data) and SCL (clock) to communicate between integrated circuits in a system. Data is transferred on the bus serially one bit at a time. With the most significant bit (MSB) transferred first, the address and data can be transferred in byte (8bit) format. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus.

The bus uses transitions on the SDA when the clock is high to indicate start and stop conditions. A high-to-low transition on SDA indicates a start, and a low-to-high transition indicates a stop. Normal data bit transitions must occur within the low time of the clock. These conditions are shown in Figure 10. The master generates the 7bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The APA3163A holds SDA low during the acknowledge clock to indicate an acknowledgment. When this occurs, the master transmits the next byte of the sequence.

Each device is addressed by a unique 7bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. An external pull-up resistor must be used for the SDA and SCL signals to set the high level for the bus.

#### Figure 10. Typical I<sup>2</sup>C Sequence

There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. A generic data transfer sequence is shown in Figure 10.

The 7bit address for APA3163A is 0011 010 (0x34). APA3163A address can be changed from 0x34 to 0x38 by writing 0x38 to device address register 0xF9.

#### Single- and Multiple-Byte Transfers

The serial control interface supports single-byte and multiple-byte (R/W) operations for sub-addresses 0x00 to 0x1F. However, for the sub-addresses 0x20 to 0xFF, the serial control interface supports only multiple-byte read/write operations (in multiples of 4 bytes).

During multiple-byte read operations, the DAP responds with data, a byte at a time, starting at the sub-address assigned, as long as the master device continues to respond with acknowledges. If a particular sub-address does not contain 32 bits, the unused bits are read as logic 0.

During multiple-byte write operations, the DAP compares the number of bytes transmitted to the number of bytes that are required for each specific sub-address.

Supplying a sub-address for each sub-address transaction is referred to as random I<sup>2</sup>C addressing. The APA3163A also supports sequential I<sup>2</sup>C addressing. For write transactions, if a sub-address is issued and followed by data for that sub-address and the 15 sub-addresses that follow, a sequential I<sup>2</sup>C write transaction has taken place, and the data for all 16 sub-addresses is successfully received by the APA3163A. For I<sup>2</sup>C sequential write transactions, the sub-address then serves as the start address, and the amount of data subsequently transmitted, before a stop or start is transmitted, determines how many sub-addresses are written. As was true for random addressing, sequential addressing requires that a complete set of data be transmitted. If only a partial set of data is written to the last sub-address, the data for the last sub-address is discarded. However, if all other data written is accepted, only the incomplete data is discarded.

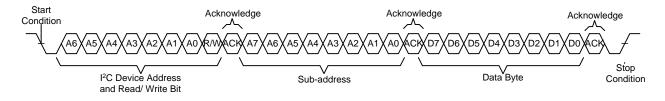

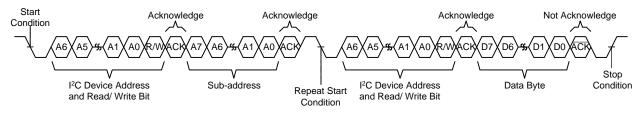

#### Single-Byte Write

As shown in Figure 11, a single-byte data write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the R/W bit. The R/W bit determines the direction of the data transfer. For a write data transfer, the R/W bit will be a 0. After receiving the correct I<sup>2</sup>C device address and the R/W bit, the DAP responds with an acknowledge bit. And then, the master transmits the address byte or bytes corresponding to the APA3163A internal memory address being accessed. After receiving the address byte, the APA3163A responds with an acknowledge bit again. Next, the master device transmits the data byte to be written to the memory address being accessed. After receiving the data byte to be written to the memory address being accessed. After receiving the data byte to be written to the memory address being accessed. After receiving the data byte to be written to the memory address being accessed. After receiving the data byte to be written to the memory address being accessed. After receiving the data byte to be written to the memory address being accessed. After receiving the data byte to be written to the memory address being accessed. After receiving the data byte to be written to the memory address being accessed. After receiving the data byte to be written to the memory address being accessed.

Figure 11. Single-Byte Write Transfer

#### **Multiple-Byte Write**

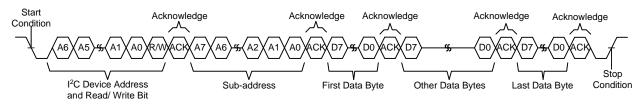

A multiple-byte data write transfer is identical to a single-byte data write transfer except that multiple data bytes are transmitted by the master device to the DAP as shown in Figure 12. After receiving each data byte, the APA3163A responds with an acknowledge bit.

Figure 12. Multiple-Byte Write Transfer

#### Single-Byte Read

As shown in Figure 13, a single-byte data read transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the R/W bit. For the data read transfer, both a write followed by a read are actually done. Initially, a write is done to transfer the address byte or bytes of the internal memory address to be read. As a result, the R/W bit becomes a 0. After receiving the APA3163A address and the read/write bit, APA3163A responds with an acknowledge bit. Besides, after sending the internal memory address byte or bytes, the master device transmits another start condition followed by the APA3163A address and the read/write bit again. This time the read/ write bit becomes a 1, indicating a read transfer. After receiving the address and the read/write bit, the APA3163A again responds with an acknowledge bit. And then, the APA3163A transmits the data byte from the memory address being read. After receiving the data byte, the master device transmits a not acknowledge followed by a stop condition to complete the single byte data read transfer.

Figure 13. Single-Byte Read Transfer

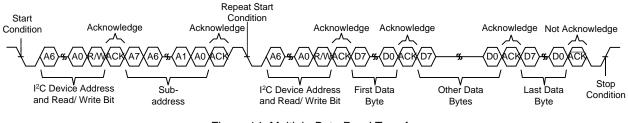

#### **Multiple-Byte Read**

A multiple-byte data read transfer is identical to a single-byte data read transfer except that multiple data bytes are transmitted by the APA3163A to the master device as shown in Figure 14. Except for the last data byte, the master device responds with an acknowledge bit after receiving each data byte.

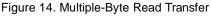

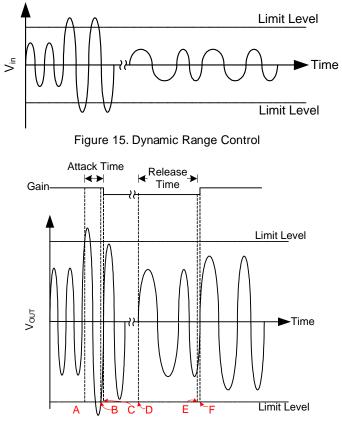

### Dynamic Range Control (DRC)

The DRC scheme has a single threshold, offset, and slope (all programmable). There is one ganged DRC for the left/ right channels.

The DRC input/output diagram is shown in Figure 15.

Figure 16. DRC Structure

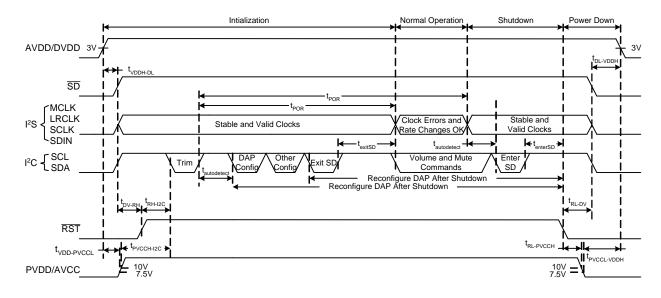

### **Recommended Use Model**

| Figure 17. Recommended Command Sequence |

|-----------------------------------------|

|-----------------------------------------|

| Deremeter               | Description                                                                                                                                                              |                                   | APA3163/ | 4    | l lm i t |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------|------|----------|

| Parameter               | Description                                                                                                                                                              | Min.                              | Тур.     | Max. | Unit     |

| $t_{VDDH-DL}$           | Time digital inputs must remain low after AVDD/DVDD goes above 3V                                                                                                        | 0                                 | -        | -    |          |

| $t_{\text{DL-VDDH}}$    | Time digital inputs must be low before AVDD/DVDD goes below 3V                                                                                                           | 0                                 | -        | -    |          |

| $t_{\text{VDDH-PVDDL}}$ | Time PVDD/AVCC remains below 7.5V after AVDD/DVDD goes above 3V                                                                                                          | 100                               | -        | -    |          |

| $t_{PVDDL-VDDH}$        | Time PVDD/AVCC must be below 7.5V before AVDD/DVDD goes below 3V                                                                                                         | 0                                 | -        | -    | μs       |

| t <sub>PVDDH-I2C</sub>  | Time PVDD/AVCC must be above 10V before I <sup>2</sup> C commands may address device                                                                                     | 10                                | -        | -    |          |

| t <sub>RL-PVDDH</sub>   | Time PVDD/AVCC must remain above 10V after RST goes low                                                                                                                  | 2                                 | -        | -    |          |

| t <sub>RH-I2C</sub>     | Time RESET must be high before I <sup>2</sup> C commands may address device                                                                                              | 13.5                              | -        | -    | ms       |

| t <sub>DV-RH</sub>      | Time digital inputs must be valid (driven as recommended) before RST goes high                                                                                           | 100                               | -        | -    |          |

| t <sub>RL-DV</sub>      | Time digital inputs must remain valid (driven as recommended) after $\overline{RST}$ goes low                                                                            | 2                                 | -        | -    | μs       |

| t <sub>autodetect</sub> | Auto-detect completion wait time (given stable and valid clocks) before issuing further commands                                                                         | 50                                | -        | -    |          |

| t <sub>exitSD</sub>     | Exit shutdown wait time before issuing further commands to device (t start given by register 0x1A)                                                                       | 1+1.3 x<br>t <sub>start</sub>     | -        | -    | ]        |

| t <sub>enterSD</sub>    | Enter shutdown wait time before issuing further commands to device (t stop given by register 0x1A)                                                                       | 1+1.3 x<br>t <sub>stop</sub>      | -        | -    | - ms     |

| t <sub>POR</sub>        | Power-on-reset wait time after 1st trim following AVDD/DVDD power-up ( $t_{start}$ given by register 0x1A) (does not apply to trim commands following subsequent resets) | 240 +<br>1.3 x t <sub>start</sub> | -        | -    |          |

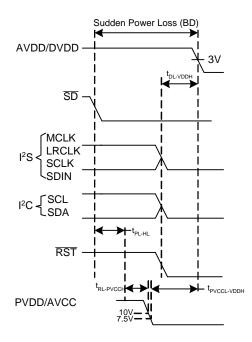

Recommended Use Model (Cont.)

Figure 18. Power Loss Sequence

| Parameter               | Description                                                                                   |      | Unit |      |      |

|-------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

| Farameter               | Description                                                                                   | Min. | Тур. | Max. | Unit |

| t <sub>RL-DV</sub>      | Time digital inputs must remain valid (driven as recommended) after $\overline{RST}$ goes low | 2    | -    | -    |      |

| t <sub>DL-VDDH</sub>    | Time digital inputs must be low before AVDD/DVDD goes below 3V                                | 0    | -    | -    |      |

| t <sub>RL-PVDDH</sub>   | Time PVDD/AVCC must remain above 10V after RST goes low                                       | 2    | -    | -    | μs   |

| t <sub>PVDDL-VDDH</sub> | Time PVDD/AVCC must be below 7.5V before AVDD/DVDD goes below 3V                              | 0    | -    | -    |      |

#### **Recommended Command Sequences**

The DAP has two groups of commands. One set is for configuration and is intended for use only during initialization. The other set has built-in click and pop protection and may be used during normal operation while audio is streaming. The following supported command sequences illustrate how to initialize, operate, and shutdown the device.

#### Initialization Sequence

Use the following sequence to power-up and initialize the device:

- 1. Hold all digital inputs low and ramp up AVDD/DVDD to at least 3V.

- 2. Initialize digital inputs and PVDD supply as follows:

- Drive  $\overline{RST}=0$ ,  $\overline{SD}=1$ , and other digital inputs to their desired state while ensuring that all are never more than 2.5V above AVDD/DVDD. Provide stable and valid I<sup>2</sup>S clocks (MCLK, LRCLK, and SCLK). Wait at least 100µs, drive  $\overline{RST}=1$ , and wait at least another 13.5ms.

- Ramp up PVDD to at least 8V while ensuring that it remains below 6V for at least 100µs after AVDD/DVDD reaches 3V. Then wait at least another 10µs.

- 3. Configure the DAP via I<sup>2</sup>C (see Users's Guide for typical values): DRC parameters (0x46, and 0x60~62).

- 4. Configure remaining registers.

- 5. Exit shutdown (sequence defined below).

### **Normal Operation**

The following are the only events supported during normal operation:

- (a) Writes to master/channel volume registers

- (b) Writes to soft mute register

- (c) Enter and exit shutdown (sequence defined below)

- (d) Clock errors and rate changes

Note: Events (c) and (d) are not supported for 240ms+1.3xt<sub>0</sub> 0after trim following AVDD/DVDD power up ramp (where Tstart is specified by register 0x1A).

### Shutdown Sequence

Enter:

1. Ensure  $I^2S$  clocks have been stable and valid for at least 50ms.

2. Write 0x40 to register 0x05.

3. Wait at least  $1ms+1.3xt_{stoo}$  (where  $t_{stoo}$  is specified by register 0x1A).

4. Once in shutdown, stable clocks are not required while device remains idle.

5. If desired, reconfigure by ensuring that clocks have been stable and valid for at least 50ms before returning to step 4 of initialization sequence.

Exit:

1. Ensure  $\mathsf{I}^2\mathsf{S}$  clocks have been stable and valid for at least 50ms.

2. Write 0x00 to register 0x05 (exit shutdown command may not be serviced for as much as 240ms after trim following AVDD/DVDD powerup ramp).

3. Wait at least  $1ms+1.3xt_{start}$  (where  $t_{start}$  is specified by register 0x1A).

4. Proceed with normal operation.

### Power-down Sequence

Use the following sequence to power-down the device and its supplies:

1. If time permits, enter shutdown (sequence defined above); else, in case of sudden power loss, assert  $\overline{SD}=0$  and wait at least 2ms.

- 2. Assert RST=0.

- 3. Drive digital inputs low and ramp down PVDD supply as follows:

- Drive all digital inputs low after  $\overline{RST}$  has been low for at least 2µs.

- Ramp down PVDD while ensuring that it remains above 8V until RST has been low for at least 2µs.

4. Ramp down AVDD/DVDD while ensuring that it remains above 3V until PVDD is below 6V and that it is never more than 2.5V below the digital inputs.

| Sub Address | Register Name                 | No. of Bytes | Contents                                | Initialization Values |

|-------------|-------------------------------|--------------|-----------------------------------------|-----------------------|

|             |                               |              | A u indicates unused bits.              |                       |

| 0x00        | Clock control register        | 1            | Description shown in subsequent section | 0x6C                  |

| 0x01        | Device ID register            | 1            | Description shown in subsequent section | 0x00                  |

| 0x02        | Error status register         | 1            | Description shown in subsequent section | 0x00                  |

| 0x03        | System control register 1     | 1            | Description shown in subsequent section | 0x80                  |

| 0x04        | Serial data interface         | 1            | Description shown in subsequent section | 0x05                  |

| 0x05        |                               | 1            | Description shown in subsequent section | 0x40                  |

| 0x06        | Soft mute register            | 1            | Description shown in subsequent section | 0x00                  |

| 0x07        | Master volume                 | 1            | Description shown in subsequent section | 0xFF (mute)           |

| 0x08        | Channel 1 vol                 | 1            | Description shown in subsequent section | 0x30 (0dB)            |

| 0x09        | Channel 2 vol                 | 1            | Description shown in subsequent section | 0x30 (0dB)            |

| 0x0A        | Fine master volume            | 1            | Description shown in subsequent section | 0x00 (0dB)            |

| 0x0B - 0X0D |                               |              | Reserved <sup>(1)</sup>                 |                       |

| 0x0E        | Volume configuration register | 1            | Description shown in subsequent section | 0x91                  |

| 0x0F        |                               | 1            | Reserved <sup>(1)</sup>                 |                       |

| 0x10        | Modulation limit register     | 1            | Description shown in subsequent section | 0x02                  |

| 0x15-0x19   |                               | 1            | Reserved <sup>(1)</sup>                 |                       |

| 0x1A        | Start/stop period register    | 1            | Description shown in subsequent section | 0x0A                  |

| 0x1B        |                               | 1            | Reserved <sup>(1)</sup>                 |                       |

| 0x1C        |                               | 1            | Reserved <sup>(1)</sup>                 |                       |

| 0x1D-0x1F   |                               | 1            | Reserved <sup>(1)</sup>                 |                       |

| 0x20        | Input MUX register            | 4            | Description shown in subsequent section | 0x 0089 777A          |

| 0x21-0x24   |                               | 4            | Reserved <sup>(1)</sup>                 |                       |

| 0x25        | PWM MUX register              | 4            | Description shown in subsequent section | 0x0102 1345           |

| 0x26-0x5F   |                               | 4            | Reserved <sup>(1)</sup>                 |                       |

#### Table 1. Serial Control Interface Register Summary

### Table 1. Serial Control Interface Register Summary (Cont.)

| Sub Address | Register Name         | No. of Bytes | Contents                                    | Initialization Values |

|-------------|-----------------------|--------------|---------------------------------------------|-----------------------|

| 0x46        | DRC Control           | 4            | Description shown in subsequent section     | 0x0000 0000           |

| 0x60        | DRC attack threshold  | 4            | u [31:24], attackTh [23:0]                  | 0x0003 2D64           |

| 0x61        | DRC release threshold | 4            | u [31:24], attackTh [23:0]                  | 0x0002 FFE4           |

| 0x62        | DRC Winldx            | 1            | Description shown in subsequent section     | 0x01                  |

| 0x63-0xF8   |                       |              | Reserved <sup>(2)</sup>                     |                       |

| 0xF9        | Update Device Address | 4            | u [31:8], New Dev Id[7:0] (New Dev Id=0x38) | 0x0000034             |

| 0xFA-0xFF   |                       |              | Reserved <sup>(2)</sup>                     |                       |

Note (1): Reserved register should not be accessed.

Note (2): Reserved register should not be accessed.

Note (3): "ae" stands for  $\alpha$  of energy filter, "aa" stands for  $\alpha$  of attack filter and "ad" stands for  $\alpha$  of decay filter and  $1 - \alpha = \omega$ .

#### Clock Control Register (0x00)

The clocks and data rates are automatically determined by the APA3163A. The clock control register contains the autodetected clock status. Bits D7-D5 reflect the sample rate. Bits D4-D2 reflect the MCLK frequency.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                              |

|----|----|----|----|----|----|----|----|-------------------------------------------------------|

| 0  | 0  | 0  | -  | -  | -  | -  | -  | f <sub>s</sub> =32kHz sample rate                     |

| 0  | 0  | 1  | -  | -  | -  | -  | -  | f <sub>s</sub> =88.2kHz/96kHz sample rate             |

| 0  | 1  | 0  | -  | -  | -  | -  | -  | f <sub>s</sub> =176.4kHz/192kHz sample rate           |

| 0  | 1  | 1  | -  | -  | -  | -  | -  | f <sub>s</sub> =44.1/48kHz sample rate <sup>(5)</sup> |

| -  | -  | -  | 0  | 0  | 0  | -  | -  | MCLK frequency=64xfs <sup>(6)</sup>                   |

| -  | -  | -  | 0  | 0  | 1  | -  | -  | MCLK frequency=128xfs <sup>(6)</sup>                  |

| -  | -  | -  | 0  | 1  | 0  | -  | -  | MCLK frequency=192xfs <sup>(7)</sup>                  |

| -  | -  | -  | 0  | 1  | 1  | -  | -  | MCLK frequency=256xfs <sup>(5) (8)</sup>              |

| -  | -  | -  | 1  | 0  | 0  | -  | -  | MCLK frequency=384xfs                                 |

| -  | -  | -  | 1  | 0  | 1  | -  | -  | MCLK frequency=512xfs                                 |

| -  | -  | -  | 1  | 1  | 0  | -  | -  | Reserved <sup>(4)</sup>                               |

| -  | -  | -  | 1  | 1  | 1  | -  | -  | Reserved <sup>(4)</sup>                               |

| -  | -  | -  | -  | -  | -  | 0  | -  | Reserved <sup>(4)</sup>                               |

| -  | -  | -  | -  | -  | -  | -  | 0  | Reserved <sup>(4)</sup>                               |

#### Table 2. Clock Control Register (0x00)

Note (4): Reserved registers should not be accessed.

Note (5): Italic is default.

Note (6): Only available for 44.1kHz and 48kHz rates.

Note (7): Rate only available for 32/44.1/48kHz sample rates.

Note (8): Not available at 8kHz.

#### Device Id Register (0x01)

The device ID register contains the ID code for the firmware revision.

### Table 3. General Status Register (0x01)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION            |

|----|----|----|----|----|----|----|----|---------------------|

| Х  | -  | -  | -  | -  | -  | -  | -  | Reserved            |

| -  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Identification code |

#### Error Status Register (0x02)

The error bits are sticky and are not cleared by the hardware. This means that the software must clear the register (write zeroes) and then read them to determine if they are persistent errors. Error Definitions:

MCLK Error : MCLK frequency is changing. The number of MCLKs per LRCLK is changing.

SCLK Error: The number of SCLKs per LRCLK is changing.

LRCLK Error: LRCLK frequency is changing.

#### Table 4. Error Status Register (0x02)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                                                                         |

|----|----|----|----|----|----|----|----|--------------------------------------------------------------------------------------------------|

| 1  | -  | -  | -  | -  | -  | -  | -  | MCLK error                                                                                       |

| -  | 1  | -  | -  | -  | -  | -  | -  | PLL auto clock error                                                                             |

| -  | -  | 1  | -  | -  | -  | -  | -  | SCLK error                                                                                       |

| -  | -  | -  | 1  | -  | -  | -  | -  | LRCLK error                                                                                      |

| -  | -  | -  | -  | 1  | -  | -  | -  | Reserved                                                                                         |

| -  | -  | -  | -  | -  | 1  | -  | -  | Reserved                                                                                         |

| -  | -  | -  | -  | -  | -  | 1  | -  | Over temperature warning (sets around 145 <sup>o</sup> C) POR error, OCP, thermal shutdown error |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | No errors                                                                                        |

Note: Italic is default.

#### System Control Register 1 (0x03)

The system control register 1 has several functions:

Bit D7: If 0, the dc-blocking filter for each channel is disabled. If 1, the dc-blocking filter (-3dB cutoff < 1Hz) for each channel is enabled (default).

Bit D5: If 0, use soft unmute on recovery from clock error. This is a slow recovery. Unmute takes same time as volume ramp defined in reg 0x0E. If 1, use hard unmute on recovery from clock error (default). This is a fast recovery, a single step volume ramp Bits D1-D0: Select de-emphasis.

| Table 5 | . System | Control | <b>Register 1</b> | (0x03) |

|---------|----------|---------|-------------------|--------|

|---------|----------|---------|-------------------|--------|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                |

|----|----|----|----|----|----|----|----|-----------------------------------------|

| 0  | -  | -  | -  | -  | -  | -  | -  | PWM high-pass (dc blocking) disenabled  |

| 1  | -  | -  | -  | -  | -  | -  | -  | PWM high-pass (dc blocking) enabled     |

| -  | 0  | -  | -  | -  | -  | -  | -  | Reserved                                |

| -  | -  | 0  | -  | -  | -  | -  | -  | Reserved                                |

| -  | -  | 0  | -  | -  | -  | -  | -  | Reserved                                |

| -  | -  | -  | 0  | -  | -  | -  | -  | Reserved                                |

| -  | -  | -  | -  | 0  | -  | -  | -  | Reserved                                |

| -  | -  | -  | -  | -  | 0  | -  | -  | Reserved                                |

| -  | -  | -  | -  | -  | -  | 0  | 0  | No de-emphasis                          |

| -  | -  | -  | -  | -  | -  | 0  | 1  | Reserved                                |

| -  | -  | -  | -  | -  | -  | 1  | 0  | De-emphasis for f <sub>s</sub> =44.1kHz |

| -  | -  | -  | -  | -  | -  | 1  | 1  | De-emphasis for f <sub>s</sub> =48kHz   |

### Serial Data Interface Register (0x04)

As shown in Table 6, the APA3163A supports 9 serial data modes. The default is 24bit, I<sup>2</sup>S mode.

#### Table 6. Serial Data Interface Control Register (0x04) Format

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Word Length | Receive Serial Data Interface Format |

|----|----|----|----|----|----|----|----|-------------|--------------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 16          | Right-justified                      |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 20          | Right-justified                      |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 24          | Right-justified                      |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 16          | I <sup>2</sup> S                     |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 20          | I <sup>2</sup> S                     |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 24          | I <sup>2</sup> S                     |

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 16          | Left-justified                       |

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 20          | Left-justified                       |

| 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 24          | Left-justified                       |

| 0  | 0  | 0  | 0  | 1  | -  | 1  | 0  | -           | Reserved                             |

| 0  | 0  | 0  | 0  | 1  | -  | -  | 1  | -           | Reserved                             |

| 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | -           | Reserved                             |

Note: Italic is default.

#### System Control Register 2 (0x05)

When bit D6 is set low, the system exits all channel shutdown and starts playing audio; otherwise, the outputs are shut down (hard mute).

#### Table 7. System Control Register 2 (0x05)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                      |

|----|----|----|----|----|----|----|----|-----------------------------------------------|

| 0  | -  | -  | -  | -  | -  | -  | -  | Reserved                                      |

| -  | 1  | -  | -  | -  | -  | -  | -  | Enter all channel shut down (hard mute)       |

| -  | 0  | -  | -  | -  | -  | -  | -  | Exit all channel shut down (Normal operation) |

| -  | -  | 0  | 0  | 0  | 0  | 0  | 0  | Reserved                                      |

Note: Italic is default.

#### Soft Mute Register (0x06)

Writing a 1 to any of the following bits sets the output of the respective channel to 50% duty cycle (soft mute).

#### Table 8. Soft Mute Register (0x06)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION               |

|----|----|----|----|----|----|----|----|------------------------|

| -  | -  | -  | -  | -  | -  | -  | 1  | Soft mute channel 1    |

| -  | -  | -  | -  | -  | -  | -  | 0  | Soft un-mute channel 1 |

| -  | -  | -  | -  | -  | -  | 1  | -  | Soft mute channel 2    |

| -  | -  | -  | -  | -  | -  | 0  | -  | Soft un-mute channel 2 |

| 0  | 0  | 0  | 0  | 0  | 0  | -  | -  | Reserved               |

#### Volume Registers (0x07, 0x08, 0x09)

Step size is 0.5 dB.

| Master volume    | - 0x07 (default is mute) |

|------------------|--------------------------|

| Channel-1 volume | - 0x08 (default is 0 dB) |

| Channel-2 volume | - 0x09 (default is 0 dB) |

#### Table 9. Volume Registers (0x07, 0x08, 0x09)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                  |

|----|----|----|----|----|----|----|----|-------------------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 24dB                                      |

| 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0dB                                       |

|    | -  |    |    |    |    |    |    |                                           |

| 1  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | -78.5dB                                   |

| 1  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | -79.0dB                                   |

| 1  | 1  | 0  | 0  | 1  | 1  | 1  | 1  | Values between 0xCF and 0xFE are Reserved |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | MUTE (default for master volume)          |

Note: Italic is default.

#### Master Fine Volume Register (0x0A)

This register can be used to provide precision tuning of master volume.

#### Table 10. Master Fine Volume Register (0x0A)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                      |

|----|----|----|----|----|----|----|----|-------------------------------|

| -  | -  | -  | -  | -  | -  | 0  | 0  | 0dB                           |

| -  | -  | -  | -  | -  | -  | 0  | 1  | 0.125dB                       |

| -  | -  | -  | -  | -  | -  | 1  | 0  | 0.25dB                        |

| -  | -  | -  | -  | -  | -  | 1  | 1  | 0.345dB                       |

| 1  | -  | -  | -  | -  | -  | -  | -  | Write enable bit              |

| -  | -  | -  | -  | -  | -  | -  | -  | Ignore write to register 0x0A |

Note: Italic is default.

#### Volume Configuration Register (0x0E)

Bits Volume slew rate (Used to control volume change and MUTE ramp rates). These bits control the D2-D0: number of steps in a volume ramp. Volume steps occur at a rate that depends on the sample rate of the I<sup>2</sup>S data as follows.

| Sample Rate (kHz) | Approximate Ramp Rate |

|-------------------|-----------------------|

| 8/16/32           | 125µs/step            |

| 11.025/22.05/44.1 | 90.7µs/step           |

| 12/24/48          | 83.3μs/step           |

#### Table 11. Volume Control Register (0x0E)

| l | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                               |

|---|----|----|----|----|----|----|----|----|--------------------------------------------------------|

|   | 1  | 0  | 0  | 1  | 0  | -  | -  | -  | Reserved                                               |

|   | -  | -  | -  | -  | -  | 0  | 0  | 0  | Volume slew 512 steps (43ms volume ramp time at 48kHz) |

### Volume Configuration Register (0x0E) (Cont.)

#### Table 11. Volume Control Register (0x0E)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                                 |

|----|----|----|----|----|----|----|----|----------------------------------------------------------|

| -  | -  | -  | -  | -  | 0  | 0  | 1  | Volume slew 1024 steps (85ms volume ramp time at 48kHz)  |

| -  | -  | -  | -  | -  | 0  | 1  | 0  | Volume slew 2048 steps (171ms volume ramp time at 48kHz) |

| -  | -  | -  | -  | -  | 0  | 1  | 1  | Volume slew 256 steps (21ms volume ramp time at 48kHz)   |

| -  | -  | -  | -  | -  | 1  | х  | х  | Reserved                                                 |

Note: Italic is default.

#### Modulation Limit Register (0x10)

#### Table 12. Modulation Limit Register (0x10)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | MODULATION LIMIT |

|----|----|----|----|----|----|----|----|------------------|

| -  | -  | -  | -  | -  | 0  | 0  | 0  | Reserved         |

| -  | -  | -  | -  | -  | 0  | 0  | 1  | 98.4%            |

| -  | -  | -  | -  | -  | 0  | 1  | 0  | 97.7%            |

| -  | -  | -  | -  | -  | 0  | 1  | 1  | 96.9%            |

| -  | -  | -  | -  | -  | 1  | 0  | 0  | 96.1%            |

| -  | -  | -  | -  | -  | 1  | 0  | 1  | 95.3%            |

| -  | -  | -  | -  | -  | 1  | 1  | 0  | 94.5%            |

| -  | -  | -  | -  | -  | 1  | 1  | 1  | 93.8%            |

| 0  | 0  | 0  | 0  | 0  | -  | -  | -  | Reserved         |

Note: Italic is default.

#### Start/Stop Period Register (0x1A)

This register is used to control the soft-start and soft-stop period following an enter/exit all channel shut down command or change in the  $\overline{SD}$  state. This helps reduce pops and clicks at start-up and shutdown. The times are only approximate and vary depending on device activity level and I<sup>2</sup>S clock stability.

Table 13. Start/Stop Period Register (0x1A)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                 |

|----|----|----|----|----|----|----|----|------------------------------------------|

| 0  | 0  | 0  | -  | -  | -  | -  | -  | Reserved                                 |

| -  | -  | -  | 0  | 0  | -  | -  | -  | No 50% duty cycle start/stop period      |

| -  | -  | -  | 0  | 1  | 0  | 0  | 0  | 16.5ms 50% duty cycle start/stop period  |

| -  | -  | -  | 0  | 1  | 0  | 0  | 1  | 23.9ms 50% duty cycle start/stop period  |

| -  | -  | -  | 0  | 1  | 0  | 1  | 0  | 31.4ms 50% duty cycle start/stop period  |

| -  | -  | -  | 0  | 1  | 0  | 1  | 1  | 40.4ms 50% duty cycle start/stop period  |

| -  | -  | -  | 0  | 1  | 1  | 0  | 0  | 53.9ms 50% duty cycle start/stop period  |

| -  | -  | -  | 0  | 1  | 1  | 0  | 1  | 70.3ms 50% duty cycle start/stop period  |

| -  | -  | -  | 0  | 1  | 1  | 1  | 0  | 94.2ms 50% duty cycle start/stop period  |

| -  | -  | -  | 0  | 1  | 1  | 1  | 1  | 125.7ms 50% duty cycle start/stop period |

### Start/Stop Period Register (0x1A) (Cont.)

### Table 13. Start/Stop Period Register (0x1A)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                   |

|----|----|----|----|----|----|----|----|--------------------------------------------|

| -  | -  | -  | 1  | 0  | 0  | 0  | 0  | 164.6ms 50% duty cycle start/stop period   |

| -  | -  | -  | 1  | 0  | 0  | 0  | 1  | 239.4ms 50% duty cycle start/stop period   |

| -  | -  | -  | 1  | 0  | 0  | 1  | 0  | 314.2ms 50% duty cycle start/stop period   |

| -  | -  | -  | 1  | 0  | 0  | 1  | 1  | 403.9ms 50% duty cycle start/stop period   |

| -  | -  | -  | 1  | 0  | 1  | 0  | 0  | 538.6ms 50% duty cycle start/stop period   |

| -  | -  | -  | 1  | 0  | 1  | 0  | 1  | 703.4ms 50% duty cycle start/stop period   |

| -  | -  | -  | 1  | 0  | 1  | 1  | 0  | 942.5ms 50% duty cycle start/stop period   |

| -  | -  | -  | 1  | 0  | 1  | 1  | 1  | 1256.6ms 50% duty cycle start/stop period  |

| -  | -  | -  | 1  | 1  | 0  | 0  | 0  | 1728.1ms 50% duty cycle start/stop period  |

| -  | -  | -  | 1  | 1  | 0  | 0  | 1  | 2513.6ms 50% duty cycle start/stop period  |

| -  | -  | -  | 1  | 1  | 0  | 1  | 0  | 3299.1ms 50% duty cycle start/stop period  |

| -  | -  | -  | 1  | 1  | 0  | 1  | 1  | 4241.7ms 50% duty cycle start/stop period  |

| -  | -  | -  | 1  | 1  | 1  | 0  | 0  | 5655.6ms 50% duty cycle start/stop period  |

| -  | -  | -  | 1  | 1  | 1  | 0  | 1  | 7383.7ms 50% duty cycle start/stop period  |

| -  | -  | -  | 1  | 1  | 1  | 1  | 0  | 9897.3ms 50% duty cycle start/stop period  |

| -  | -  | -  | 1  | 1  | 1  | 1  | 0  | 13196.4ms 50% duty cycle start/stop period |

Note: Italic is default.

#### Input Multiplexer Register (0x20)

This register controls the modulation scheme (BD mode) as well as the routing of I<sup>2</sup>S audio to the internal channels.

| D31 | D30 | D29 | D28 | D27 | D26 | D25 | D24 | FUNCTION                |

|-----|-----|-----|-----|-----|-----|-----|-----|-------------------------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Reserved                |

|     |     |     |     |     |     |     |     |                         |

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | FUNCTION                |

| 0   | -   | -   | -   | -   | -   | -   | -   | Reserved                |

| 1   | -   | -   | -   | -   | -   | -   | -   | Channel 1 BD mode       |

| -   | 0   | 0   | 0   | -   | -   | -   | -   | SDIN-L to Channel 1     |

| -   | 0   | 0   | 1   | -   | -   | -   | -   | SDIN-R to Channel 1     |

| -   | 0   | 1   | 0   | -   | -   | -   | -   | Reserved                |

| -   | 0   | 1   | 1   | -   | -   | -   | -   | Reserved                |

| -   | 1   | 0   | 0   | -   | -   | -   | -   | Reserved                |

| -   | 1   | 0   | 1   | -   | -   | -   | -   | Reserved                |

| -   | 1   | 1   | 0   | -   | -   | -   | -   | Ground (0) to channel 1 |

| -   | 1   | 1   | 1   | -   | -   | -   | -   | Reserved                |

| -   | -   | -   | -   | 0   | -   | -   | -   | Reserved                |

| -   | -   | -   | -   | 1   | -   | -   | -   | Channel-2 BD mode       |

### Table 14. Input Multiplexer Register (0x20)

### Input Multiplexer Register (0x20) (Cont.)

#### Table 14. Input Multiplexer Register (0x20)

| D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | FUNCTION                |

|-----|-----|-----|-----|-----|-----|-----|-----|-------------------------|

| -   | -   | -   | -   | -   | 0   | 0   | 0   | SDIN-L to Channel 2     |

| -   | -   | -   | -   | -   | 0   | 0   | 1   | SDIN-R to Channel 2     |

| -   | -   | -   | -   | -   | 0   | 1   | 0   | Reserved                |

| -   | -   | -   | -   | -   | 0   | 1   | 1   | Reserved                |

| -   | -   | -   | -   | -   | 1   | 0   | 0   | Reserved                |

| -   | -   | -   | -   | -   | 1   | 0   | 1   | Reserved                |

| -   | -   | -   | -   | -   | 1   | 1   | 0   | Ground (0) to channel 2 |

| -   | -   | -   | -   | -   | 1   | 1   | 1   | Reserved                |