PMIC for LED BL + LCD Bias Power

### Features

- · 2.9V to 5.5V Input Supply Range

- Current Mode Step-up Regulator (LCD bias)

- 1MHz Fixed Operating Frequency

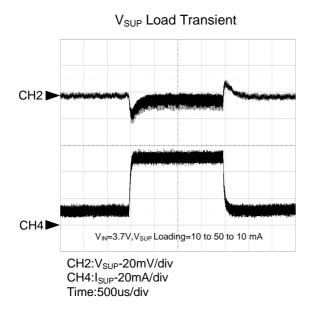

- Fast Transient Response

- 18V/700mA ,1.5W Internal N-MOS

- Positive & Negative Charge Pump Driver for V<sub>GH</sub>,

V<sub>GL</sub>

- Current Mode Step-up Regulator (LED BL)

- 1MHz Fixed Operating Frequency

- 0.2V Feedback Voltage

- 18V/2A, 0.3W internal N-MOS

- · Control Output for External P-MOS to Support

- Completely Disconnecting the Battery

- Adjustable Power Sequencing by External Capacitor

- · Internal Soft-Start

- Multiple Overload Protection

- · Thermal Shutdown

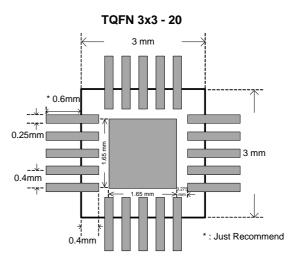

- Available in Small Package:TQFN3x3-20

## **General Description**

The APW7279 integrates with two high-performance stepup converter and two charge pump controllers for TFT-LCD and Backlight applications. Both the two step-up regulators are a current-mode, fixed-frequency PWM switching regulator. The 1.0MHz switching frequency allows the usage of low-profile inductors and ceramic capacitors to minimize the thickness of LCD panel designs. The charge pump controllers provide regulated the gatedriver of TFT-LCD V<sub>GH</sub> and V<sub>GL</sub> supplies. The APW7279 is available in a tiny 3mm x 3mm 20-pin TQFN package (TQFN3x3-20).

### Applications

· Tablet PC

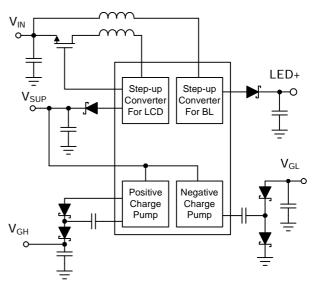

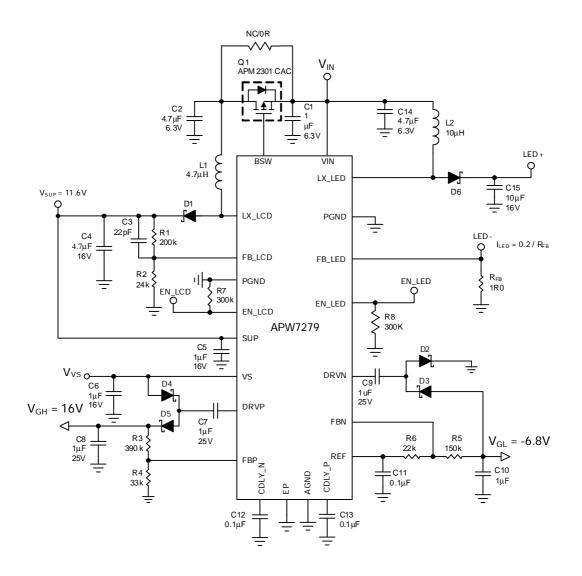

### **Simplified Application Circuit**

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

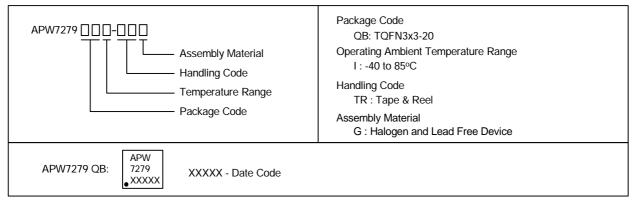

## Ordering and Marking Information

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or CI does not exceed 900ppm by weight in homogeneous material and total of Br and CI does not exceed 1500ppm by weight).

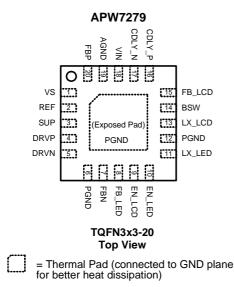

## **Pin Configuration**

### Absolute Maximum Ratings (Note 1)

| Symbol | Parameter                                                                         | Rating           | Unit |

|--------|-----------------------------------------------------------------------------------|------------------|------|

| VIN    | Input Bias Supply Voltage (VIN to GND)                                            | -0.3 ~ 6         | V    |

|        | LX_LCD, DRVN, DRVP, SUP, VS to GND Voltage                                        | -0.3 ~ 20        | V    |

|        | LX_LED                                                                            | -0.3 ~ 20        | V    |

|        | EN_LCD, EN_LED, FB_LCD, FB_LED, FBP, FBN, BSW, CDLY_N, VDLY_P, REF to GND Voltage | -0.3 ~ VIN       | V    |

| PD     | Power Dissipation                                                                 | Internally Limit | W    |

| ТJ     | Maximum Junction Temperature                                                      | 150              | °C   |

| TSTG   | Storage Temperature                                                               | -65 ~ 150        | °C   |

| TSDR   | Maximum Lead Soldering Temperature (10 Seconds)                                   | 260              | °C   |

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

### Thermal Characteristics (Note 2, 3)

| Symbol        | Parameter                                           | Typical Value | Unit |      |

|---------------|-----------------------------------------------------|---------------|------|------|

| $\theta_{JA}$ | Junction-to-Ambient Resistance in free air (Note 2) | TQFN3x3-20    | 50   | °C/W |

| θյς           | Case-to-Ambient Resistance in free air (Note 2)     | TQFN3x3-20    | 12   | °C/W |

Note 2:  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air.

### Recommended Operating Conditions (Note 3)

| Symbol           | Parameter                                           | Range                          | Unit |

|------------------|-----------------------------------------------------|--------------------------------|------|

| V <sub>IN</sub>  | Input Bias Supply Voltage (VIN to GND)              | 2.9 ~ 5.5                      | V    |

| V <sub>SUP</sub> | LCD Driver Step-up Converter Output Voltage         | V <sub>N</sub> ~ 15            | V    |

| $V_{GH}$         | Positive Charge Pump Output Voltage                 | 0 ~ (2 x V <sub>SUP</sub> ) -2 | V    |

| $V_{GL}$         | Negative Charge Pump Output Voltage                 | $-V_{SUP}$ +2 ~ $V_{REF}$      | V    |

| C <sub>IN</sub>  | Input Power Capacitor                               | 4.7 ~ 10                       | μF   |

| L1               | Inductor Range                                      | 1 ~ 10                         | μH   |

| $C_{GH}$         | VGH Capacitor                                       | 0.22 ~ 2.2                     | μF   |

| $C_{GL}$         | VGLCapacitor                                        | 0.22 ~ 2.2                     | μF   |

| $C_{REF}$        | VREF Capacitor                                      | 0.1 ~ 0.47                     | μF   |

| R1               | Feedback Resistance of $V_{\mbox{\scriptsize SUP}}$ | 0.1 ~ 1                        | MΩ   |

| R3               | Feedback Resistance of V <sub>GH</sub>              | 0.1 ~ 1                        | MΩ   |

| R5               | Feedback Resistance of V <sub>GL</sub>              | 0.1 ~ 0.54                     | MΩ   |

| T <sub>A</sub>   | Ambient Temperature                                 | -40 ~ 85                       | °C   |

| TJ               | Junction Temperature                                | -40 ~ 125                      | °C   |

Note 3: Refer to the typical application circuit.

### **Electrical Characteristics**

Unless otherwise specified, these specifications apply over V\_{IN}=3.6V and T\_{A}=25^{\circ}C.

| 0                           | De se se sta s                           | Test Osuditions                                                                            |      | APW7279 | )    | Unit |

|-----------------------------|------------------------------------------|--------------------------------------------------------------------------------------------|------|---------|------|------|

| Symbol                      | Parameter                                | Test Conditions                                                                            | Min  | Тур     | Мах  | Unit |

| SUPPLY                      | CURRENT                                  |                                                                                            |      | r.      |      |      |

| VIN                         | Input Voltage Range                      |                                                                                            | 2.9  | -       | 5.5  | V    |

| loc                         | VIN Operating Current                    | $V_{FB\_LCD} = 1.1V$ , switching<br>$V_{FB\_LED} = 0.2V$ , switching                       | -    | 3       | 7    | mA   |

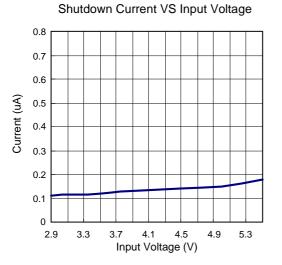

| I <sub>SD</sub>             | VIN Shutdown Current                     | $V_{EN_{LCD}} = V_{EN_{LED}} = GND$                                                        | -    | 0.1     | 1    | uA   |

| UNDER V                     | OLTAGE LOCKOUT (UVLO)                    |                                                                                            |      |         |      |      |

| VIN                         | UVLO Threshold Voltage                   | V <sub>IN</sub> Rising                                                                     | 2.4  | 2.6     | 2.8  | V    |

|                             | UVLO Hysteresis Voltage                  |                                                                                            | 200  | 250     | 300  | mV   |

| STET-UP                     | REGULATOR FOR LCD POWER                  | 2                                                                                          |      |         |      |      |

| $V_{REF}$                   | Referenœ Voltage                         | $V_{IN} = 2.9V \sim 5.5V, T_A = -40 \sim 85^{\circ}C$<br>$I_{REF} = 0 \sim 2mA$            | 1.22 | 1.25    | 1.28 | V    |

| I <sub>REF</sub>            | Referenœ Voltage Output<br>Current       |                                                                                            | 2    | -       | -    | mA   |

| $V_{\text{FB}\_\text{LCD}}$ | FB_LCD Regulation Voltage                | $V_{IN} = 2.9V \sim 5.5V, T_A = -40 \sim 85^{\circ}C$                                      | 1.22 | 1.25    | 1.28 | V    |

| I <sub>FB_LCD</sub>         | FB_LCD Input Current                     |                                                                                            | -50  | -       | 50   | nA   |

| F <sub>SW_LCD</sub>         | Switching Frequency                      | V <sub>FB_LCD</sub> = 1.1V                                                                 | 0.85 | 1.0     | 1.15 | MHz  |

| R <sub>on_lcd</sub>         | Power Switch On Resistance               | V <sub>IN</sub> = 3.6V                                                                     | -    | 1.1     | -    | Ω    |

|                             | Power Switch Current Limit               |                                                                                            | 1    | -       | -    | А    |

|                             | LX_LCD Leakage Current                   | $V_{IN} = 5V, V_{EN\_LCD} = GND, V_{LX\_LCD} = 16V$                                        | -1   | -       | 1    | uA   |

| D <sub>MAX_LCD</sub>        | LX_LCD Maximum Duty Cycle                |                                                                                            | 92   | 95      | 98   | %    |

| T <sub>SS_LCD</sub>         | Step-up Regulator Soft-start<br>Duration | (Note 4)                                                                                   | -    | 2       | -    | ms   |

| $V_{FB\_UVP}$               | FB_LCD Under Voltage<br>Protection (UVP) |                                                                                            | -    | 1       | -    | V    |

|                             | UVP Debounce time                        |                                                                                            | -    | 250     | -    | us   |

| STET-UP                     | REGULATOR FOR LED BACKL                  | IGHT                                                                                       |      |         |      |      |

| $V_{FB\_LED}$               | FB_LED Regulation Voltage                | $V_{IN} = 2.9V \sim 5.5V, T_A = -40 \sim 85^{\circ}C$<br>( $T_J = -40 \sim 125^{\circ}C$ ) | 190  | 200     | 210  | mV   |

| I <sub>FB_LED</sub>         | FB_LED Input Current                     |                                                                                            | -50  | -       | 50   | nA   |

| $F_{\text{SW}\_\text{LED}}$ | Switching Frequency                      | V <sub>FB_LED</sub> = GND                                                                  | 0.85 | 1.0     | 1.15 | MHz  |

| $R_{ON\_LED}$               | Power Switch On Resistance               | V <sub>IN</sub> = 3.6V                                                                     | -    | 0.3     | -    | Ω    |

| I <sub>LIM_LED</sub>        | Power Switch Current-Limit               |                                                                                            | 2    | -       | -    | Α    |

|                             | LX_LED Leakage Current                   | $V_{IN} = 5V, V_{EN\_LED} = GND, V_{LX\_LED} = 16V$                                        | -1   |         | 1    | uA   |

| D <sub>MAX_LED</sub>        | LX_LED Maximum Duty Cycle                |                                                                                            | 92   | 95      | 98   | %    |

| V <sub>LX_OVP</sub>         | LX_LED Over Voltage<br>Threshold         | VLX_LED Rising                                                                             | 16.5 | 18      | 19.9 | V    |

| T <sub>SS_LED</sub>         | Step-up Regulator Soft-start<br>Duration | (Note 4)                                                                                   | -    | 2       | -    | ms   |

### **Electrical Characteristics**

Unless otherwise specified, these specifications apply over V  $_{\rm IN}{=}3.6V$  and T  $_{\rm A}{=}$  25°C.

| Symbol                                                              | Parameter                                                                           | ameter Test Conditions                                          | APW7279 |      |      | l l m i é |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------|------|------|-----------|

| Symbol                                                              |                                                                                     |                                                                 | Min     | Тур  | Мах  | Unit      |

| SHUTDO                                                              | WN                                                                                  |                                                                 |         |      |      |           |

| V <sub>enh_lcd</sub>                                                | EN_LCD High Threshold                                                               | V <sub>EN_LCD</sub> Rising                                      | 1.4     | -    | -    | V         |

| V <sub>enl_lcd</sub>                                                | EN_LCD Low Threshold                                                                | V <sub>EN_LCD</sub> Falling                                     | -       | -    | 0.4  | V         |

|                                                                     | EN_LCD Leakage Current                                                              | $V_{IN} = 5V, V_{EN\_LCD} = 5V$                                 | -1      | -    | 5    | uA        |

| Venh_led                                                            | EN_LED High Threshold                                                               | V <sub>EN_LED</sub> Rising                                      | 1       | -    | -    | V         |

| V <sub>enl_lcd</sub>                                                | EN_LED Low Threshold                                                                | V <sub>EN_LED</sub> Falling                                     | -       | -    | 0.4  | V         |

|                                                                     | EN_LED Leakage Current                                                              | $V_{IN} = 5V, V_{EN\_LED} = 5V$                                 | -1      | -    | 1    | uA        |

| CHARGE                                                              | CURRENT AND INTERNAL SW                                                             | псн                                                             |         |      |      |           |

| I <sub>CDLY_N</sub>                                                 | CDLY_N Charge Current                                                               |                                                                 | -       | 10   | -    | uA        |

| CDLY_N High Threshold V <sub>GL</sub> Soft-start without Delay from |                                                                                     | V <sub>GL</sub> Soft-start without Delay from V <sub>AVDD</sub> | -       | 1    | -    | V         |

| I <sub>C DLY_P</sub>                                                |                                                                                     |                                                                 | -       | 10   | -    | uA        |

|                                                                     | CDLY_P High Threshold V <sub>GH</sub> Soft-start without Delay from V <sub>GL</sub> |                                                                 | -       | 1    | -    | V         |

| I <sub>BSW</sub>                                                    | BSW Pull-down Current                                                               |                                                                 | 3       | 5    | 10   | uA        |

|                                                                     | BSW to VIN Ron                                                                      |                                                                 | -       | 200  | -    | Ω         |

| $R_{VS}$                                                            | SUP to VS On Resistance                                                             |                                                                 | -       | 300  | -    | Ω         |

|                                                                     | SUP to VS Leakage Current                                                           |                                                                 | -       | -    | 100  | nA        |

|                                                                     | VS Soft-start Duration                                                              | (Note 4)                                                        | -       | 2    | -    | ms        |

| POSITIVE                                                            | REGULATED CHARGE PUMP                                                               |                                                                 |         |      |      |           |

| V FBP                                                               | FBP Regulation Voltage                                                              | $V_{IN} = 2.9V \sim 5.5V, T_A = -40 \sim 85^{\circ}C$           | 1.22    | 1.25 | 1.28 | V         |

| I <sub>FBP</sub>                                                    | FBP Input Current                                                                   |                                                                 | -50     | -    | 50   | nA        |

| I <sub>DRVP</sub>                                                   | RMS DRVP Output Current                                                             | V <sub>SUP</sub> = 12V                                          | 5       | -    | -    | mA        |

|                                                                     | Positive Charge Pump<br>Frequency                                                   |                                                                 | 400     | 500  | 600  | kHz       |

| T <sub>SSP</sub>                                                    | Positive Charge Pump<br>Soft-start Duration                                         | (Note 4)                                                        | -       | 2    | -    | ms        |

| NEGATIV                                                             | E REGULATED CHARGE PUMP                                                             | <b>)</b>                                                        |         |      |      |           |

| $V_{\text{FBN}}$                                                    | FBN Regulation Voltage                                                              | $V_{IN}=2.9V \sim 5.5V, T_A = -40 \sim 85^{\circ}C$             | -25     | 0    | 25   | mV        |

| $I_{FBN}$                                                           | FBN Input Current                                                                   |                                                                 | -50     | -    | 50   | nA        |

| I <sub>D RVN</sub>                                                  | RMS DRVN Output Current                                                             | V <sub>SUP</sub> = 12V                                          | 5       | -    | -    | mA        |

|                                                                     | Negative Charge Pump<br>Frequency                                                   |                                                                 | 400     | 500  | 600  | kHz       |

| $T_{SSN}$                                                           | Negative Charge Pump<br>Soft-start Duration                                         | (Note 4)                                                        | -       | 2    | -    | ms        |

| OVER-TE                                                             | MPERATURE PROTECTION                                                                |                                                                 |         |      |      |           |

| Top                                                                 | Over-Temperature Protection (note 4)                                                | T <sub>J</sub> Rising                                           | -       | 160  | -    | °C        |

|                                                                     | Over-Temperature Protection<br>Hysteresis (note4)                                   |                                                                 | -       | 40   | -    | °C        |

Note 4: Guarantee by design, not production test.

## **Pin Description**

| Pin         |        | Function                                                                                                                                                                                                           |

|-------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN3x3-20  | NAME   | Function                                                                                                                                                                                                           |

| 1           | VS     | The supply voltage of positive charge pump regulator.                                                                                                                                                              |

| 2           | REF    | Internal 1.25V reference voltage output. Connect 1µF capacitor to this pin.                                                                                                                                        |

| 3           | SUP    | This is the supply pin of the positive and negative charge pump driver. Connected this pin to the output of the LCD Driver step-up converter $V_{SUP}$ .                                                           |

| 4           | DRVP   | Regulated charge pump driver for $V_{\mbox{\scriptsize GH}}.$ Connect to flying capacitor.                                                                                                                         |

| 5           | DRVN   | Regulated charge pump driver for $V_{\text{GL}}.$ Connect to flying capacitor.                                                                                                                                     |

| 6           | PGND   | Power Ground.                                                                                                                                                                                                      |

| 7           | FBN    | Negative charge pump feedback input.                                                                                                                                                                               |

| 8           | FB_LED | Step-up converter feedback input of LED driver.                                                                                                                                                                    |

| 9           | EN_LCD | Enable pin of LCD driver. Logic high initiates power-up sequencing. Logic low disable the LCD Driver.                                                                                                              |

| 10          | EN_LED | Enable pin of LED driver. Logic high initiates power-up sequencing. Logic low disable the LED Driver.                                                                                                              |

| 11          | LX_LED | Step-up converter inductor/diode connection.                                                                                                                                                                       |

| 12          | PGND   | Power Ground.                                                                                                                                                                                                      |

| 13          | LX_LCD | Step-up converter inductor/diode connection.                                                                                                                                                                       |

| 14          | BSW    | Bi-direction switch control pin. This switch disconnects VOUT from VIN during shutdown and any fault evens.                                                                                                        |

| 15          | FB_LCD | Step-up converter feedback input of LCD driver.                                                                                                                                                                    |

| 16          | CDLY_P | Delay Setting Capacitor Connection Pin. Connecting a capacitor from this pin to GND allows the setting of delay time between $V_{SUP}$ to $V_{GL}$ during start-up. Pull this pin exceed 1V ignore the delay time. |

| 17          | CDLY_N | Delay Setting Capacitor Connection Pin. Connecting a capacitor from this pin to GND allows the setting of delay time between $V_{GL}$ to $V_{GH}$ during start-up. Pull this pin exceed 1V ignore the delay time.  |

| 18          | VIN    | IC power input.                                                                                                                                                                                                    |

| 19          | AGND   | Analog Ground.                                                                                                                                                                                                     |

| 20          | FBP    | Positive charge pump feedback input.                                                                                                                                                                               |

| Exposed Pad | PGND   | Power Ground.                                                                                                                                                                                                      |

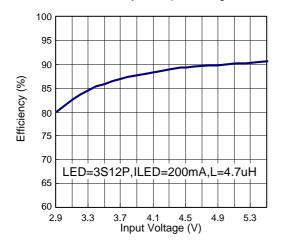

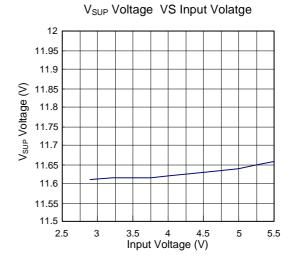

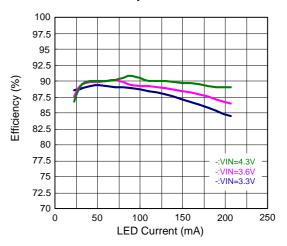

## **Typical Operating Characteristics**

Efficiency VS Input Voltage

Efficiency VS LED current

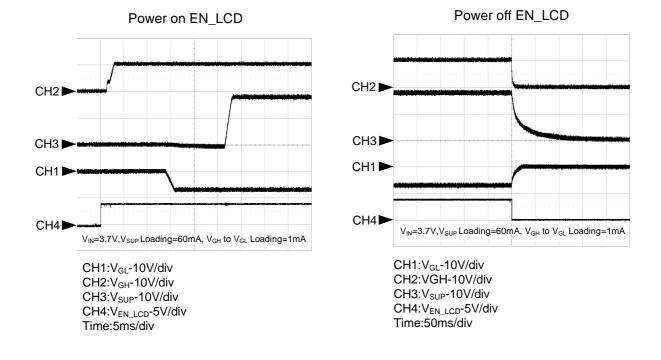

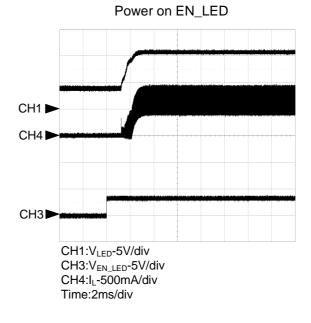

### **Operating Waveforms**

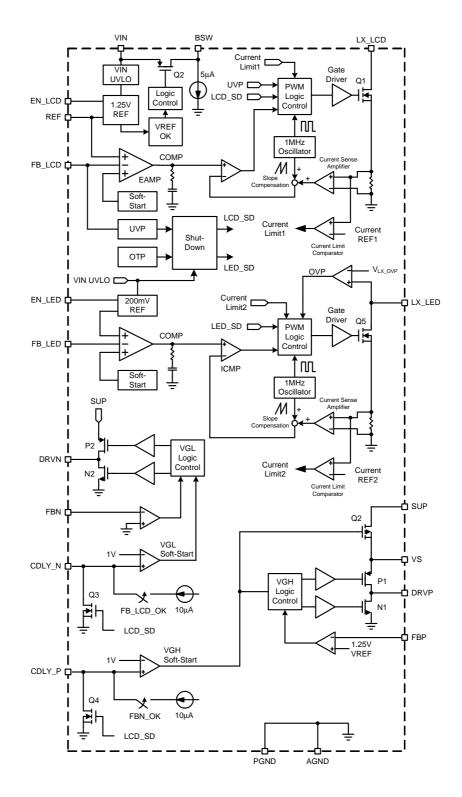

### **Block Diagram**

## **Typical Application Circuit**

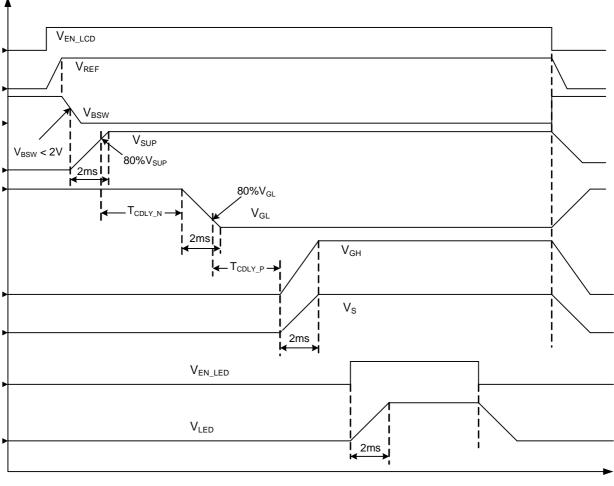

### **Power On Sequence**

Time

The output voltage falling slew rate after shutdown depend on external resistance.

### **Function Description**

#### VIN Under-Voltage Lockout (UVLO)

The Under-voltage lockout (UVLO) circuit compares the input voltage at VIN with the UVLO threshold to ensure the input voltage is high enough for reliable operation. The 100mV (typ) hysteresis prevents supply transients from causing a restart. Once the input voltage exceeds the UVLO rising threshold, startup begins. When the input voltage falls below the UVLO falling threshold, the controller turns off the device.

#### LCD Driver Step-up Converter Control Loop

The APW7279 includes a constant frequency, synchronous rectifier and current-mode switching regulator. In normal operation, the internal main switch (Q1) is turned on each cycle. The peak inductor current at which EAMP turn off the Q1 is controlled by the voltage on the COMP node which is the output of the error amplifier (EAMP). An external resistive divider connected between VSUP and ground allows the EAMP to receive an output feedback voltage VFB at FB pin. When the load current increases, it causes a slightly decrease in VFB relative to the reference voltage, which in turn causes the COMP voltage to increase until the average inductor current matches the new load current. At light load current, the COMP voltage is lower. The APW7279 auto skips pulse.

#### **Pulse Skip Modulation**

APW7279 auto skip pulse at light load.

#### LCD Driver Step-up Converter Current Limit

The APW7279 integrated a current-limit-comparator in main step-up converter. It monitors the inductor current, flows through the N-channel MOSFET(Q1), and limits the current peak at current-limit level to prevent loads and the APW7279 from damaging during overload or short-circuit conditions.

#### VREF

The VREF initiates soft-start process after POR and EN\_LCD goes high. Shutdown if POR and EN\_LCD goes low.

#### CDLY\_N

Connecting a capacitor from this pin to GND allows the setting of delay time between V<sub>GL</sub> and V<sub>SUP</sub>. Once V<sub>SUP</sub> reaches 80% of its normal regulated output voltage, an internal 10uA current source starts to charge C<sub>CDLY\_N</sub>, the V<sub>GL</sub> channel initiates soft-start process once V<sub>CDLY\_N</sub> exceed 1V. If the V<sub>CDLY\_N</sub> exceeds 1V before V<sub>SUP</sub> start up, the V<sub>SUP</sub> and V<sub>GL</sub> start up simultaneously.

#### CDLY\_P

Connecting a capacitor from this pin to GND allows the setting of delay time between V<sub>GH</sub> and V<sub>GL</sub>. Once V<sub>GL</sub> reaches 80% of its normal regulated output voltage, an internal 10uA current source starts to charge C<sub>CDLY\_P</sub>, the V<sub>GH</sub> channel initiates soft-start process once V<sub>CDLY\_P</sub> exceed 1V. If the V<sub>CDLY\_P</sub> exceeds 1V before V<sub>GL</sub> start up, the V<sub>GL</sub> and V<sub>GH</sub> start up simultaneously.

#### BSW

Once  $V_{REF}$  is within 8% of its normal regulated output voltage, an internal current source from the BSW to GND to pull BSW low. Once the VBSW below 2V, the LCD driver step-up converter initiates soft-start process. The  $V_{BSW}$  pull to VIN if main step-up current limit detected without delay, EN\_LCD pull low or VIN below POR.

#### An Isolation Switch from VSUP to VS (Q2)

The VS is the voltage source of positive charge pump (V<sub>GH</sub>). Once V<sub>GL</sub> reaches 80% of its normal regulated output voltage, the timer will start counting T<sub>CDLY\_P</sub>. The P-FET(Q2) starts switching soft on after T<sub>CDLY\_P</sub> and the Q2 fully turns on after 2ms. The Q2 turns off at Q1 current limit detected and EN\_LCD goes low.

### **Function Description**

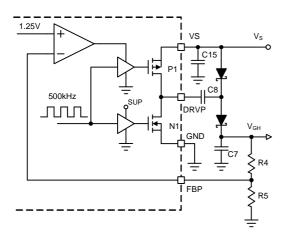

#### **Positive Charge Pump**

The positive charge-pump regulator is typically used to generate the positive supply rail for the TFT LCD gate driver ICs. The output voltage is set with an external resistive voltage-divider from its output to GND with the midpoint connected to FBP. The charge pump includes a high-side p-channel MOSFET(P1) and a low-side n-channel MOSFET(N1) to control the power transfer as shown in Figure 1. During the first half-cycle, N1 turns on and charges flying capacitors C8 (Figure 1). During the second half cycle, N1 turns off and P1 turns on, level shifting C8 by  $V_{SUP}$  volts. The amount of charge transferred to the output is determined by the error amplifier that controls P1's on-resistance. The positive charge-pump regulator's startup can be delayed by  $C_{\text{CDLY P}}$  from negative charge pump reaches 80% of its normal regulated output voltage, the positive charge-pump regulator is enabled. Each time it is enabled, the positive charge-pump regulator goes through a soft-start routine by ramping up its internal reference voltage from 0 to 1.25V. The soft-start period is 2ms (typ). The soft-start feature effectively limits the inrush current during startup. The t<sub>CDLY P</sub> is calculated by the following equation.

$t_{COLY\_P} = \frac{C_{CDLY\_P}}{10uA}$

Fig1. Positive Charge Pump Regulator Block Diagram

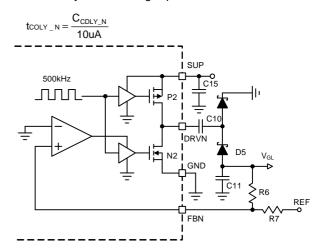

#### **Negative Charge Pump**

The negative charge-pump regulator is typically used to generate the negative supply rail for the TFT LCD gate driver ICs. The output voltage is set with an external resistive voltage-divider from its output to REF with the midpoint connected to FBN. The number of charge pump stages and the setting of the feedback divider determine the output of the negative charge-pump regulator. The charge-pump controller includes a high-side p-channel MOSFET (P2) and a low-side n-channel MOSFET (N2) to control the power transfer as shown in Figure 2.

During the first half cycle, P2 turns on, and flying capacitor C10 charges to  $V_{SUP}$  minus a diode drop. During the second half cycle, P2 turns off, and N2 turns on, level shifting C10. This connects C10 in parallel with reservoir capacitor C11. If the voltage across C11 minus a diode drop is greater than the voltage across C10, charge flows from C11 to C10 until the diode (D5) turns off. The amount of charge transferred from the output is determined by the error amplifier, which controls N2's on-resistance. The negative charge-pump regulator is enabled when the LCD driver step-up regulator reaches 80% of its normal regulated output voltage and  $V_{CDLY N}$  exceed 1V. Each time it is enabled, the negative charge-pump regulator goes through a soft-start routine by ramping down its internal reference voltage from 1.25V to 0mV. The softstart period is 2ms typically. The soft-start feature effectively limits the inrush current during startup. The  $t_{CDLY N}$  is calculated by the following equation.

Fig2. Negative Charge Pump Regulator Block Diagram

### **Function Description**

#### LED Driver Step-up Converter Control Loop

The APW7279 includes a constant frequency currentmode switching regulator. During normal operation, the internal N-channel power MOSFET (Q5) is turned on each cycle when the oscillator sets an internal RS latch and turned off when an internal comparator (ICMP) resets the latch. The peak inductor current at which ICMP resets the RS latch is controlled by the voltage on the COMP node, which is the output of the error amplifier (EAMP). An external current-sense resistor connected between cathode of the lowest LED and ground allows the EAMP to receive a current feedback voltage  $V_{FB\_LED}$  at FB\_LED pin. When the LEDs voltage decreases to cause the LEDs current to decrease, it causes a slightly decrease in  $V_{\mbox{\tiny FB \ LED}}$  relative to the reference voltage, which in turn causes the COMP voltage to increase until the LEDs current reaches the set point. The soft-start period is 2ms (typ). The softstart feature effectively limits the inrush current during startup.

#### LED Driver Current-Limit Protection

The APW7279 monitors the inductor current, flowing through the N-channel MOSFET (Q5), and limits the current peak at current-limit level to prevent loads and the APW7279 from damaging during overload conditions.

#### EN\_LED/Dimming

Driving EN\_LED to ground places the APW7279 in shutdown mode. When in shutdown, the internal power MOSFET (Q5) turns off, all internal circuitry shuts down and the quiescent supply current reduces to 1mA maximum. This pin also could be used as a digital input allowing brightness controlled by using a PWM signal with frequency from 5kHz to 100kHz. The 0% duty cycle of PWM signal corresponds to zero LEDs current and 100% corresponds to full one. If use EN Pin to enable the device, suggestion dimming duty range is from 15% to 100% at 100kHz dimming frequency.

#### EN\_LED/Dimming

In driving LED applications, the feedback voltage on FB\_LED pin falls down if one of the LEDs, in series, is failed. Meanwhile, the converter unceasingly boosts the output voltage like an open-loop operation. Therefore, an over-voltage protection monitoring the output voltage via LX pin prevents the LX and the output voltages from exceeding their maximum voltage ratings. Once the voltage on the LX pin rises above the OVP threshold, the converter stops switching and prevents the output voltage from rising. The converter can work again when the LX voltage falls below the falling of OVP voltage threshold.

#### **Over-Temperature Protection (OTP)**

The over-temperature circuit limits the junction temperature of the APW7279. When the junction temperature exceeds 160°C, a thermal sensor turns off the power MOSFET allowing the devices to cool. The thermal sensor allows the converters to start a soft-start process and regulates the output voltage again after the junction temperature cools by 40°C. The OTP is designed with a 40°C hysteresis to lower the average Junction Temperature (T<sub>J</sub>) during continuous thermal overload conditions increasing the lifetime of the device.

### **Application Information**

#### Input Capacitor Selection

The input capacitor ( $C_{IN}$ ) reduces the current peaks drawn from the input supply and reduces noise injection into the IC. The reflected ripple voltage will be smaller with larger  $C_{IN}$ . For reliable operation, it is recommended to select the capacitor voltage rating at least 1.2 times higher than the maximum input voltage. The capacitors should be placed close to the  $V_{IN}$  and GND.

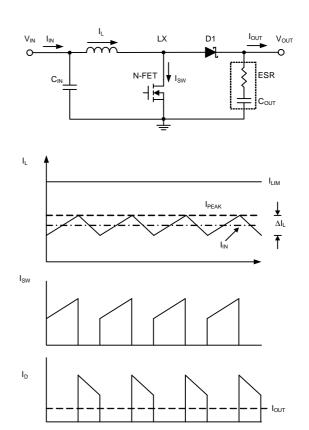

#### **Inductor Selection**

For high efficiencies, the inductor should have a low dc resistance to minimize conduction losses. Especially at high-switching frequencies the core material has a higher impact on efficiency. When using small chip inductors, the efficiency is reduced mainly due to higher inductor core losses. This needs to be considered when selecting the appropriate inductor. The inductor value determines the inductor ripple current. The larger the inductor value, the smaller the inductor ripple current and the lower the conduction losses of the converter. Conversely, larger inductor values cause a slower load transient response. A reasonable starting point for setting ripple current. The recommended inductor value can be calculated as below:

$$L \geq (\frac{V_{IN}}{V_{OUT}})^2 \frac{V_{OUT} - V_{IN}}{F_{SW} \cdot I_{OUT}(_{MAX})} (\frac{\eta}{\frac{\Delta I_L}{I_L}})$$

Where

VIN = input voltage

VOUT = output voltage

F<sub>sw</sub> = switching frequency in MHz

$I_{out}$  = maximum output current in amp.

$\eta = Efficiency$

$\Delta I_L / I_{L(AVG)} = (0.3 \text{ to } 0.5 \text{ typical})$

To avoid saturation of the inductor, the inductor should be rated at least for the maximum input current of the converter plus the inductor ripple current. The maximum input current is calculated as below:

$$I_{IN(MAX)} = \frac{I_{OUT(MAX)} - V_{OUT}}{V_{IN} \cdot \eta}$$

Copyright © ANPEC Electronics Corp. Rev. A.3 - Nov., 2017 The peak inductor current is calculated as follow equation:

$$I_{\text{PEAK}} = I_{\text{IN(MAX)}} + \frac{1}{2} \times \frac{V_{\text{IN}} \cdot (V_{\text{OUT}} - V_{\text{IN}})}{V_{\text{OUT}} \cdot L \cdot F_{\text{SW}}}$$

### **Application Information**

#### **Output Capacitor Selection**

The current-mode control scheme of the APW7279 allows the use of tiny ceramic capacitors. The higher capacitor value provides the good load transients response. Ceramic capacitors with low ESR values have the lowest output voltage ripple and are recommended. If required, tantalum capacitors may be used as well. The output ripple is the sum of the voltages across the ESR and the ideal output capacitor.

$$\Delta \mathsf{V}_{\mathsf{OUT}} = \Delta \mathsf{V}_{\mathsf{ESR}} + \Delta \mathsf{V}_{\mathsf{COUT}}$$

$\Delta V\text{esr}\cong \text{Ipeak}\cdot \text{Resr}$

Where  $I_{PEAK}$  is the peak inductor current. For ceramic capacitor application, the output voltage ripple is dominated by the  $\Delta V_{COUT}$ . When choosing the input and output ceramic capacitors, the X5R or X7R with their good temperature and voltage characteristics are recommended.

#### Setting the LED Current

In Typical Application Circuit, the converter regulates the voltage on FB\_LED pin, connected with the cathode of the lowest LED and the current- sense resistor RFB at  $V_{REF}$ . Therefore, the current ( $I_{LED}$ ), flowing via the LEDs and the RFB, is calculated by the following equation:

$$I_{\text{LED}} = \frac{V_{\text{REF}}}{R_{\text{FB}}}$$

#### Layout Consideration

For all switching power supplies, the layout is an important step in the design; especially at high peak currents and switching frequencies. If the layout is not carefully done, the regulator might show noise problems and duty cycle jitter.

1. The input capacitor C1, C5 and C14 should be placed close to the VIN/SUP and GND. Connecting the capacitor with VIN/SUP and GND pins by short and wide tracks for filtering and minimizing the input voltage ripple.

2. The inductor and Schottky diode should be placed as close as possible to the LX\_LCD/LX\_LED pin to minimize length of the copper tracks as well as the noise coupling into other circuits.

3. A star ground connection or ground plane minimizes ground shifts and noise is recommended.

4. Since the feedback pin (FBx) and network is a high impedance circuit the feedback network should be routed away from the inductor. The feedback pin and feedback network should be shielded with a ground plane or trace to minimize noise coupling into this circuit.

Figure : Recommended Minimum Footprint

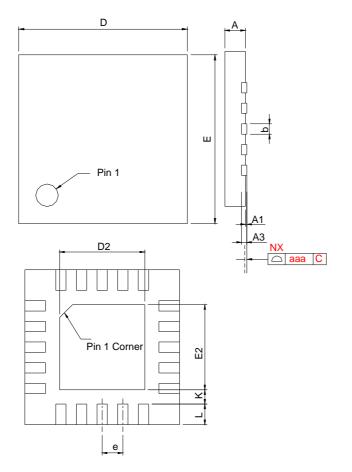

## Package Information

### TQFN3x3-20

| Ş      |        | TQFN  | 3x3-20 |       |

|--------|--------|-------|--------|-------|

| SYMBOL | MILLIM | ETERS | INCH   | ES    |

| Õ      | MIN.   | MAX.  | MIN.   | MAX.  |

| А      | 0.70   | 0.80  | 0.028  | 0.031 |

| A1     | 0.00   | 0.05  | 0.000  | 0.002 |

| A3     | 0.20   | REF   | 0.008  | REF   |

| b      | 0.15   | 0.25  | 0.006  | 0.010 |

| D      | 2.90   | 3.10  | 0.114  | 0.122 |

| D2     | 1.50   | 1.80  | 0.059  | 0.071 |

| Е      | 2.90   | 3.10  | 0.114  | 0.122 |

| E2     | 1.50   | 1.80  | 0.059  | 0.071 |

| е      | 0.40   | BSC   | 0.016  | BSC   |

| L      | 0.30   | 0.50  | 0.012  | 0.020 |

| к      | 0.20   |       | 0.008  |       |

| aaa    | 0.     | 08    | 0.00   | 3     |

Note : 1. Followed from JEDEC MO-220 WEEE

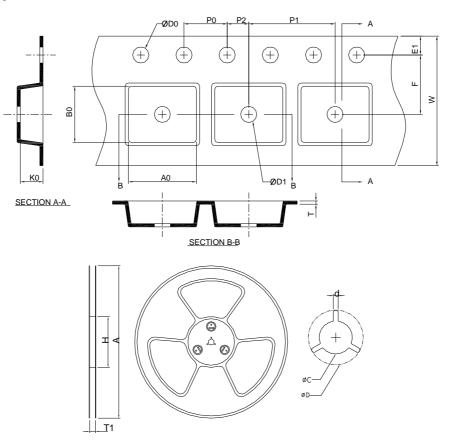

## **Carrier Tape & Reel Dimensions**

| Application | Α        | Н        | T1                 | С                  | d        | D                 | W         | E1        | F         |

|-------------|----------|----------|--------------------|--------------------|----------|-------------------|-----------|-----------|-----------|

|             | 330±2.00 | 50 MIN.  | 12.4+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 12.0±0.30 | 1.75±0.10 | 5.5±0.05  |

| TQFN3x3-20  | P0       | P1       | P2                 | D0                 | D1       | Т                 | A0        | B0        | K0        |

|             | 4.0±0.10 | 8.0±0.10 | 2.0±0.05           | 1.5+0.10<br>-0.00  | 1.5 MIN. | 0.6+0.00<br>-0.40 | 3.30±0.20 | 3.30±0.20 | 1.00±0.20 |

(mm)

### **Devices Per Unit**

| Package Type | Unit        | Quantity |

|--------------|-------------|----------|

| TQFN3x3-20   | Tape & Reel | 3000     |

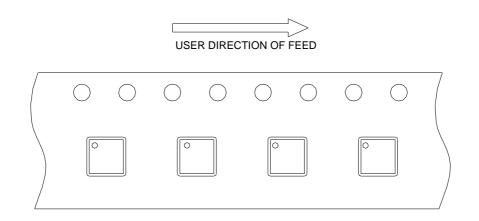

### **Taping Direction Information**

TQFN3x3-20

### **Classification Profile**

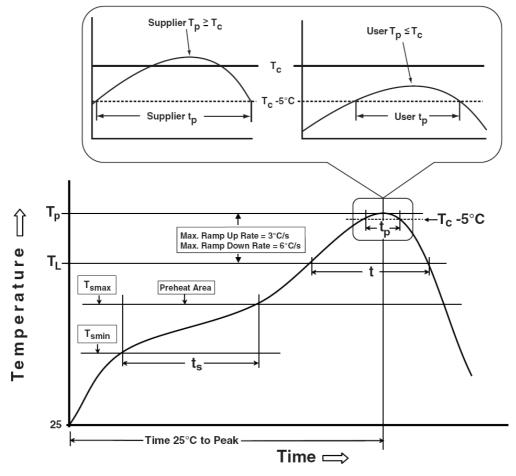

### **Classification Reflow Profiles**

| Profile Feature                                                                                                                                                                                                                             | Sn-Pb Eutectic Assembly            | Pb-Free Assembly                   |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|--|--|--|

| $\begin{array}{c} \textbf{Preheat \& Soak} \\ \textbf{Temperature min (T_{smin})} \\ \textbf{Temperature max (T_{smax})} \\ \textbf{Time (T_{smin} to T_{smax}) (t_s)} \end{array}$                                                         | 100 °C<br>150 °C<br>60-120 seconds | 150 °C<br>200 °C<br>60-120 seconds |  |  |  |

| Average ramp-up rate<br>(T <sub>smax</sub> to T <sub>P</sub> )                                                                                                                                                                              | 3 °C/second max.                   | 3°C/second max.                    |  |  |  |

| Liquidous temperature $(T_L)$<br>Time at liquidous $(t_L)$                                                                                                                                                                                  | 183 °C<br>60-150 seconds           | 217 °C<br>60-150 seconds           |  |  |  |

| Peak package body Temperature (T <sub>p</sub> )*                                                                                                                                                                                            | See Classification Temp in table 1 | See Classification Temp in table 2 |  |  |  |

| Time $(t_P)^{**}$ within 5°C of the specified classification temperature $(T_c)$                                                                                                                                                            | 20** seconds                       | 30** seconds                       |  |  |  |

| Average ramp-down rate ( $T_p$ to $T_{smax}$ )                                                                                                                                                                                              | 6 °C/second max.                   | 6 °C/second max.                   |  |  |  |

| Time 25°C to peak temperature                                                                                                                                                                                                               | 6 minutes max.                     | 8 minutes max.                     |  |  |  |

| * Tolerance for peak profile Temperature (T <sub>p</sub> ) is defined as a supplier minimum and a user maximum.<br>** Tolerance for time at peak profile temperature (t <sub>p</sub> ) is defined as a supplier minimum and a user maximum. |                                    |                                    |  |  |  |

Table 1. SnPb Eutectic Process – Classification Temperatures (Tc)

| Package   | Volume mm <sup>3</sup> | Volume mm <sup>3</sup> |

|-----------|------------------------|------------------------|

| Thickness | <350                   | <sup>3</sup> 350       |

| <2.5 mm   | 235 °C                 | 220 °C                 |

| ≥2.5 mm   | 220 °C                 | 220 °C                 |

Table 2. Pb-free Process – Classification Temperatures (Tc)

| Package<br>Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br>350-2000 | Volume mm <sup>3</sup><br>>2000 |

|----------------------|--------------------------------|------------------------------------|---------------------------------|

| <1.6 mm              | 260 °C                         | 260 °C                             | 260 °C                          |

| 1.6 mm – 2.5 mm      | 260 °C                         | 250 °C                             | 245 °C                          |

| ≥2.5 mm              | 250 °C                         | 245 °C                             | 245 °C                          |

### **Reliability Test Program**

| Test item     | Method             | Description                            |

|---------------|--------------------|----------------------------------------|

| SOLDERABILITY | JESD-22, B102      | 5 Sec, 245°C                           |

| HOLT          | JESD-22, A108      | 1000 Hrs, Bias @ T <sub>j</sub> =125°C |

| PCT           | JESD-22, A102      | 168 Hrs, 100%RH, 2atm, 121°C           |

| тст           | JESD-22, A104      | 500 Cycles, -65°C~150°C                |

| НВМ           | MIL-STD-883-3015.7 | VHBM≧2KV                               |

| MM            | JESD-22, A115      | VMM≧200V                               |

| Latch-Up      | JESD 78            | 10ms, 1 <sub>tr</sub> ≧100mA           |

### **Customer Service**

Anpec Electronics Corp. Head Office : No.6, Dusing 1st Road, SBIP,

Hsin-Chu, Taiwan, R.O.C. Tel : 886-3-5642000 Fax : 886-3-5642050

Taipei Branch :

2F, No. 11, Lane 218, Sec 2 Jhongsing Rd., Sindian City, Taipei County 23146, Taiwan Tel : 886-2-2910-3838 Fax : 886-2-2917-3838