## 300 - 480 MHz OOK Receiver with 3.0 - 5.5 V Supply Power

### **Features**

■ Frequency range: 300 - 480 MHz

■ Data rate: 1 - 5 kbps

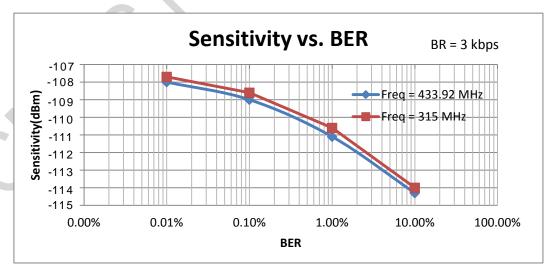

Sensitivity: -109 dBm (3 kbps), 0.1% BER

■ Receiver bandwidth: 510 kHz @ 433.92 MHz

Image rejection ratio: 33 dB

Supporting input signal up to 10 dBm

Operating independently with antenna in and data out

■ Supply voltage: 3.0 – 5.5 V

■ Low power consumption: 5.3 mA @ 315 MHz

■ SOP8 packaging

■ RoHS compliant

## **Application**

- Home and building automation control

- Infrared receiver replacement

- Industrial monitoring and control

- Wireless meter reading

- Wireless lighting control system

- Wireless alarm and security system

- Access control system with remote control

### **Ordering Information**

| Product Model | Package   | Minimum Order Quantity |

|---------------|-----------|------------------------|

| CMT2220LY-ESR | SOP8/Tape | 2,500 pcs              |

# **Description**

CMT2220LY new-generation, low-power, are high-performance, plug-and-play based OOK RF receiver with no need for register configuration, fitting for wireless receiving applications within 300 - 480 MHz ISM band. The CMT2220LY supports a data rate range of 1 - 5 kbps, ideal for pairing with encoder or MCU based low-cost transmitters. Operating in a supply voltage range of 3.0 - 5.5 V, the chip remains stable receiving performance with no significant performance change in different power supply voltage within this voltage range. It consumes only a current of 5.7 mA while achieving a receiving sensitivity of -110 dBm @ 433.92 MHz. The chip can operate at the commonly used 315 MHz frequency or other RF frequency points within the applicable frequency band through selecting crystals with different frequencies. The CMT2220LY receiver cooperating with CMT211x / 5x / 8x transmitters can fulfill cost-effective RF application solutions conveniently.

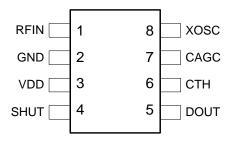

**CMT2220LY Pin Arrangement**

### **Table of Contents**

| 1  | Elec  | ctrical Specifications                   | 3  |

|----|-------|------------------------------------------|----|

|    | 1.1   | Recommended Operating Conditions         | 3  |

|    | 1.2   | Absolute Maximum Ratings                 | 3  |

|    | 1.3   | Receiver Specification                   | 4  |

|    | 1.4   | Crystal Oscillator Specification         | 5  |

| 2  | Pin I | Description                              | 6  |

| 3  | Турі  | oical Application Schematic              | 7  |

| 4  | Турі  | oical Performance                        | 9  |

| 5  | Fund  | nction Description                       | 11 |

|    | 5.1   | Crystal Frequency and RF Frequency Point | 11 |

|    | 5.2   | Receiver IF Bandwidth                    | 11 |

|    | 5.3   | Considerations of CAGC and CTH Selection | 11 |

| 6  | Orde  | lering Information                       | 12 |

|    |       | ckaging Information                      |    |

| 8  | Тор   | Marking                                  | 14 |

| 9  | Revi  | vise History                             | 15 |

| 10 | Con   | ntacts                                   | 16 |

## 1 Electrical Specifications

If nothing else stated, the test conditions are  $V_{DD}$ = 5.0 V,  $T_{OP}$ = 25 °C,  $F_{RF}$  = 433.92 MHz, sensitivity being measured by receiving a PN9 sequence, matching to 50  $\Omega$  impedance and 0.1% BER. All measurement results are obtained using the evaluation board CMT2220LY-EM if nothing else stated.

### 1.1 Recommended Operating Conditions

**Table 1. Recommended Operating Conditions**

| Parameter                | Symbol          | Condition   | Min. | Тур. | Max. | Unit       |

|--------------------------|-----------------|-------------|------|------|------|------------|

| Operating supply voltage | $V_{DD}$        | -40°C∼+85°C | 3.0  |      | 5.5  | V          |

| Operating temperature    | T <sub>OP</sub> |             | -40  |      | 85   | $^{\circ}$ |

| RF supply voltage slope  | V <sub>SL</sub> |             | 1    |      |      | mV/us      |

### 1.2 Absolute Maximum Ratings

Table 2. Absolute Maximum Ratings[1]

| Parameter                 | Symbol           | Condition                     | Min. | Тур.                  | Max. |

|---------------------------|------------------|-------------------------------|------|-----------------------|------|

| Supply voltage            | $V_{DD}$         |                               | -0.3 | 5.5                   | V    |

| Interface voltage         | V <sub>IN</sub>  |                               | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| Junction temperature      | TJ               | 1                             | -40  | 125                   | °C   |

| Storage temperature       | T <sub>STG</sub> |                               | -50  | 150                   | °C   |

| Soldering temperature     | T <sub>SDR</sub> | Lasts for at least 30 seconds |      | 255                   | °C   |

| ESD rating <sup>[2]</sup> |                  | Human body model (HBM)        | -2   | 2                     | kV   |

| Latch-up current          |                  | @ 85 ℃                        | -100 | 100                   | mA   |

#### Notes:

- [1]. Exceeding the Absolute Maximum Ratings may cause permanent damage to the equipment. This value is a pressure rating and does not imply that the function of the equipment is affected under this pressure condition, but if it is exposed to absolute maximum ratings for extended periods of time, it may affect equipment reliability.

- [2]. The CMT2220LY is a high performance RF integrated circuit. The operation and assembly of this chip should only be performed on a workbench with good ESD protection.

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent performance degradation or loss of functionality.

### 1.3 Receiver Specification

**Table 3. Receiver Specification**

| Parameter                         | Symbol                | Condition                                                                                               |                              | Min. | Тур. | Max. | Unit |

|-----------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------|------------------------------|------|------|------|------|

| Frequency range                   | F <sub>RF</sub>       | Through choosing crystals with diff                                                                     | erent frequencies            | 300  |      | 480  | MHz  |

| Data rate                         | DR                    |                                                                                                         |                              | 1    |      | 5    | kbps |

| Complete its                      | S <sub>315</sub>      | F <sub>RF</sub> = 315 MHz, DR = 3 kbps, BER                                                             | a = 0.1%                     | -110 | -109 | -107 | dBm  |

| Sensitivity                       | S <sub>433.92</sub>   | F <sub>RF</sub> = 433.92 MHz, DR = 3 kbps, BER = 0.1%                                                   |                              |      | -109 | -107 | dBm  |

| Operating current                 | I <sub>DD315</sub>    | F <sub>RF</sub> = 315 MHz                                                                               | F <sub>RF</sub> = 315 MHz    |      |      |      | mA   |

|                                   | I <sub>DD433.92</sub> | F <sub>RF</sub> = 433.92 MHz                                                                            | F <sub>RF</sub> = 433.92 MHz |      | 5.7  |      | mA   |

| Shutdown current                  | I <sub>SHUT</sub>     | SHUT pin keeps high level                                                                               |                              |      | 0.3  |      | uA   |

| Receiver bandwidth                | BW <sub>315</sub>     | F <sub>RF</sub> = 315 MHz                                                                               |                              |      | 370  |      | kHz  |

|                                   | BW <sub>433.92</sub>  | F <sub>RF</sub> = 433.92 MHz                                                                            |                              |      | 510  |      | kHz  |

| Receiver startup time [1]         | T <sub>START-UP</sub> | Time duration from the time point of changes from high level to low level when received data is output. |                              | 3    | 4    |      | ms   |

|                                   |                       | CAGC/CTH capacitance value <sup>[2]</sup>                                                               | 4.7uF/0.47uF                 |      | 80   |      |      |

|                                   |                       |                                                                                                         | 2.2uF/0.1uF                  |      | 28   |      |      |

| Receiver startup time [1]         | T <sub>START-UP</sub> | point when SHUT pin changes                                                                             | 1uF/0.1uF                    |      | 15   |      | ms   |

|                                   |                       | from high level to low level to the<br>time point when received data is<br>output.)                     | 0.47uF/0.047uF               |      | 4    |      |      |

| Saturation input level            | P <sub>LVL</sub>      |                                                                                                         |                              |      | 10   |      | dBm  |

| Input third-order Intercept point | IIP3                  | Two-tone test with frequency offset between 1 and 2 MHz, maximum system gain setting.                   |                              |      | -29  |      | dBm  |

| Anti-blocking                     |                       | ±1 MHz, continuous wave jamming                                                                         | 9                            |      | 32   |      | dB   |

|                                   | ВІ                    | ±2 MHz, continuous wave jamming ±10 MHz, continuous wave jamming                                        |                              |      | 42   |      | dB   |

|                                   |                       |                                                                                                         |                              |      | 61   |      | dB   |

| Anti-co-channel-interference      | CCR                   |                                                                                                         |                              |      | -11  |      | dB   |

| Image rejection ratio             | IRR                   |                                                                                                         |                              |      | 33   |      | dB   |

#### Notes:

- [1]. The receiver startup time is affected much by the CAGC capacitance value as well as the received signal strength. The less the signal strength, the longer the startup time.

- In AC to DC power supply systems, if an application allows a longer chip startup time, users can choose a CAGC with larger value. For instance, 4.7 uF is an appropriate value. In this case the chip startup time is around 70 ms in the condition of receiving signal strength being near to receiving sensitivity.

- In battery-powered applications, it is appropriate to select CAGC as 1 uF. In this case the chip startup time is around 8

ms in the condition of receiving signal strength being near to receiving sensitivity. If it requires a shorter chip startup

time, users can choose a slightly smaller CAGC value based on practical requirements.

- [2]. The different receiver start up time test values according to different CAGC and CTH capacitance values are provided in the table.

## 1.4 Crystal Oscillator Specification

**Table 4. Crystal Oscillator Specification**

| Parameter                           | Symbol                  | Condition                    | Min. | Тур.     | Max. | Unit |

|-------------------------------------|-------------------------|------------------------------|------|----------|------|------|

| On rated from the second            | F <sub>XTAL315</sub>    | F <sub>RF</sub> = 315 MHz    |      | 9.81563  |      | MHz  |

| Crystal frequency                   | F <sub>XTAL433.92</sub> | F <sub>RF</sub> = 433.92 MHz |      | 13.52127 |      | MHz  |

| Crystal frequency tolerance [1]     |                         |                              |      | ±20      |      | ppm  |

| Load capacitance <sup>[2]</sup>     | C <sub>LOAD</sub>       | 49USSMD or 49S packaging     |      | 15       |      | pF   |

| Crystal equivalent resistance       | Rm                      |                              |      |          | 60   | Ω    |

| Crystal startup time <sup>[3]</sup> | T <sub>XTAL</sub>       |                              |      | 400      |      | us   |

#### Notes:

- [1]. It involves:(1) initial tolerance, (2) crystal loading, (3) aging, and (4) temperature changing. The acceptable crystal frequency tolerance is subject to the bandwidth of the receiver and the RF tolerance between the receiver and its paired transmitter.

- [2]. As the crystal parasitic capacitance value differs in different crystal packaging type, it is recommended to select a crystal with appropriate load capacitance value according to the packaging type used.

- [3]. This parameter is to a large degree crystal dependent.

Rev 1.0 | 5/16

# 2 Pin Description

Figure 1. CMT2220LY Pin Arrangement Diagram

Table 5. CMT2220LY Pin Description

| Pin# | Pin Name | I/O | Description                                                                                                       |

|------|----------|-----|-------------------------------------------------------------------------------------------------------------------|

| 1    | RFIN     | 1   | RF signal input pin, connecting matching network externally.                                                      |

| 2    | GND      | 1   | Ground                                                                                                            |

| 3    | VDD      | I   | 3.0 - 5.5 V supply power input.                                                                                   |

| 4    | SHUT     | I   | Chip shutdown control pin, connecting high level to disable the chip and connecting low level to enable the chip. |

| 5    | DOUT     | 0   | Received data output                                                                                              |

| 6    | СТН      |     | Received data filtering, connecting filtering capacitor externally.                                               |

| 7    | CAGC     | , l | Automatic gain control pin, connecting filtering capacitor externally.                                            |

| 8    | xosc     | ı   | Crystal oscillator input pin, connecting crystal externally.                                                      |

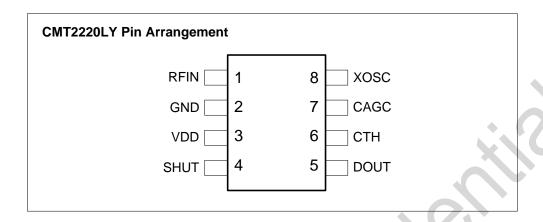

# 3 Typical Application Schematic

Figure 2. CMT2220LY Typical Application Schematic

Table 6. Typical Application BOM (Matching to 315 / 433.92 MHz)

| Label             | Description                                                         | Compone            | ent Value        | Unit | Committee |  |

|-------------------|---------------------------------------------------------------------|--------------------|------------------|------|-----------|--|

| Labei             | Description                                                         | 315 MHz            | 433.9 2MHz       | Onit | Supplier  |  |

| X1                | Crystal, ±20 ppm, 49USSMD                                           | 9.81563            | 13.52127         | МН   | EPSON     |  |

| L1                | Matching network inductor, ± 10%, 0603 multilayer chip inductor     | 47                 | 27               | nH   | Sunlord   |  |

| L2                | Matching network inductor, ± 10%, 0603 multilayer chip inductor     | 68                 | 39               | nΗ   | Sunlord   |  |

| C1                | Matching network capacitor, ±0.25 pF, 0402 NP0, 50 V                | 4.7                | 2.7              | pF   | ·         |  |

| C2                | Matching network capacitor, ±0.25 pF, 0402 NP0, 50 V                | 3                  |                  | pF   | -         |  |

| C3                | Supply power filtering capacitor, ±20%, 0603 X7R, 25 V              | 0                  | .1               | uF   | -         |  |

| C4 <sup>[1]</sup> | Gain control filtering capacitor, ±20%, 0603 X7R, 25 V              | 4.7 <sup>[1]</sup> | 1 <sup>[1]</sup> | uF   | -         |  |

| C5                | Data filtering capacitor, ±20%, 0603 X7R, 25 V                      | 0,                 | 47               | uF   | -         |  |

| R1                | Resistor, 5%, 1/8W, 0603                                            |                    | 17               | Ω    | -         |  |

| U1                | CMT2220LY, 300 - 480 MHz OOK receiver with 3.0 - 5.5 V supply power |                    | <b>)</b>         | -    | CMOSTEK   |  |

#### Notes:

Rev 1.0 | 8/16 www.cmostek.com

<sup>[1].</sup> The value of the gain control filtering capacitor will affect the receiver startup time much. Users can select an appropriate gain control filter capacitor (CAGC) according to the notes information specified in <a href="Table 3">Table 3</a>.

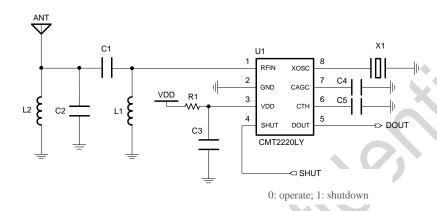

# 4 Typical Performance

Figure 3. Rx Current vs. VDD

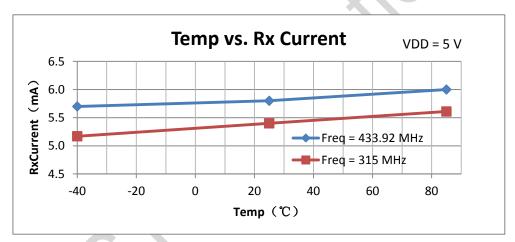

Figure 4. Rx Current vs. Operating Temperature

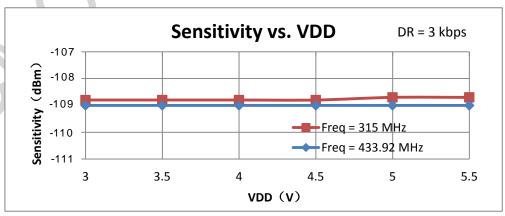

Figure 5. Sensitivity vs. VDD

Rev 1.0 | 9/16 www.cmostek.com

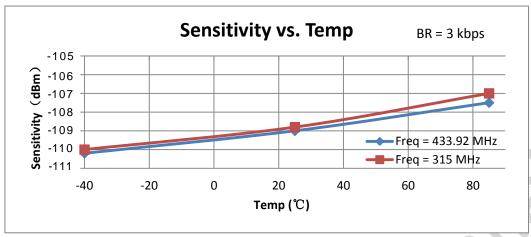

Figure 6. Sensitivity vs. Operating Temperature

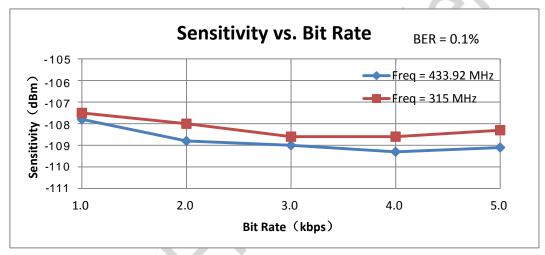

Figure 7. Sensitivity vs. Bit Rate

Figure 8. Sensitivity vs. BER

## **5 Function Description**

As an integrated receiver with digital-analog hybrid design, the CMT2220LY chip applies LNA + Mixer + IF Filter + Limiter + PLL low-IF receiving architecture. It requires to connect 2 capacitors CAGC and CTH externally to assist in fulfilling the stability of the automatic gain control loop and the function of received data filtering.

### 5.1 Crystal Frequency and RF Frequency Point

The CMT2220LY applies a single-ended crystal oscillation circuit with the load capacitor required for crystal oscillation integrated in the chip. It is recommended to use a crystal with an accuracy of  $\pm$  20 ppm, an equivalent resistance of less than 60  $\Omega$ , and a load capacitance of 15 pF. Since crystal parasitic capacitance differs in different packaging specifications, users should pay more attention when selecting crystals to avoid receiver performance degradation caused by too much variance between the actual oscillation frequency and the target frequency value.

The CMT2220LY can operate in any frequency point within the free range 300 - 480 MHz. Users can fulfill different frequency points through selecting corresponding crystals. For instance, for a device operating at 433.92 MHz, the required crystal frequency is 13.52127 MHz. The formula between a specific RF operating frequency and the corresponding crystal frequency is as follows.

$$F_{XTAL} = \frac{13.52127}{433.92} F_{RF}$$

For example, for a CMT2220LY chip desired to operate at 315 MHz, the required crystal frequency is 9.81563 MHz.

### 5.2 Receiver IF Bandwidth

When the chip is operating at 433.92 MHz, the corresponding IF bandwidth is 510 kHz. The IF bandwidth is adjusted automatically with same proportion according to selected crystal frequency. The formula between a specific RF operating frequency and the corresponding IF bandwidth is as follows.

$$BW_{RF} = 1.175332e^{-3} * F_{RF}$$

For example the IF bandwidth is adjusted to 370 kHZ when the chip is operated at 315 MHz.

### 5.3 Considerations of CAGC and CTH Selection

The CAGC pin is the port for automatic gain control of receiving link, connecting with a filtering capacitor externally. The value of CAGC will affect the chip startup time, namely the larger the CAGC value, the longer the startup time. Suggest users choose a larger capacitor value in AC to DC applications while choose 1 uF or slightly smaller one in DC power supply applications.

Moreover, users should make sure the CTH of CMT2220LY is connected externally to a data filtering capacitor. Users can select the capacitance value as listed in Table 6.

Rev 1.0 | 11/16

## 6 Ordering Information

**Table 7. Ordering Information**

| Model                        | Description                                              | Packaging | Packing<br>Option | Operating<br>Condition       | Minimum<br>Order Quantity |

|------------------------------|----------------------------------------------------------|-----------|-------------------|------------------------------|---------------------------|

| CMT2220LY-ESR <sup>[1]</sup> | 300 - 480 MHz OOK receiver with 3.0 - 5.5 V supply power | SOP8      | Tape and Reel     | 3.0 - 5.5 V,<br>- 40 ~ 85 °C | 2,500                     |

#### Notes:

[1]. CMT2220LY refers to model CMT2220LY.

E refers to extended Industrial product rating, which supports temperature range from -40 to +85 °C.

S refers to the packaging type SOP8.

R refers to tape and reel packing type, and the minimum ordering quantity (MOQ) is 2,500 pieces.

Please visit <u>www.cmostek.com</u> for more product/product line information.

Please contact <a href="mailto:sales@cmostek.com">sales@cmostek.com</a> or your local sales representative for sales or pricing requirements.

# 7 Packaging Information

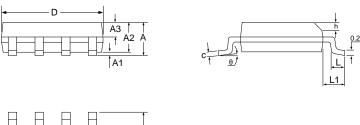

The packaging information of CMT2220LY is shown in the below figure.

Figure 9. SOP8 Packaging

Table 8. SOP8 Packaging Scale

|        |      | Scale (mm) |       |

|--------|------|------------|-------|

| Symbol | Min. | Тур.       | Max.  |

| Α      | -    | -          | 1.75  |

| A1     | 0.10 | -          | 0.225 |

| A2     | 1.30 | 1.40       | 1.50  |

| A3     | 0.60 | 0.65       | 0.70  |

| b      | 0.39 | -          | 0.48  |

| c      | 0.21 | -          | 0.26  |

| D      | 4.70 | 4.90       | 5.10  |

| E      | 5.80 | 6.00       | 6.20  |

| E1     | 3.70 | 3.90       | 4.10  |

| е      |      | 1.27 BSC   |       |

| h      | 0.25 | -          | 0.50  |

| L      | 0.50 | -          | 0.80  |

| L1     |      | 1.05 BSC   |       |

| θ      | 0    | -          | 8°    |

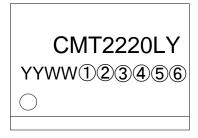

# 8 Top Marking

Figure 10. CMT2220LY Top Marking

Table 9. Top Marking Information

| Marking Method | Laser                                                                                                                                                       |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 1 Mark     | Diameter of the circle = 0.5 mm                                                                                                                             |

| Font Height    | 0.6 mm, align right                                                                                                                                         |

| Font Width     | 0.3 mm                                                                                                                                                      |

| Line 1 Marking | CMT2220LY referring to model CMT2220LY                                                                                                                      |

| Line 2 Marking | YYWW is the date code assigned by the packaging factory. YY is the last 2 digits of the year. WW is the working week.  ①②③④⑤⑥ is the internal tracing code. |

# 9 Revise History

**Table 10. Revise History Records**

| Version No. | Chapter            | Description                                                                             | Date       |

|-------------|--------------------|-----------------------------------------------------------------------------------------|------------|

| 0.5         | All                | Initial version                                                                         | 2020-03-12 |

| 0.6         | All                | Add description information                                                             | 2020-04-15 |

| 0.7         | 3                  | Update R1 resistor description in Table 6                                               | 2020-05-14 |

| 0.8         | All                | Document refining                                                                       | 2020-07-24 |

| 0.9         | First page, 1.3, 4 | Update performance parameter values.                                                    | 2021-06-30 |

| 1.0         | 1.3                | Add data for receiver start up time according to different CAGA CTH capacitance values. | 2021-09-15 |

### 10 Contacts

CMOSTEK Microelectronics Co., Ltd. Shenzhen Branch

Address: 30th floor of 8th Building, C Zone, Vanke Cloud City, Xili Sub-district, Nanshan, Shenzhen, GD, P.R. China

**Tel:** +86-755-83231427

Post Code: 518071

Sales: sales@cmostek.com

Supports: support@cmostek.com

Website: www.cmostek.com

#### Copyright. CMOSTEK Microelectronics Co., Ltd. All rights are reserved.

The information furnished by CMOSTEK is believed to be accurate and reliable. However, no responsibility is assumed for inaccuracies and specifications within this document are subject to change without notice. The material contained herein is the exclusive property of CMOSTEK and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of CMOSTEK. CMOSTEK products are not authorized for use as critical components in life support devices or systems without express written approval of CMOSTEK. The CMOSTEK logo is a registered trademark of CMOSTEK Microelectronics Co., Ltd. All other names are the property of their respective owners.