### TTR011 (1K ROM MCU)

Page

### Preliminary

# TTR011

## § Features

- ◆ Tontek RISC 4-bit CPU core with 2-level stacks

- ◆ All instructions are one word length

- ◆ Most of instructions need one machine cycle (2 CPU clocks) except read table instruction RTB

- Advanced CMOS process

- ♦ 1Kx16 OTP ROM

- ♦ 56x4 SRAM

- ◆ Operating voltage: 2.0V~5.50V

- ◆ Two high-speed clock OSCH selectable: on-chip 910kHz oscillator, external RC oscillator

- One low-speed clock OSCL: on-chip 16kHz oscillator

- Power-on default is low speed mode

- Four operation modes

- STOP mode: CPU, OSCH and OSCL stop

- GREEN mode: CPU and OSCH stop; OSCL active for periodical ADC measure and wake-up

- Low power mode: OSCH stop, OSCL active for CPU and peripheral circuit

- Normal mode: Both OSCH and OSCL active, CPU clock from OSCH

- ♦ 11 I/O pins + 1 input

- PA, PB and PC can be configured as wake-up input pins

- PB and PC can be programmed as input pins with pull-high resistors

- Four input pins can be defined as external interrupt input pins

- Shared with 5 ADC input channels and 1 buzzer output

- ◆ 5-channel 4-bit ADC

- One time base timer

- In GREEN mode, its clock is from the overflow of timer/counter B and its overflow wake up CPU from GREEN mode.

- In other mode, its clock is from OSCL

- Two 8-bit timer/counter

- One 8-bit timer/counter B with two sets of auto-preload data to generate periodic waveform for buzzer function.

- In GREEN mode, the overflow of timer B will trigger ADC check procedure and increment of time base timer 1.

- One 8-bit timer/counter C with auto reload function

### TTR011 (1K ROM MCU)

2013/07/10

#### 2 of 41

Page

Version 3.2

### Preliminary

#### Eight interrupts:

Title

- Internal interrupts: ADC, timer/counter B, timer/counter C, time base timer

- External interrupts: INT0, INT1, INT2, INT3

- ◆ Two on-chip system protections:

- Watch dog timer(WDT) circuit

- 4-level low voltage detector: 2.0V, 2.2V, 3.3V, 4.5V

- MCU executes next address instruction or interrupt servicing after wake up

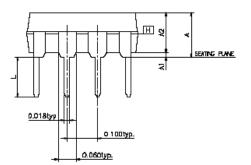

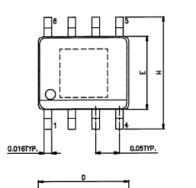

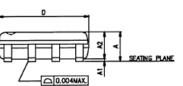

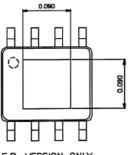

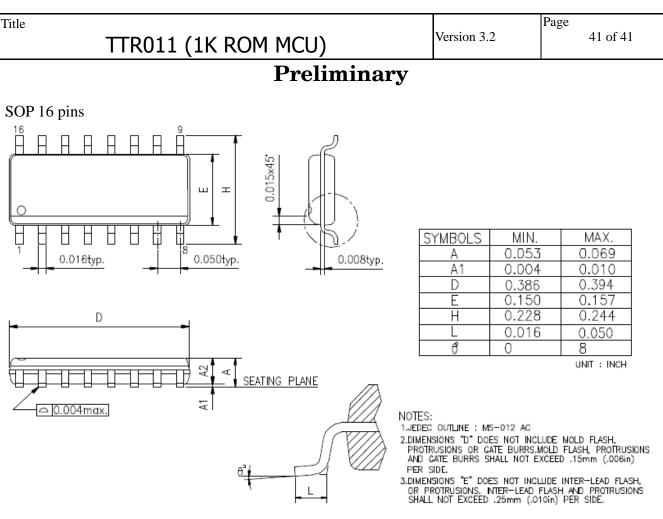

- ◆ Package: SOP 8/16 pins

§ Pin configuration

## § Applications

TTR011 can be used in alarm systems in supermarkets, discount stores, etc.

#### INT2/VPP/PC0 1 16 PC1/INT3 INT2/VPP/PC0 1 8 PC2 INTO/AD0/PA0 2 15 PC2 INTO/ADO/PA0 2 7 PC3 INT1/AD1/PA1 3 14 PC3 INT1/AD1/PA1 3 6 PB3/BZ AD2/PA2 4 13 PB3/BZ VSS 5 VDD 4 AD3/PA3 5 12 PB2/OSCI SOP8-FO8 VSS 6 11 PB1 VDD 7 10 PB0/AD4 NC 8 9 NC SOP16-HOB

## § Ordering Form:

- a. Package form : TTR011-zzz

- b. Chip form :

- c. Wafer base :

ns ed in alarm systems i

| Dealiminary         |             |         |  |  |  |  |

|---------------------|-------------|---------|--|--|--|--|

| TTR011 (1K ROM MCU) | Version 3.2 | 3 of 41 |  |  |  |  |

| Title               |             | Page    |  |  |  |  |

77

### Preliminary

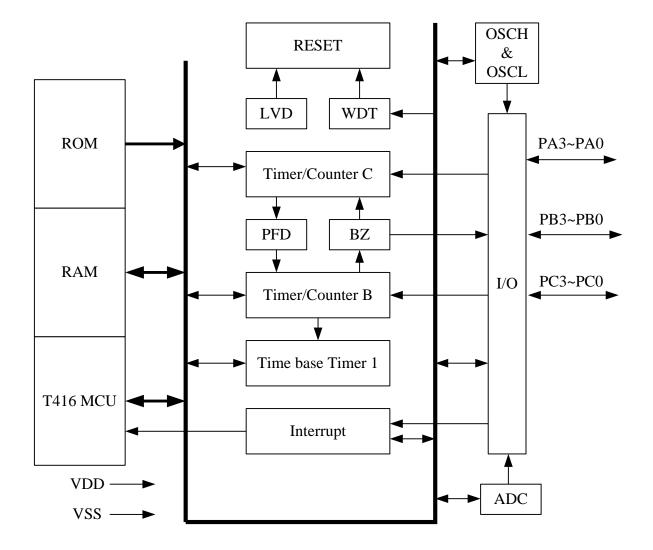

## § Block Diagram

#### Figure 1: Block diagram

## TTR011 (1K ROM MCU)

Version 3.2

Page

### Preliminary

# § Pin Descriptions

| Pin Name        | Function | Туре  | Pin Description                                                                                                                             |  |  |  |  |  |  |  |

|-----------------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                 | PA0      | I/O   | Input or output port determined by software                                                                                                 |  |  |  |  |  |  |  |

| PAO/INT0/AD0    | INT0     | Ι     | External interrupt input as input mode determined                                                                                           |  |  |  |  |  |  |  |

|                 | AD0      | Ι     | ADC input channel configured by software                                                                                                    |  |  |  |  |  |  |  |

|                 | PA1      | I/O   | Input or output port determined by software                                                                                                 |  |  |  |  |  |  |  |

| PA1/INT1/AD1    | INT1     | Ι     | xternal interrupt input as input mode determined                                                                                            |  |  |  |  |  |  |  |

|                 | AD1      | Ι     | ADC input channel configured by software                                                                                                    |  |  |  |  |  |  |  |

| <b>PA2</b> /AD2 | PA2      | I/O   | Input or output port determined by software                                                                                                 |  |  |  |  |  |  |  |

| PAZ/ADZ         | AD2      | Ι     | ADC input channel configured by software                                                                                                    |  |  |  |  |  |  |  |

| <b>PA3</b> /AD3 | PA3      | I/O   | Input or output port determined by software                                                                                                 |  |  |  |  |  |  |  |

| PA3/ADS         | AD3      | Ι     | ADC input channel configured by software                                                                                                    |  |  |  |  |  |  |  |

| <b>PB0</b> /AD4 | PB0      | I/O   | Input with or without pull-high resistor or output port determined by software                                                              |  |  |  |  |  |  |  |

| -               | AD4      | Ι     | ADC input channel configured by software                                                                                                    |  |  |  |  |  |  |  |

| PB1             | PB1      | I/O   | Input with or without pull-high resistor or output port determined by software                                                              |  |  |  |  |  |  |  |

| PB2/OSCI        | PB2      | I/O   | Input with or without pull-high resistor or output port determined by software                                                              |  |  |  |  |  |  |  |

| ,               | OSCI     | Ι     | external oscillator PAD Connect resister to VSS                                                                                             |  |  |  |  |  |  |  |

| PB3/BZ          | PB3      | I/O   | Input with or without pull-high resistor or output port determined by software                                                              |  |  |  |  |  |  |  |

|                 | ΒZ       | 0     | Buzzer output                                                                                                                               |  |  |  |  |  |  |  |

| PCO/INT2/VPP    | PC0      | Ι     | Input port with or without pull-high resistor determined by software<br>One of the TCPC clock sources as input mode determined              |  |  |  |  |  |  |  |

|                 | INT2     | Ι     | External interrupt input as input mode determined                                                                                           |  |  |  |  |  |  |  |

|                 | VPP      | Р     | OTP ROM Programming pin: 12.5V                                                                                                              |  |  |  |  |  |  |  |

| PC1/INT3        | PC1      | I/O   | Input with or without pull-high resistor or output port determined by software<br>One of the TCPC clock sources as input mode determined    |  |  |  |  |  |  |  |

|                 | INT3     | Ι     | External interrupt input as input mode determined                                                                                           |  |  |  |  |  |  |  |

| PC2             | PC2      | I/O   | Input with or without pull-high resistor or output port<br>determined by software<br>One of the TCPB clock sources as input mode determined |  |  |  |  |  |  |  |

| PC3             | PC3      | I/O   | Input with or without pull-high resistor or output port determined by software                                                              |  |  |  |  |  |  |  |

| VDD             | VDD      | Power | Positive power supply                                                                                                                       |  |  |  |  |  |  |  |

| VSS             | VSS      | Power | Negative power supply, ground                                                                                                               |  |  |  |  |  |  |  |

### TTR011 (1K ROM MCU)

Page

### Preliminary

## § Absolute Maximum Ratings

| ITEM                                   | SYMBOL | RATING               |  |  |

|----------------------------------------|--------|----------------------|--|--|

| Operating Temperature                  | Тор    | -20°C ~ +70°C        |  |  |

| Storage Temperature                    | Tst    | -50℃ ~ +125℃         |  |  |

| Supply Voltage                         | VDD    | VSS-0.3V ~ VSS+6.0V  |  |  |

| OTP Supply Voltage                     | VPP    | VSS-0.3V ~ VSS+12.5V |  |  |

| Input Voltage                          | Vin    | VSS-0.3V ~ VDD+0.3V  |  |  |

| ESD(Human Body Mode)                   | ESD    | >5kV                 |  |  |

| Note: VSS symbolizes for system ground |        |                      |  |  |

## § DC Characteristics

| Parameter                          | Symbol          | Test Condition                                                                      | Min.   | Тур.    | Max.     | Unit     |

|------------------------------------|-----------------|-------------------------------------------------------------------------------------|--------|---------|----------|----------|

| Operating Voltage                  | VDD             | OSCH generated by external RC oscillator                                            | 2.0    |         | 5.5      | V        |

| Operating voltage                  | VDD             | OSCH generated by on-chip<br>910kHZ oscillator                                      | 2.0    |         | 5.5      | V        |

| Operating Current                  | $I_{nd1}$       | Normal mode, no load,<br>VDD=3.0V, OSCH=3.64MHz                                     |        | 1.0     | 2.0      | mA       |

| Operating Current                  | $I_{nd3}$       | Normal mode, no load,<br>VDD=3.0V, OSCH=910kHz                                      |        | 0.4     | 0.7      | ША       |

|                                    | Istb1           | ADC OFF, OSCH stop, OSCL active, VDD=3.0V, no load                                  |        | 0.8     | 1.2      | uA       |

| GREEN mode Current                 | Istb2           | ADC measurement cycle<br>time=32ms,<br>OSCH stop, OSCL active,<br>VDD=3.0V, no load |        | 1.1     | 1.5      | uA       |

| Input low voltage                  | V <sub>IL</sub> | Input Low Voltage                                                                   | 0      |         | 0.2      | VDD      |

| Input high voltage                 | $V_{IH}$        | Input High Voltage                                                                  | 0.8    |         | 1.0      | VDD      |

| Sink Current of output             | I <sub>OL</sub> | VDD=3.0V, V <sub>OL</sub> =0.6V                                                     | 2      | 4       |          | mA       |

| Source Current of output           | I <sub>OH</sub> | VDD=3.0V, V <sub>OH</sub> =2.4V                                                     |        | -4      | -2       | mA       |

| Pull-high Resistor of PB<br>and PC | R <sub>PH</sub> | VDD=3.0V                                                                            | 50     | 100     | 150      | KΩ       |

|                                    |                 |                                                                                     | (ambie | ent tem | perature | is 25°C) |

## § AC Characteristics

| Parameter                             | Test Condition                                                    | Min. | Тур. | Max. | Unit |  |

|---------------------------------------|-------------------------------------------------------------------|------|------|------|------|--|

| High-speed clock OSCH                 | External RC oscillator                                            | 400K |      | 4M   | Hz   |  |

| Frequency                             | On-chip 910kHz oscillator                                         | 882k | 910K | 937k | п    |  |

| System stable time after<br>power up  | Stable time=(OSCL startup<br>time)+(1/OSCL)X256                   |      | 17   |      | ms   |  |

| Wake up time                          | Wake up time to low power mode<br>=(OSCL startup time)+(1/OSCL)X4 |      | 1    |      | ms   |  |

| Wake up time                          | Wake up time to normal mode<br>=(OSCH startup time)+(1/OSCH)X4    |      | 1    |      | ms   |  |

| (VDD=3V, ambient temperature is 25°C) |                                                                   |      |      |      |      |  |

## TTR011 (1K ROM MCU)

Version 3.2

Page

### Preliminary

## § Memory Map

| ROM<br>ADDRESS                     | RAM<br>ADDRESS                     | Function              |

|------------------------------------|------------------------------------|-----------------------|

| 000 <sub>H</sub>                   |                                    | Reset vector          |

|                                    |                                    | Jump to start address |

| 001 <sub>H</sub>                   |                                    | Interrupt vector      |

| 002 <sub>H</sub> ~3FF <sub>H</sub> |                                    | Program ROM           |

|                                    | $000_{H\sim}007_{H}$               | File registers        |

|                                    | $008_{H} \sim 01F_{H}$             | Peripheral registers  |

|                                    | 020 <sub>н</sub> ~057 <sub>н</sub> | Working RAM [56x4]    |

|                                    | 058 <sub>H</sub> ~068 <sub>H</sub> | Peripheral registers  |

## § File registers and Peripheral registers:

This table gives a list of the file registers and peripheral registers. "**Default**" indicates each register status upon power on reset. "**R/W**" indicates the register can be read and written. "**R/WO**" indicates the register can be read and only written to "O". "**R**" is read-only. "**W**" is write-only.

| Address          | Resister | Bit3           | Bit2            | Bit1              | Bit0            | R/W  | Default | Description                                   |  |

|------------------|----------|----------------|-----------------|-------------------|-----------------|------|---------|-----------------------------------------------|--|

| 000 <sub>H</sub> | (DP1)    | -              | -               | -                 | -               | R/W  | uuuu    | Indirect addressing register                  |  |

| 001 <sub>H</sub> | ACC      | ACC3           | ACC2            | ACC1              | ACC0            | R/W  | uuuu    | Accumulator & Read Table 1 <sup>st</sup> data |  |

| 002 н            | TB1      | D7             | D6              | D5                | D4              | R/W  | uuuu    | Read Table 2 <sup>nd</sup> data               |  |

| 003 <sub>Н</sub> | TB2      | D11            | D10             | D9                | D8              | R/W  | uuuu    | Read Table 3 <sup>rd</sup> data               |  |

| 004 <sub>Н</sub> | TB3      | D15            | D14             | D13               | D12             | R/W  | uuuu    | Read Table 4 <sup>th</sup> data               |  |

| 005 <sub>н</sub> | DPL      | A3             | A2              | A1                | A0              | R/W  | 0000    | Data Pointer low nibble                       |  |

| 006 <sub>н</sub> | DPM      | A7             | A6              | A5                | A4              | R/W  | 0000    | Data Pointer middle nibble                    |  |

| 007 <sub>н</sub> | DPH      | A11            | A10             | A9                | A8              | R/W  | 0000    | Data Pointer high nibble                      |  |

| 008 <sub>н</sub> | PS       | LVR_EN         | H/L             | GREEN             | STOP            | R/W  | 0000    | Power saving control register                 |  |

| 009 <sub>н</sub> | INTC1    | ADC_IE         | TCPC_IE         | TCPB_IE           | TB1_IE          | R/W  | 0000    | Internal interrupt enable register            |  |

| 00A <sub>H</sub> | INTF1    | ADC_IF         | TCPC_IF         | TCPB_IF           | TB1_IF          | R/W0 | 0000    | Internal interrupt request flag register      |  |

| 00B <sub>H</sub> | CTLA     | LVD_DET<br>(R) | LVD_EN<br>(R/W) | TCPCD_LD<br>(R/W) | TCP_RD<br>(R/W) |      | 0000    | LVD and timer/counter Control register        |  |

| 00C <sub>H</sub> | TBC/BZC  | BZ_EN          | -               | TB1               | TB0             | R/W  | 0-11    | Time Base Timer/buzzer control register       |  |

| 00D <sub>H</sub> | PAC      | PAC3           | PAC2            | PAC1              | PAC0            | R/W  | 1111    | Port A control register                       |  |

| 00E <sub>H</sub> | -        | -              | -               | -                 | -               | -    | -       | Reserved                                      |  |

| 00F <sub>H</sub> | PA       | PA3            | PA2             | PA1               | PA0             | R/W  | uuuu    | Port A data register                          |  |

| 010 н            | PB       | PB3            | PB2             | PB1               | PB0             | R/W  | uuuu    | Port B data register                          |  |

| 011 н            | PC       | PC3<br>(R/W)   | PC2<br>(R/W)    | PC1<br>(R/W)      | PC0<br>(R)      |      | uuuu    | Port C data register                          |  |

| 012 н            | WK_FG    | TB_WK          | PC_WK           | PB_WK             | AD/PA_WK        | R/W0 | 0000    | Wake up flag register                         |  |

| 013 н            | TCPBC    | TCPB_LD        | TCPB_CK1        | TCPB_CK0          | TCPB_EN         | R/W  | 0000    | Timer/counter B(TCPB) control register        |  |

| 014 <sub>H</sub> | TCPBDLL  | TCPBDL3        | TCPBDL2         | TCPBDL1           | TCPBDL0         | R/W  | 0000    | Low nibble register for low data TCPBDL       |  |

| 015 <sub>н</sub> | TCPBDLH  | TCPBDL7        | TCPBDL6         | TCPBDL5           | TCPBDL4         | R/W  | 0000    | High nibble register for low data TCPBDL      |  |

| 016 <sub>н</sub> | TCPBDHL  | TCPBDH3        | TCPBDH2         | TCPBDH1           | TCPBDH0         | R/W  | 0000    | Low nibble register for high data TCPBDH      |  |

| 017 <sub>Н</sub> | TCPBDHH  | TCPBDH7        | TCPBDH6         | TCPBDH5           | TCPBDH4         | R/W  | 0000    | High nibble register for high data TCPBDH     |  |

| 018 <sub>H</sub> | INTC2    | INT3_IE        | INT2_IE         | INT1_IE           | INT0_IE         | R/W  | 0000    | External interrupt enable register            |  |

| 019 <sub>Н</sub> | INTF2    | INT3_IF        | INT2_IF         | INT1_IF           | INT0_IF         | R/W0 | 0000    | External interrupt request flag register      |  |

| 01A <sub>H</sub> | ADC_CTL1 | ADC_EN         | AD_CH2          | AD_CH1            | AD_CH0          | R/W  | 0000    | ADC control register 1                        |  |

| 01B <sub>H</sub> | TCPCC    | TCPC_CK2       | TCPC_CK1        | TCPC_CK0          | TCPC_EN         | R/W  | 0000    | Timer/counter C(TCPC) control register        |  |

| 01C <sub>H</sub> | TCPCDL   | TCPCD3         | TCPCD2          | TCPCD1            | TCPCD0          | R/W  | 0000    | Low nibble register for data TCPCD            |  |

| Title               |            |               |               |               |             |     |             |                                              | Page                  |  |  |

|---------------------|------------|---------------|---------------|---------------|-------------|-----|-------------|----------------------------------------------|-----------------------|--|--|

| TTR011 (1K ROM MCU) |            |               |               |               |             |     | Version 3.2 | 7 of 41                                      |                       |  |  |

| Preliminary         |            |               |               |               |             |     |             |                                              |                       |  |  |

| Address             |            |               |               |               |             |     |             |                                              |                       |  |  |

| 01D <sub>H</sub>    | TCPCDH     | TCPCD7        | TCPCD6        | TCPCD5        | TCPCD4      | R/W | 0000        | High nibble register fo                      | or data TCPCD         |  |  |

| 01E <sub>H</sub>    | PBC        | PBC3          | PBC2          | PBC1          | PBC0        | R/W | 1111        | Port B control register                      |                       |  |  |

| 01F <sub>H</sub>    | PCC        | PCC3<br>(R/W) | PCC2<br>(R/W) | PCC1<br>(R/W) | PCC0<br>(R) |     | 1111        | Port C control register                      |                       |  |  |

| 058 <sub>н</sub>    | AD0_H      | AD0_H3        | AD0_H2        | AD0_H1        | AD0_H0      | R/W | uuuu        | High limit voltage for ADC0 wake up functio  |                       |  |  |

| 059 <sub>н</sub>    | AD0_L      | AD0_L3        | AD0_L2        | AD0_L1        | AD0_L0      | R/W | uuuu        | Low limit voltage for ADC0 wake up function  |                       |  |  |

| 05А <sub>Н</sub>    | AD1_H      | AD1_H3        | AD1_H2        | AD1_H1        | AD1_H0      | R/W | uuuu        | High limit voltage for ADC1 wake up function |                       |  |  |

| 05В <sub>Н</sub>    | AD1_L      | AD1_L3        | AD1_L2        | AD1_L1        | AD1_L0      | R/W | uuuu        | Low limit voltage for ADC1 wake up function  |                       |  |  |

| 05C <sub>н</sub>    | AD2_H      | AD2_H3        | AD2_H2        | AD2_H1        | AD2_H0      | R/W | uuuu        | High limit voltage for                       | ADC2 wake up function |  |  |

| 05D <sub>н</sub>    | AD2_L      | AD2_L3        | AD2_L2        | AD2_L1        | AD2_L0      | R/W | uuuu        | Low limit voltage for A                      | ADC2 wake up function |  |  |

| 05E н               | AD3_H      | AD3_H3        | AD3_H2        | AD3_H1        | AD3_H0      | R/W | uuuu        | High limit voltage for                       | ADC3 wake up function |  |  |

| 05F н               | AD3_L      | AD3_L3        | AD3_L2        | AD3_L1        | AD3_L0      | R/W | uuuu        | Low limit voltage for A                      | ADC3 wake up function |  |  |

| 060 н               | ADC_D      | ADC_D3        | ADC_D2        | ADC_D1        | ADC_D0      | R   | uuuu        | ADC data register                            | •                     |  |  |

| 061 <sub>H</sub>    | ADC_PA     | AD3/PA3       | AD2/PA2       | AD1/PA1       | AD0/PA0     | R/W | 0000        | ADC input channel an                         | d PA select register  |  |  |

| 062 <sub>н</sub>    | AD_WKEN    | AD3WKEN       | AD2WKEN       | AD1WKEN       | AD0WKEN     | R/W | 0000        | ADC wake up function                         | control register      |  |  |

| 063 <sub>н</sub>    | ADC_CTL2   | ADCK1         | ADCK0         | -             | AD4/PB0     | R/W | 00-0        | ADC control register 2                       |                       |  |  |

| 064 <sub>н</sub>    | PB_PH      | PB3_PH        | PB2_PH        | PB1_PH        | PB0_PH      | R/W | 0000        | Port B pull-high regist                      | er                    |  |  |

| 065 <sub>н</sub>    | PC_PH      | PC3_PH        | PC2_PH        | PC1_PH        | PC0_PH      | R/W | 0000        | Port C pull-high register                    |                       |  |  |

| 066 <sub>н</sub>    | PT_WKEN    | -             | PC_WKEN       | PB_WKEN       | PA_WKEN     | R/W | -000        | Port wake up function                        |                       |  |  |

| 067 <sub>н</sub>    | Mod RC16KL | M16K3         | M16K2         | M16K1         | M16K0       | R/W | 0000        | Low nibble of RC16hz                         | modify register       |  |  |

## § System Clock and Operation Modes

M16K6

M16K5

There are two clocks, OSCH and OSCL, to be supplied to the CPU and peripheral hardware. OSCL is the low-speed clock. It is generated from on-chip 16kHz oscillator.

R/W

1000

High nibble of RC16hz modify register

M16K4

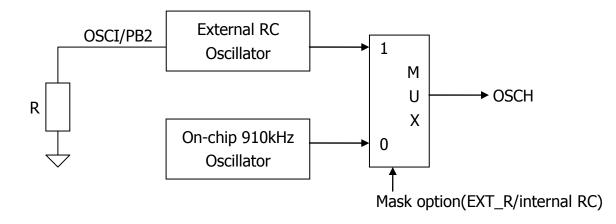

OSCH is the high-speed clock. It can be generated from on-chip 910kHz oscillator or external RC type oscillator that is defined by mask option. If external RC type oscillator is selected, there should be a resistor connected between OSCI pin and VSS.

#### Figure 2: OSCH circuit

Mod\_RC16KH

M16K7

068<sub>H</sub>

### TTR011 (1K ROM MCU)

Page

### Preliminary

$\diamond$  PS : Power saving control register [R/W] : 008<sub>H</sub> , default value [0000]

| Register   | Bit3   | Bit2 | Bit1  | Bit0 |

|------------|--------|------|-------|------|

| Bit Name   | LVR_EN | H/L  | GREEN | STOP |

| Read/write | R/W    | R/W  | R/W   | R/W  |

STOP : STOP mode enable (0: inactive; 1: active)

GREEN : GREEN mode enable (0: inactive; 1: active)

H/L : CPU clock select

=1 : select high speed clock (OSCH), CPU enters normal mode

=0 : select low speed clock (OSCL), CPU enters low power mode

LVR\_EN : (ROM-ready type) LVR enable

=0 : disable LVR

=1 : enable LVR

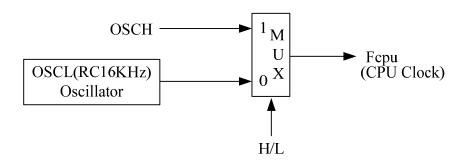

#### CPU clock (Normal mode & low power mode)

The CPU clock comes from OSCH or OSCL clocks which are controlled by H/L bit in PS register. When the MCU sets H/L bit = "1", The CPU enters normal mode and operates in the high speed clock (OSCH). In this mode, the OSCL is also active.

When the MCU sets H/L bit = "0", The CPU enters low power mode and operates in the low speed clock (OSCL). In this mode, the OSCH will be turn off. The high speed oscillators are shut down to save the power consumption. The others circuits of the MCU which use the OSCH clock are also idle to reduce the power consumption. The CPU also enters low power mode after power-up and reset.

#### Figure 3: CPU clock circuit

#### TTR011 (1K ROM MCU)

## Preliminary

### Power saving modes (STOP mode & GREEN mode)

The MCU enters STOP or GREEN mode by writing STOP bit or GREEN bit in PS register. During these modes, MCU holds some of the internal circuits to save the power consumption.

When the MCU sets STOP bit = "1", the MCU enter the STOP mode. Both of the clocks, OSCH and OSCL, are turn off. The MCU can be released from STOP mode by reset, interrupt, or wake-up event. When the system is waked up, it need a warm-up time for the stability of system clock running.

When the MCU sets GREEN bit = "1", the MCU enter the GREEN mode. In GREEN mode, the OSCH clock will be stopped, and RC16Khz oscillator (OSCL) is still on. The system can wake up from auto time-out (TB1) and ADC change (in ADC check procedure) wake-up for the alarm system application.

| Power saving modes condition & Release |                                |                       |  |  |  |  |  |

|----------------------------------------|--------------------------------|-----------------------|--|--|--|--|--|

| Modes                                  | STOP mode                      | GREEN mode            |  |  |  |  |  |

| High speed oscillator                  | Stopped                        | Stopped               |  |  |  |  |  |

| Low speed oscillator                   | Stopped                        | Keep Operating        |  |  |  |  |  |

| CPU clock                              | Stopped                        | Stopped               |  |  |  |  |  |

| <b>CPU internal status</b>             | Stop & F                       | Retain the status     |  |  |  |  |  |

| Memory, Flag,<br>Register, I/O         | Retain the status              |                       |  |  |  |  |  |

| Program counter                        | Hold the next executed address |                       |  |  |  |  |  |

| Peripherals: Time                      |                                |                       |  |  |  |  |  |

| base, Timers,                          | Stopped & Retain               | Keep Operating        |  |  |  |  |  |

| Interrupts                             |                                |                       |  |  |  |  |  |

| Watch Dog Timer                        | Disabled                       | & cleared             |  |  |  |  |  |

| Release Condition                      | Reset ,                        | Reset,                |  |  |  |  |  |

|                                        | external INT,                  | external INT,         |  |  |  |  |  |

|                                        | Input change wake-up           | internal INT,         |  |  |  |  |  |

|                                        |                                | Input change wake-up, |  |  |  |  |  |

|                                        |                                | TB1 time-out wake-up, |  |  |  |  |  |

|                                        |                                | ADC change wake-up    |  |  |  |  |  |

#### ♦ Power saving modes condition & Release

#### MCU System Operation Modes

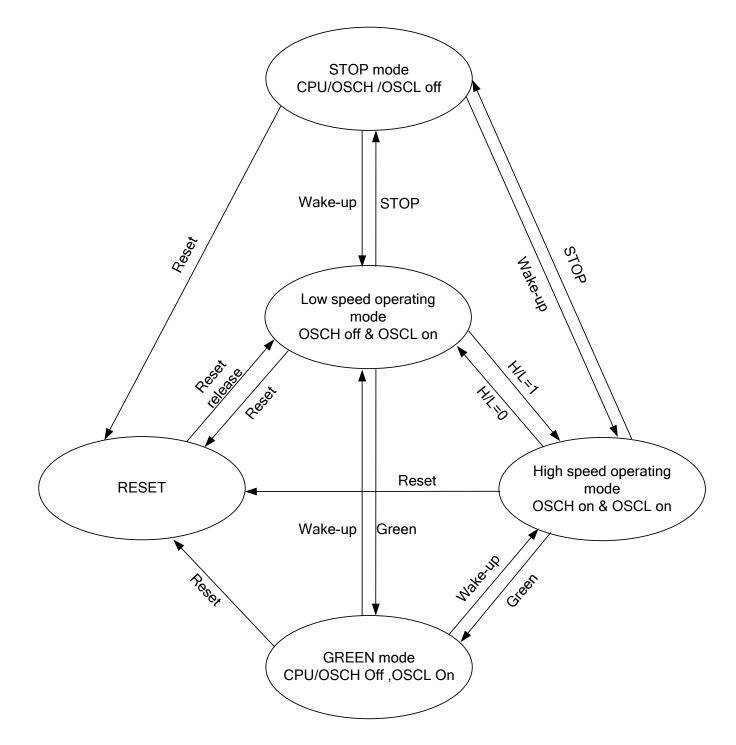

The MCU has the 4 operation modes, including normal mode, low speed mode , STOP mode , and GREEN mode . After power on reset, the MCU will go into low speed mode

Page

Version 3.2

| TTR011 (1K ROM MCU) | Version 3.2 | 10 of 41 |

|---------------------|-------------|----------|

| Title               |             | Page     |

automatically and the CPU operate in the low speed clock (OSCL). After wake up from STOP/GREEN mode, the MCU will resume the last operation mode.

/7

#### Figure 4: state diagram of system operation modes

| Title               |             | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 11 of 41 |

|                     |             |          |

#### OSCILLATOR STABLE TIME (OST)

The system oscillator generates the system control timing for CPU core or peripheral devices with fixed control phase, so the waveform of oscillator becomes sensitive to many kinds of noise. The abnormal duty is especially fatal for CPU. Any switching of clock source needs oscillation stable time (OST) to make sure the oscillation is stable and synchronized with CPU timing phase.

The OST is 256's RC16K clocks after power up. When waking up to normal mode, The OST is 4's OSCH clocks. When waking up to low power mode, the OST is 4's RC16K (OSCL) clock.

#### Adjustment of OSCL (RC16KHz)

The OSCL is RC type oscillator. The resistance and capacitance of the built-in resistor and capacitor will vary piece by piece at the wafers. Then the frequency of OSCL will vary as the resistance and capacitance vary. When the chip is used in the hot or cold environment, the frequency of OSCL will change as the temperature of environment. It will also change as the power voltage of the chip is change. There is above 100% variation of the OSCL frequency in the worst case.

This chip provides a way to correct the OSCL frequency. If on-chip 910KHz is used as OSCH, it provides a 3% accurate oscillator to MCU. The user software can compare OSCL with OSCH by the timer/counter B (TCPB) and C (TCPC). If the OSCL is slower than 16KHz, decreasing Mod\_RC16KH or Mod\_RC16KL will speed up 16KHz. If the OSCL is faster than 16KHz, increasing Mod\_RC16KH or Mod\_RC16KL speed up 16KHz. Every 1 increment will slow down about 1.5% of frequency at RC16KHz. Here is a simple method to adjust the OSCL frequency:

- Step 1: set TCPC condition TCPCD =  $FF_H$

- Step 2: set TCPB conditions TCPBDH =  $FF_H$ , TCPBDL =  $FF_H$

- Step 3: enable TCPC at conditions Input clock = RC16KHz, auto-reload

- Step 4: enable TCPB at conditions Input clock = Fcpu, auto-reload

- Step 5: count 6 overflows from TCPB, and record how many of TCPCOV occur

- Step 6: Compute the total count of RC16KHz Read TCPC counter value and do 1's complement, and add 255 for every TCPCOV

- Step 7: disable TCPB and TCPC

- Step 8: if the total count < 54, subtract 1 to M16K7~0 and go to Step 3

----

| Title               |             | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 12 of 41 |

### **Preliminary**

Step 9: if the total count > 55, add 1 from M16K7~0 and go to Step 3 Step 10: wait about 10 min. then go to Step 1 to do adjustment again

Mod\_RC16KL : Low nibble of RC16KHz modify register [R/W] : 067<sub>H</sub> , default value [0000] ∻

| Register   | Bit3  | Bit2  | Bit1  | Bit0  |

|------------|-------|-------|-------|-------|

| Bit Name   | M16K3 | M16K2 | M16K1 | M16K0 |

| Read/write | R/W   | R/W   | R/W   | R/W   |

M16K3~0 : low nibble to modify 16KHz frequency

Mod\_RC16KH : High nibble of RC16KHz modify register [R/W] : 068<sub>H</sub> , default value [1000] ∻

| Register   | Bit3  | Bit2  | Bit1  | Bit0  |

|------------|-------|-------|-------|-------|

| Bit Name   | M16K7 | M16K6 | M16K5 | M16K4 |

| Read/write | R/W   | R/W   | R/W   | R/W   |

M16K7~4 : high nibble to modify 16KHz frequency

| TTR011 (1K ROM MCU) | Version 3.2 | Page 13 of 41 |

|---------------------|-------------|---------------|

|                     |             |               |

## § Interrupts

The CPU provides only 1 interrupt vector (\$001H) for all interrupts. All of them have the same priority in the hardware. The first coming interrupt will be served firstly. When above two interrupts are coming, the software can decide the priority to serve them.

Interrupt sources include three timer/counter overflow interrupts (TB1 INT, TCPB INT, and TCPC INT), ADC conversion complete interrupt, and four external interrupts (INT0 INT from AD0/PA0/INT0 pin , INT1 INT from AD1/PA1/INT1 pin , INT2 INT from PC0/VPP/INT2 pin, and INT3 INT from PC1/INT3 pin).

The interrupt enable registers (INTCx) contain the interrupt enable control bits to enable and disable corresponding interrupt request and the corresponding interrupt request flags in the INTFx registers. Before finishing the INT service routine, another INT request will keep waiting until program return from interrupt routine.

| $\diamond$ | $INTC1$ : Internal interrupt enable register [R/W] : $009_H$ , default value [0000] |  |

|------------|-------------------------------------------------------------------------------------|--|

|------------|-------------------------------------------------------------------------------------|--|

| Register   | Bit3    | Bit2    | Bit1    | Bit0   |

|------------|---------|---------|---------|--------|

| Bit Name   | ADC _IE | TCPC_IE | TCPB_IE | TB1_IE |

| Read/Write | R/W     | R/W     | R/W     | R/W    |

TB1\_IE: Enable interrupt of time base timer 1. (0: disable; 1: enable) TCPB\_IE: Enable interrupt of timer/counter B. (0: disable; 1: enable) TCPC\_IE: Enable interrupt of timer/counter C. (0: disable; 1: enable) ADC\_IE : Enable interrupt of the ADC conversion. (0: disable; 1: enable)

♦ INTC2 : External interrupt enable register [R/W] : 018<sub>H</sub> , default value [0000]

| Register   | Bit3    | Bit2    | Bit1    | Bit0    |

|------------|---------|---------|---------|---------|

| Bit Name   | INT3_IE | INT2_IE | INT1_IE | INT0_IE |

| Read/Write | R/W     | R/W     | R/W     | R/W     |

INT0\_IE: Enable the external AD0/PA0/INT0 interrupt (0: disable; 1: enable) INT1\_IE: Enable the external AD1/PA1/INT1 interrupt (0: disable; 1: enable) INT2\_IE: Enable the external PC0/VPP/INT2 interrupt (0: disable; 1: enable) INT3\_IE: Enable the external PC1/INT3 interrupt (0: disable; 1: enable)

♦ INTF1 : Internal interrupt request flag register [R/W0] : 00A<sub>H</sub> , default value [0000]

| Register | Bit3   | Bit2    | Bit1    | Bit0   |

|----------|--------|---------|---------|--------|

| Bit Name | ADC_IF | TCPC_IF | TCPB_IF | TB1_IF |

| Title | Π          | R011 (1 | Version 3.2 | Page 14 of 41 |      |  |

|-------|------------|---------|-------------|---------------|------|--|

|       |            |         | Pre         | liminary      |      |  |

|       | Read/Write | R/W0    | R/W0        | R/W0          | R/W0 |  |

TB1\_IF: TIME base Timer1 interrupt request flag for overflow. (0: inactive; 1: active) TCPB\_IF: Timer/counter B interrupt request flag for overflow. (0: inactive; 1: active) TCPC\_IF: Timer/counter C interrupt request flag for overflow. (0: inactive; 1: active) ADC\_IF: ADC interrupt request flag for conversion complete. (0: inactive; 1: active)

♦ INTF2 : External interrupt request flag register [R/W0] : 019<sub>H</sub> , default value [0000]

| RegisterBit3Bit2Bit1Bit0Bit NameINT3_IFINT2_IFINT1_IFINT0_IFRead/WriteR/W0R/W0R/W0R/W0INT0_IF:INT0 interrupt request flag for change. (0: inactive; 1: activeINT1_IF:INT1 interrupt request flag for change. (0: inactive; 1: activeINT2_IF:INT2 interrupt request flag for change. (0: inactive; 1: activeINT3_IF:INT3 interrupt request flag for change. (0: inactive; 1: active |          |                                                                     |       |                  |                | - · ·                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------|-------|------------------|----------------|----------------------|

| Read/WriteR/W0R/W0R/W0INT0_IF:INT0 interrupt request flag for change. (0: inactive; 1: activeINT1_IF:INT1 interrupt request flag for change. (0: inactive; 1: activeINT2_IF:INT2 interrupt request flag for change. (0: inactive; 1: active                                                                                                                                        | Register | · Bit                                                               | 3     | Bit2             | Bit1           | Bit0                 |

| INTO_IF: INTO interrupt request flag for change. (0: inactive; 1: active<br>INT1_IF: INT1 interrupt request flag for change. (0: inactive; 1: active<br>INT2_IF: INT2 interrupt request flag for change. (0: inactive; 1: active                                                                                                                                                   | Bit Name | e INT3                                                              | _IF   | INT2_IF          | INT1_IF        | INT0_IF              |

| INT1_IF: INT1 interrupt request flag for change. (0: inactive; 1: active<br>INT2_IF: INT2 interrupt request flag for change. (0: inactive; 1: active                                                                                                                                                                                                                               | Read/Wri | te R/V                                                              | V0    | R/W0             | R/W0           | R/W0                 |

| INT2_IF: INT2 interrupt request flag for change. (0: inactive; 1: active                                                                                                                                                                                                                                                                                                           | INT0_IF: | INT0 int                                                            | errup | t request flag f | or change. (0: | inactive; 1: active) |

|                                                                                                                                                                                                                                                                                                                                                                                    | INT1_IF: | E: INT1 interrupt request flag for change. (0: inactive; 1: active) |       |                  |                |                      |

| INT3_IF: INT3 interrupt request flag for change. (0: inactive; 1: active                                                                                                                                                                                                                                                                                                           | INT2_IF: | INT2 int                                                            | errup | t request flag f | or change. (0: | inactive; 1: active) |

|                                                                                                                                                                                                                                                                                                                                                                                    | INT3_IF: |                                                                     |       |                  |                |                      |

If the interrupt request needs service, the user software may set the corresponding interrupt enable bit. The internal timer/counter interrupt flag (TCPx\_IF) is set to 1, resulting from the timer/counter overflow.

When the corresponding interrupts are enabled and their flag bits are set to 1, the CPU will active the interrupt service routine. Then CPU reads the service flag bits and check the request priority then proceeds with the relative interrupt service. After CPU writes the corresponding bits to 0 in the INTF register, the INT flag bit will be cleared to 0 (using STX #n, \$m instruction). The CPU can only write "0" to clear the flag bit. Writing "1" to flag bit will do nothing to it.

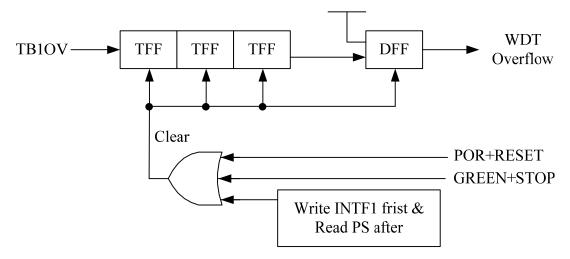

## § Watch Dog Timer (WDT)

The clock of watch dog timer comes from time base overflow (TB1OV). The time-up signal of WDT can prevent a software malfunction or abnormal sequence from jumping to an unknown memory location, before the system is going to fatal failure. Normally, when the time-up signal of WDT is active, it will reset the chip. At the same time, program and hardware can be initialized to resume system back to normal operation. The chip needs 2 steps to clear WDT. The programmer writes INTF1 with \$F data first to enable the WDT clear, and then reads the power saving (PS) control register after. After finishing the two write/read steps in order, the watch dog timer will be cleared. User should well arrange the two command steps for avoiding the dead lock loop. *User should keep in minds that always reset WDT at main program and*

| Title               |             | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 15 of 41 |

never clear the WDT in the interrupt routine.

#### The max period of WDT = (TB10V cycle time) \* 8

In GREEN mode, The time base timer 1 is combined with timer/counter TCPB to generate a long period timer for auto wake-up function. The WDT is cleared in this mode. The TB1OV is also ignored by the WDT. In STOP mode, all the oscillators are turned off. The WDT is also cleared.

#### Figure 5: WDT circuit

| Title               |             | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 16 of 41 |

## § RESET

The chip has three kinds of reset sources: POR (power on reset), Watch dog timer reset, LVR (low voltage reset). The reset feature can be divided into 2 kinds of groups. One is system reset and the other is CPU reset. The system reset will initialize the CPU and peripheral device with default state. The CPU reset only initializes the CPU state and keeps the peripheral state no change.

#### System reset

#### .POR (power on reset)

The chip provides automatic reset function when the power is turned on. The reset will be active by POR when the VDD is below 1.4V and its rising slope (from 0.1VDD up to 0.9VDD) is less than 10ms.

#### CPU reset

#### .Watch Dog Timer Reset

The reset will happen automatically when the watchdog timer runs overflow. If the watchdog timer is cleared regularly by the user software before overflow, no watchdog reset will occur. While the CPU is forced into abnormal state, the regular software procedure is disrupted and the watchdog timer may overflow by no clear coming. The overflow of WDT will generate reset to return CPU to the reset procedure. Thus the CPU goes back to normal operation. The H/L and GREEN and STOP bits will also be cleared by WDT.

#### . LVR (low voltage reset)

The LVR is a low system voltage detector. As the operating voltage falls below the detected window, then the LVR will make the CPU start the reset procedure. The LVR can be disabled by setting the LVREN bit of PS register to "0". When the low system voltage occurs in this condition, The CPU will cease to do any instruction. But the system states have opportunity to be corrupted by this low system voltage. The following table shows the relationship between LVR and detected voltage. The H/L and GREEN and STOP bits will also be cleared by LVR.

| LVR | System RESET | Detected Vop |

|-----|--------------|--------------|

| 0→1 | active       | 1.2V~1.8V    |

| Title | TTR011 (1K | ROM MCU)  | Version 3.2 | Page 17 of 41 |  |

|-------|------------|-----------|-------------|---------------|--|

|       |            | Prelimina | ſy          |               |  |

|       | 1→0        | inactive  |             | >1.8V         |  |

For OTP MCU, hardware needs to download the mask options into registers. It happens at power on reset, watch dog overflow reset and LVR reset.

### § System Register Description

\$000(DP1) : Index == 虛擬指標暫存器

這不是一個實際的暫存器,只用來當做間接定址的指標,當對此位址讀寫或運算或 讀取ROM TABLE 時,CPU 實際是以DPH,DPM,DPL 所組成的 12 位元為地址線,讀取ROM 的資料或是對RAM 做運算或讀寫資料.

\$001: Acc == 累積器

除了當成一般暫存器使用外;當需要將暫存器或RAM 的資料轉換到其他RAM 或暫存 器時累積器是一個重要的中繼站,先使用LDA 指令讀取暫存器或RAM 的資料暫存在 累積器,再用STX 指令存到想要存放的暫存器或RAM 中,來達成暫存器或RAM 的資 料轉換;此外在做邏輯或算數運算時,若是選擇結果放到ACC,則運算完的結果將會 存到累積器中;在使用直接指令模式運算,累積器是二個運算來源之一;若是使用 RTB 指令讀取ROM TABLE 時,讀取到的資料是 16 位元,其中最低的 4 位元(D3~D0) 也會暫存在累積器中

\$002:TB1 == 讀表暫存器1

此暫存器提供我們在使用RTB 指令讀取ROM TABLE 時,暫時存放讀取 16 位元資料 中的次低 4 位元(D7~D4)用;在不使用讀表功能時,此暫存器可當作一般暫存器使用.

\$003:TB2 == 讀表暫存器 2

與TB1 同樣功能,此暫存器提供我們在使用RTB 指令讀取ROM TABLE 時,暫時存放 讀取16 位元資料中的次高4 位元(D11~D8)用;在不使用讀表功能時,此暫存器可當 作一般暫存器使用.

#### \$004:TB3 == 讀表暫存器3

同樣的此暫存器提供我們在使用RTB 指令讀取ROM TABLE 時,暫時存放讀取 16 位 元資料中的最高 4 位元(D15~D12)用;在不使用讀表功能時,此暫存器可當作一般 暫存器使用.

| Title               | Marian 2.2  | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 18 of 41 |

|                     |             |          |

\$005:DPL == 低位指標暫存器,

使用間接方式對RAM 位址讀寫或運算時,此暫存器是指標(DP)的 10 條地址線中最低的4 位元(A3~A0);同時亦是使用RTB 指令讀取ROM TABLE 資料的12 位元地址線中最低的4 位元(A3~A0),所以運用在上述二種方式使用之前必須先設定此暫存器. 若是與上述的使用不衝突時可當作一般暫存器使用.

#### \$006:DPM == 中位指標暫存器,

與DPL 功能相同,在使用間接方式對RAM 位址讀寫或運算時,此暫存器是指標(DP) 的10 條地址線之中間的4 位元(A7~A4);同時亦是使用RTB 指令讀取ROM TABLE 資 料的12 位元地址線之中間的4 位元(A7~A4),所以運用在上述二種方式使用之前必 須先設定此暫存器.若是與上述的使用不衝突時可當作一般暫存器使用.

\$007:DPH == 高位指標暫存器,

與上述二暫存器功能相同,在使用間接方式對RAM 位址讀寫或運算時,此暫存器是 指標(DP)的 10 條地址線中最高的 2 位元(A9~A8),A10 及A11 會被忽略掉一般設定 為"0";同時亦是使用RTB 指令讀取ROM TABLE 資料的 12 位元地址線中最高的 4 位元(A11~A8),所以運用在上述二種方式使用之前必須先設定此暫存器.若是與上 述的使用不衝突時可當作一般暫存器使用.

| Title               |             | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 19 of 41 |

|                     |             |          |

## § Wake up

After the CPU wakes up from STOP or GREEN mode, it can know which source makes wake-up occur from the wake-up flag. Then the user software may choose the proper routine for the dedicated wake-up source.

There are 3 sources which make the CPU wake-up from STOP mode. They include : power on reset, external INT, and input change. Except power on reset which initializes the whole system, the others make the CPU execute the instruction after the last one which is executed before STOP mode occurs.

There are 6 sources which make the CPU wake-up from GREEN mode. They are : power on reset, external INT, internal INT, input change, auto time-out (TB1), and ADC change (in ADC check procedure). Except power on reset which initializes the whole system, the others make the CPU execute the instruction after the last one which is executed before GREEN mode occurs.

Note: The instruction that follow the STOP or GREEN mode (set by PS register) must be NOP, and two NOP instructions must be followed, it make sure to wake up success.

#### Port wake up enable

The Port Wake-up enable register can enable or disable the wake-up from the input change of the ports. There are 3 port wake-up enable bits for 3 ports each. All pins in the same port are controlled by the same wake up enable bit.

| Ŷ |            |      |         |         |         |  |  |

|---|------------|------|---------|---------|---------|--|--|

|   | Register   | Bit3 | Bit2    | Bit1    | Bit0    |  |  |

|   | Bit Name   |      | PC_WKEN | PB_WKEN | PA_WKEN |  |  |

|   | Read/Write | R0   | R/W     | R/W     | R/W     |  |  |

$\diamond$  PT\_WKEN : Port wake up enable register [R/W] : 066<sub>H</sub>, default value [-000]

PA\_WKEN : control PORT A (pa0~3) input change wake up when those are input pins.

=0 : disable wake-up

=1 : enable wake-up

PB\_WKEN : control PORT B (pb0~3) input change wake up when those are input pins.

=0 : disable wake-up

=1 : enable wake-up

PC\_WKEN : control PORT C (pc0~3) input change wake up when those are input pins.

=0 : disable wake-up

=1 : enable wake-up

| Title               |             | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 20 of 41 |

|                     |             |          |

#### Wake up flag

The Wake-up flag register records which wake-up sources take place. When waked up, the user software should read this register to choose the corresponding service routine for each flag bit. The corresponding wake-up flag bit must be cleared before entering STOP or GREEN mode. After CPU writes the corresponding bit to "0" in the register, the wake-up flag bit will be cleared to 0 (using STX #n, \$m instruction). The user software can only write "0" to clear the wake-up flag bit. Writing "1" to the flag bit will do nothing to it.

♦ WK\_FG : wake-up flag register [R/W0] : 012<sub>H</sub> , default value [0000]

| —          | 1 3 3 |       | ,     |          |

|------------|-------|-------|-------|----------|

| Register   | Bit3  | Bit2  | Bit1  | Bit0     |

| Bit Name   | TB_WK | PC_WK | PB_WK | AD/PA_WK |

| Read/Write | R/W0  | R/W0  | R/W0  | R/W0     |

AD/PA\_WK: The wake-up flag for ADC max/min range check fail in GREEN mode, and input change of any input pins of PA (Pa0~3) (0: inactive; 1: active)

- PB\_WK: The wake-up flag for input change of any input pins of PB (Pb0~3) (0: inactive; 1: active)

- PC\_WK: The wake-up flag for input change of any input pins of PC (Pc0~3) (0: inactive; 1: active)

- TB\_WK: The wake-up flag for overflow of time base timer 1 in GREEN mode (0: inactive; 1: active)

### TTR011 (1K ROM MCU)

Page

### Preliminary

## § Peripheral function description:

### Control register

Title

The control register includes timer/counter control bits and low voltage detect/control bits. The user software can turn on LVD and find out whether the power is below the low voltage or not in this register. There are four voltages selected in the mask option register. Because the LVD consume some operation current, so it will be automatically turned off when entering into STOP or GREEN mode. It takes 500us to be stable after enabling the LVD\_EN bit. Do not read the LVD\_DET bit before the stable of the LVD circuit.

$\diamond$  CTLA : LVD and time/counter control register [R/W] : 00B<sub>H</sub> , default value [0000]

|            | 1       | 5      | <u> </u> | 11 /   |

|------------|---------|--------|----------|--------|

| Register   | Bit3    | Bit2   | Bit1     | Bit0   |

| Bit Name   | LVD_DET | LVD_EN | TCPC_LD  | TCP_RD |

| Read/Write | R       | R/W    | R/W      | R/W    |

TCP\_RD : control reading from counter data register or pre-load data register of the timer/counter B & C.

=0 : read from counter data register

- =1 : read from pre-load data register

- TCPC\_LD : enable auto-reload function of timer/counter C

- =0 : disable auto-reload function

- =1 : enable auto-reload function

- LVD\_EN : enable low voltage detect function

- =0 : disable low voltage detect function

- =1 : enable low voltage detect function

- LVD\_DET : show whether the power below low voltage or not

- =0 : the power not in low voltage state

- =1 : detect a low voltage happen

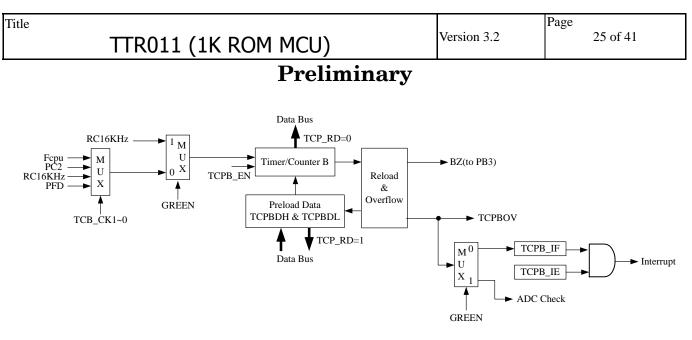

#### Time Base Timer 1 and Buzzer control

The register includes the four selections of the overflow time in time base timer 1, and buzzer output enable.

The clock of time base timer 1 is from OSCL (16KHz) normally. But in GREEN mode, it gets the clock from the overflow of time/counter B, and its overflow wakes up CPU. But the

| Title               |             | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 22 of 41 |

overflow will not generate a interrupt request, even when the TB1\_IE bit is set in the INTC1 register. Also the interrupt flag bit, ADC\_IF, is leave no change in GREEN mode. The combination of timer/counter B and time base timer1 let the MCU stay a long period time in the GREEN mode.

$\diamond$  TBC/BZC : Time base timer/buzzer control register [R/W] : 00C<sub>H</sub> , default value [0-11]

| Register   | Bit3  | Bit2 | Bit1 | Bit0 |

|------------|-------|------|------|------|

| Bit Name   | BZ_EN |      | TB1  | TB0  |

| Read/Write | RW    | R0   | R/W  | R/W  |

TB1, TB0 : select overflow count of time base timer 1 in GEEN mode, or overflow time of time base timer 1 as the following table:

| TB1 | TB0 | GREEN mode     | Ot            | her modes            |

|-----|-----|----------------|---------------|----------------------|

| IDI | IDU | Overflow count | Overflow time | Overflow frequency   |

| 0   | 0   | 256            | 15.625 ms     | 16kHz / 256 = 64 Hz  |

| 0   | 1   | 512            | 31.25 ms      | 16kHz / 512 = 32 Hz  |

| 1   | 0   | 1024           | 62.5 ms       | 16kHz / 1024 = 16 Hz |

| 1   | 1   | 2048           | 125 ms        | 16kHz / 2048 = 8 Hz  |

BZ\_EN : enable the output pin of buzzer

=0 : PB3/BZ defined as PB3

=1 : PB3/BZ defined as BZ output pin

#### Figure 6: Time base timer 1 circuit

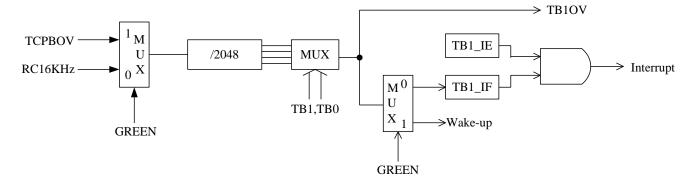

#### 8 bits Timer/counter B for TCPB

The 8-bit timer/counter B with two pre-load data buffers provides four clock sources to be selected. The clock sources includes: Fcpu (CPU clock), PC2, OSCL (16Khz), and PFD clock from TCPC. When the TCPB\_EN bit is "0", the pre-load data buffers, TCPBDHH and TCPBDHL, will keep being loaded into counter. Any value written to TCPBDHH and TCPBDHL is also

| Title               |             | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 23 of 41 |

loaded to counter. After writing the TCPB\_EN to "1", it depends on auto-load function to control how to reload to counter.

The overflow signal of TCPB is TCPBOV. The rising edge of TCPBOV will set the relative INT flag. If disabling auto-reload function by writing TCPB\_LD to "0", the TCPBOV will be active after TCPB counts up from the 1's complement of TCPBDH to "FF<sub>H</sub>". If enabling auto-reload function, the TCPBOV will be active until TCPB counts up both the values reloaded in order from the TCPBDH and TCPBDL.

In the condition that TCPBDH is written  $00_{H}$ , Enabling TCPB will make a immediate counter overflow. It will trigger reload TCPBHL in the auto-reload mode. Or it will activate TCPBOV and count across to  $00_{H}$  when the auto-reload function is disabled.

After the BZ\_EN bit is set to 1 in the TBC/BZC register, TCPB provides buzzer function by directing the TCPBOV signal waveform to the PB3 pin. No matter what the TCPB\_LD bit is, the auto-reload function will be active.

When setting the TCP\_RD bit to 0 in the CTLA register, Reading TCPBDH or TCPBDL get the same value from the counter of TCPB. Because the counter is loaded the 1's complement of TCPBDH or TCPBDL and counts up, the value read from the counter needs to be translated. If writing TCP\_RD bit to 1, Reading TCPBDH (or TCPBDL) get the value from the pre-load data buffer of TCPBDH (or TCPBDL).

| <u> </u>   |         | - J L /  | <b>_</b> = = 11 <b>/</b> = = | L       |

|------------|---------|----------|------------------------------|---------|

| Register   | Bit3    | Bit2     | Bit1                         | Bit0    |

| Bit Name   | TCPB_LD | TCPB_CK1 | ТСРВ_СКО                     | TCPB_EN |

| Read/Write | R/W     | R/W      | R/W                          | R/W     |

$\diamond$  TCPBC: Timer/counter B control register [R/W] : 013<sub>H</sub> , default value [0000]

TCPB\_EN : control enable timer/counter B counting

=0 : disable TCPB

=1 : enable TCPB

TCPB\_CK1, TCPB\_CK0 : select clock sources for TCPB except GREEN mode as the following table:

| TCPB_CK1 | TCPB_CK0 | clock source     |

|----------|----------|------------------|

| 0        | 0        | Fcpu (CPU clock) |

| 0        | 1        | PC2              |

| 1        | 0        | RC16KHz (OSCL)   |

| 1        | 1        | PFD (from TCPC)  |

TCPB\_LD : control auto-reload function of timer/counter B

=0 : disable auto-reload function

| _ |

|---|

|   |

| _ |

### TTR011 (1K ROM MCU)

Page

### Preliminary

=1 : enable auto-reload function

♦ TCPBDLL: Low nibble register for low data TCPBDL [R/W] : 014<sub>H</sub>, default value [0000]

| Register   | Bit3    | Bit2    | Bit1    | Bit0    |

|------------|---------|---------|---------|---------|

| Bit Name   | TCPBDL3 | TCPBDL2 | TCPBDL1 | TCPBDL0 |

| Read/Write | R/W     | R/W     | R/W     | R/W     |

TCPBDL3~TCPBDL0: low nibble for low data buffer TCPBDL.

$\diamond$  TCPBDLH: High nibble register for low data TCPBDL [R/W] : 015<sub>H</sub>, default value [0000]

| Register   | Bit3    | Bit2 Bit1 |         | Bit0    |

|------------|---------|-----------|---------|---------|

| Bit Name   | TCPBDL7 | TCPBDL6   | TCPBDL5 | TCPBDL4 |

| Read/Write | R/W     | R/W       | R/W     | R/W     |

TCPBDL7~TCPBDL4: high nibble for low data buffer TCPBDL.

$\diamond$  TCPBDHL: low nibble register for high data TCPBDH [R/W] : 016<sub>H</sub>, default value [0000]

| Register   | Bit3    | Bit2    | Bit1    | Bit0    |

|------------|---------|---------|---------|---------|

| Bit Name   | TCPBDH3 | TCPBDH2 | TCPBDH1 | TCPBDH0 |

| Read/Write | R/W     | R/W     | R/W     | W       |

TCPBDH3~TCPBDH0: low nibble for high data buffer TCPBDH.

$\diamond$  TCPBDHH: high nibble register for high data TCPBDH [R/W] : 017<sub>H</sub>, default value [0000]

| Register   | Bit3    | Bit2    | Bit1    | Bit0    |

|------------|---------|---------|---------|---------|

| Bit Name   | TCPBDH7 | TCPBDH6 | TCPBDH5 | TCPBDH4 |

| Read/Write | R/W     | R/W     | R/W     | R/W     |

TCPBDH7~TCPBDH4: high nibble for high data buffer TCPBDH.

#### Figure 7: Timer/counter B (TCPB) circuit

#### Timer

When TCPB works as a timer in auto-reload mode, the user software sets the two pre-load data buffers, TCPBDH (output high level) and TCPBDL (output low level), for periodic timing generation. After initialization, the user software starts TCPB to count by setting TCPB\_EN to "1", the TCPB cycle period is:

#### Tc = (selected clock cycle) \* (TCPBDH+TCPBDL)

When writing data to the TCPBDH, the data will also be loaded to counter if TCPB\_EN is "0". The 1's complement value of TCPBDH will be pre-loaded into counter TCPB as initial value. Writing TCPB\_EN to "1" starts the count-up function. The timer reloads TCPBDL to counter as TCPB up-counts and reaches the value of "FF<sub>H</sub>" or 255. After TCPBDL reloaded to counter, the next reload data is TCPBDH. The TCPBDH and TCPBDL will be re-loaded to counter alternately. When the TCPBDH is reloaded, the overflow TCPBOV and the interrupt request flag TCPB\_IF will be active. If enabling the corresponding interrupt enable bit, the INT circuit will activate MCU interrupt service routine.

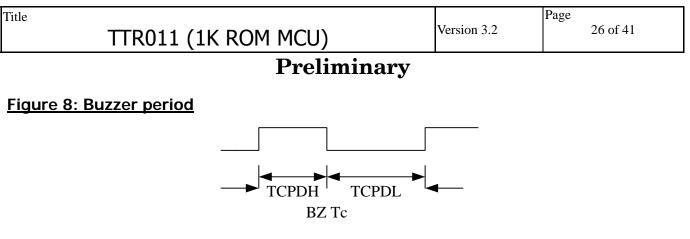

#### > BZ

The buzzer feature is active in TCPB, as the BZ\_EN bit is set to 1 in the TBC/BZC register. The buzzer output the waveform to the PB3 pin. The auto-reload function will be turned on automatically no matter what the TCPB\_LD bit is. Usually the user software will disable the interrupt feature for tone or melody generation. The BZ frequency is:

#### BZ frequency = (selected clock frequency) / (TCPDH+TCPDL)

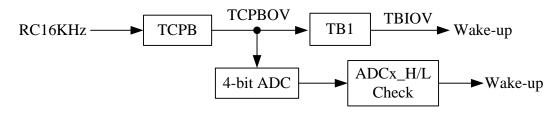

#### > TCPB and TB1 in GREEN mode

The combination of TCPB and TB1 provides many features in GREEN mode. In this mode, the input clock of TCPB is fixed to OSCL (16KHz), and runs in auto-reload mode. After automatically counting up and reloading TCPBDH/TCPBDL in order, the overflow TCPBOV is active to generate one ADC check procedure which measure ADC at one selected channel and check the conversion result with the High/Low limit by hardware circuit. The four channels AD0~3 will be selected in order at each overflow. Before the ADC check procedure for some channel going, it will confirm The ADxWKEN bit of the channel is set to "1" in the AD\_WKEN register. If the user software doesn't want to do this check procedure for some channel, it can set the corresponding ADxWKEN bit to "0", and leave nothing to do in this overflow. The period time for this ADC check procedure is:

#### Tp\_adcc = (period of 16KHz) \* (TCPBDH+TCPBDL)

No matter what the TCPB\_IE bit is, the interrupt from the overflow TCPBOV will be disabled in GREEN mode, and its interrupt flag is also left alone. No matter what the ADC\_IE bit is, the interrupt after ADC conversion complete will be disabled in the ADC check procedure, and its interrupt flag is also left no change. If the ADC conversion result is above the high limit ADx\_H or below the low limit ADx\_L in the ADC check procedure, the wake-up will be invoked. The user software can read the ADC wakeup bit of the WK\_FG register to make sure.

The input clock of TB1 is fixed to TCPBOV in GREEN mode. The overflow TB1OV will set the Auto Time Out bit of the WK\_FG register and invoke the CPU to wake up. No matter what the TB1\_IE bit is, the interrupt from the overflow TB1OV will be disabled in GREEN mode, and its interrupt flag is also left no change. The period time for TB1OV is:

#### Tp\_tb1 = (Tp\_adc) \* (selected overflow count)

The user software can choose the period time to do the ADC check procedure. If its power consumption is the most concern, it can select the maximum period time of TCPBOV:

| Title               |             | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 27 of 41 |

If the longest GREEM mode is also wanted, the user software can choose the longest overflow time of TB1. The maximum period time is:

Max. Tp\_tb1 = (31.875 ms) \* (2048) ~= 65.28 s

#### Figure 9: Combination circuits in GREEN mode

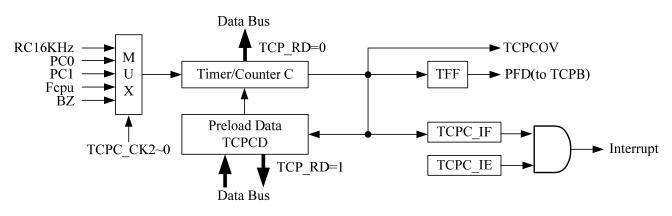

#### ♦ 8 bits Timer/counter C for TCPC

The 8-bits timer/counter C with pre-load data buffer provides five clock sources. The clock sources includes: OSCL (16Khz), PC0, PC1, Fcpu (CPU clock), and BZ clock from TCPB. The TCPCOV is the overflow signal of TCPC, and its rising edge will set the relative INT flag.

When the TCPC\_EN bit in the TCPCC register is "0", the pre-load data buffers, TCPCDH and TCPCDL, will keep being loaded into counter. Any value written to TCPCDH and TCPCDL is also loaded to counter. After setting the TCPC\_EN bit to "1", the counter starts to increase according to the clock source. The counter will be reloaded from TCPCDH and TCPCDL until overflow occurs, if enabling the auto-load function by writing the TCPC\_LD bit to "1" in the CTLA register.

The overflow signal of TCPC is TCPCOV. The rising edge of TCPCOV will set the relative INT flag. The TCPCOV will be active after TCPC counts up from the 1's complement of TCPCD to "FF<sub>H</sub>". In the condition that TCPCD is written " $00_{\text{H}}$ ", Enabling TCPC will make a immediate counter overflow. It will activate TCPCOV, and count across to " $00_{\text{H}}$ ".

When setting the TCP\_RD bit to "0" in the CTLA register, Reading TCPCDL and TCPCDH will get the values from the counter of TCPC. Because the counter is loaded the 1's complement of TCPCD and counts up, the value read from the counter needs to be translated. If setting TCP\_RD bit to 1, Reading TCPCDL and TCPCDH get the values from the pre-load data buffer of TCPC.

| ♦ TCPCC: Timer/counter C control register [R/W] : 01B <sub>H</sub> , default value [0000 | $\diamond$ | TCPCC: Timer/counter | C control register [R/W] | $: 01B_{H}$ , default v | alue [0000] |

|------------------------------------------------------------------------------------------|------------|----------------------|--------------------------|-------------------------|-------------|

|------------------------------------------------------------------------------------------|------------|----------------------|--------------------------|-------------------------|-------------|

| Register | Bit3     | Bit2     | Bit1     | Bit0    |

|----------|----------|----------|----------|---------|

| Bit Name | TCPC_CK2 | TCPC_CK1 | TCPC_CK0 | TCPC_EN |

| Title                                             |                   |               |               |               | Version 3.2    | Page 28 of 41        |  |

|---------------------------------------------------|-------------------|---------------|---------------|---------------|----------------|----------------------|--|

|                                                   | TTR01             | 1 (1K ROM     | 1 MCU)        |               | version 5.2    | 20 01 41             |  |

|                                                   | Preliminary       |               |               |               |                |                      |  |

|                                                   | Read/Write        | R/W           | R/W           | R/W           | R/W            |                      |  |

| TCPC_EN : control enable timer/counter C counting |                   |               |               |               |                |                      |  |

|                                                   | =0 : disable TCPC |               |               |               |                |                      |  |

|                                                   | =1 : enable TCPC  |               |               |               |                |                      |  |

|                                                   | TCPC_CK2, TCPC_   | _CK1, & TCPC_ | _CK0 : select | t clock sourc | es for TCPC as | the following table: |  |

| /        | /        |          |                  |

|----------|----------|----------|------------------|

| TCPC_CK2 | TCPC_CK1 | TCPC_CK0 | clock source     |

| 0        | 0        | 0        | RC16KHz (OSCL)   |

| 0        | 0        | 1        | PC0              |

| 0        | 1        | 0        | PC1              |

| 0        | 1        | 1        | Fcpu (CPU clock) |

| 1        | x        | Х        | BZ (from TCPB)   |

$\diamond$  TCPCDL: Low nibble register for data TCPCD [R/W] : 01C<sub>H</sub> , default value [0000]

| Register   | Bit3   | Bit2   | Bit1   | Bit0   |

|------------|--------|--------|--------|--------|

| Bit Name   | TCPCD3 | TCPCD2 | TCPCD1 | TCPCD0 |

| Read/Write | R/W    | R/W    | R/W    | R/W    |

TCPCD3~TCPCD0: low nibble for data buffer TCPCD.

$\diamond$  TCPCDH: High nibble register for data TCPCD [R/W] : 01D<sub>H</sub> , default value [0000]

| Register   | Bit3   | Bit2   | Bit1   | Bit0   |

|------------|--------|--------|--------|--------|

| Bit Name   | TCPCD7 | TCPCD6 | TCPCD5 | TCPCD4 |

| Read/Write | R/W    | R/W    | R/W    | R/W    |

TCPD7~TCPD4: high nibble for data buffer TCPCD.

#### Figure 10: Timer/counter C (TCPC) circuit

| Title               |             | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 29 of 41 |

#### > Timer

When TCPC works as a timer in auto-reload mode, the user software sets the pre-load data buffer TCPCD for periodic timing generation. After initialization, the user software starts TCPC to count by setting TCPC\_EN to "1", the TCPC cycle period is:

#### Tc = (selected clock cycle) \* (TCPCD)

When writing data to the TCPCD, the data will also be loaded to counter if TCPC\_EN is "0". The 1's complement value of TCPCD will be pre-loaded into counter TCPC as initial value. Writing TCPC\_EN to "1" starts the count-up function. If in auto-reload mode, the timer reloads TCPCD to counter as TCPC up-counts and reaches the value of "FF<sub>H</sub>" or 255. At the same time, the overflow TCPCOV and the interrupt request flag TCPC\_IF will be active. If enabling the corresponding interrupt enable bit, the INT circuit will activate MCU interrupt service routine.

#### > PFD

The PFD signal comes from which divides the overflow TCPCOV by two. The TCPB can select PFD as the clock source. This provides a longer period of timer by combining TCPB and TCPC.

#### ♦ PORT A , B , C

There are three ports can be used. All the pins of the ports are I/O pins. The pins of port A also are combined with the analog input pins of ADC. Writing the I/O definition registers (PAC, PBC, and PCC) can change them to be input or output pins.

In output mode, writing the data register (PA, PB, and PC) sets them to what values they output, and reading the data registers get what values are stored from register. In input mode, reading the data registers get what values are inputted from pins.

Writing the pull-high registers (PB\_PH and PC\_PH) turn-on or turn-off the pull-high of the input pins. The following table collects all the registers about these ports.

| Address          | Register | Bit3 | Bit2 | Bit1 | Bit0 | Default |

|------------------|----------|------|------|------|------|---------|

| 005              | DA       | PA3  | PA2  | PA1  | PA0  |         |

| 00F <sub>Н</sub> | PA       | R/W  | R/W  | R/W  | R/W  | uuuu    |

| 010              | חח       | PB3  | PB2  | PB1  | PB0  |         |

| 010 <sub>H</sub> | PB       | R/W  | R/W  | R/W  | R/W  | uuuu    |

|                     |             | Page     |

|---------------------|-------------|----------|

| TTR011 (1K ROM MCU) | Version 3.2 | 30 of 41 |

### Preliminary

| 011              | DC                    | PC3    | PC2    | PC1    | PC0    |        |

|------------------|-----------------------|--------|--------|--------|--------|--------|

| 011 <sub>Н</sub> | н РС                  | R/W    | R/W    | R/W    | R      | uuuu   |

| 000              | DAC                   | PAC3   | PAC2   | PAC1   | PAC0   | 1111   |

| 00D <sub>H</sub> | PAC                   | R/W    | R/W    | R/W    | R/W    | 1111   |

| 015              | PBC                   | PBC3   | PBC2   | PBC1   | PBC0   | - 1111 |

| 01E <sub>H</sub> | ICH PDC               | R/W    | R/W    | R/W    | R/W    | 1111   |

| 01E              | PCC                   | PCC3   | PCC2   | PCC1   | PCC0   | - 1111 |

| 01F <sub>Н</sub> | PLL                   | R/W    | R/W    | R/W    | R      |        |

| 064              | עם פט                 | PB3_PH | PB2_PH | PB1_PH | PB0_PH | 0000   |

| 064 <sub>н</sub> | 54 <sub>H</sub> PB_PH | R/W    | R/W    | R/W    | R/W    | 0000   |

|                  | PC3_PH                | PC2_PH | PC1_PH | PC0_PH | 0000   |        |

| 065 <sub>н</sub> | PC_PH                 | R/W    | R/W    | R/W    | R/W    | - 0000 |

- $\diamond$  PA [00F<sub>H</sub>] : Port A DATA register

- $\diamond$  PAC[00D<sub>H</sub>] : Port A I/O definition register

- =1 : setting it to be input pin.

- =0 : setting it to be output pin

- ♦ PB  $[010_{H}]$  : Port B DATA register

- $\diamond$  PBC [01E<sub>H</sub>] : Port B I/O definition register

- =1 : setting it to be input pin

- =0 : setting it to be output pin

- $\diamond$  PB\_PH [064<sub>H</sub>] : Port B Pull\_high control

- =1 : enable pull\_high resister when it is input pin

- =0 : disable pull\_high resister

- $\diamond$  PC [011<sub>H</sub>] : Port C DATA register

- $\diamond$  PCC [01F<sub>H</sub>] : Port C I/O definition register

- =1 : setting to be input pin.

- =0 : setting to be output pin

- $\diamond$  PC\_PH [065<sub>H</sub>] : Port C Pull\_high enable

- =1 : enable pull\_high resister when it is input pin

- =0 : disable pull\_high resister

TTR011 (1K ROM MCU)

Page

### Preliminary

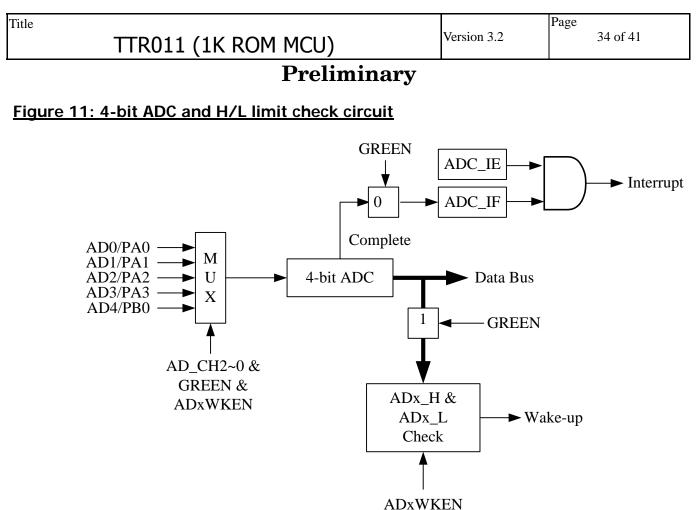

### ♦ 4-bit ADC

The following table collects all the registers about 4-bit ADC.

| Address          | Register | Bit3     | Bit2     | Bit1     | Bit0     | Default |

|------------------|----------|----------|----------|----------|----------|---------|

| 014              |          | ADEN     | AD_CH2   | AD_CH1   | AD_CH0   | 0000    |

| 01A <sub>H</sub> | ADC_CTL1 | R/W      | R/W      | R/W      | R/W      | 0000    |

| 050              |          | AD0_TOP3 | AD0_TOP2 | AD0_TOP1 | AD0_TOP0 |         |

| 058 <sub>Н</sub> | AD0_H    | R/W      | R/W      | R/W      | R/W      | uuuu    |

|                  | AD0_BOT3 | AD0_BOT2 | AD0_BOT1 | AD0_BOT0 |          |         |

| 059 <sub>Н</sub> | AD0_L    | R/W      | R/W      | R/W      | R/W      | uuuu    |

|                  |          | AD1_TOP3 | AD1_TOP2 | AD1_TOP1 | AD1_TOP0 |         |

| 05А <sub>Н</sub> | AD1_H    | R/W      | R/W      | R/W      | R/W      | uuuu    |

|                  |          | AD1_BOT3 | AD1_BOT2 | AD1_BOT1 | AD1_BOT0 |         |

| 05В <sub>Н</sub> | AD1_L    | R/W      | R/W      | R/W      | R/W      | uuuu    |

| 050              |          | AD2_TOP3 | AD2_TOP2 | AD2_TOP1 | AD2_TOP0 |         |

| 05С <sub>Н</sub> | AD2_H    | R/W      | R/W      | R/W      | R/W      | uuuu    |

|                  |          | AD2_BOT3 | AD2_BOT2 | AD2_BOT1 | AD2_BOT0 |         |

| 05D <sub>Н</sub> | AD2_L    | R/W      | R/W      | R/W      | R/W      | uuuu    |

| 05E <sub>Н</sub> |          | AD3_TOP3 | AD3_TOP2 | AD3_TOP1 | AD3_TOP0 |         |

| USLH             | AD3_H    | R/W      | R/W      | R/W      | R/W      | uuuu    |

| OFE              |          | AD3_BOT3 | AD3_BOT2 | AD3_BOT1 | AD3_BOT0 |         |

| 05F <sub>Н</sub> | AD3_L    | R/W      | R/W      | R/W      | R/W      | uuuu    |

| 060              | ADC_D    | AD_D3    | AD_D2    | AD_D1    | AD_0     |         |

| 060 <sub>Н</sub> | ADC_D    | R        | R        | R        | R        | uuuu    |

| 061 <sub>H</sub> | ADC_PA   | AD3/PA3  | AD2/PA2  | AD1/PA1  | AD0/PA0  | 0000    |

|                  |          | R/W      | R/W      | R/W      | R/W      | 0000    |

| 0(2)             |          | AD3WKEN  | AD2WKEN  | AD1WKEN  | ADOWKEN  | 0000    |

| 062 <sub>Н</sub> | AD_WKEN  | R/W      | R/W      | R/W      | R/W      | 0000    |

| 0(2              |          | ADCK1    | ADCK0    |          | AD4/PB0  | 00.0    |

| 063 <sub>Н</sub> | ADC_CTL2 | R/W      | R/W      | R0       | R/W      | 00-0    |

| 000              |          | ADC _IE  | TCPC_IE  | TCPB_IE  | TCPA_IE  | 0000    |

| 009 <sub>Н</sub> | INTC1    | R/W      | R/W      | R/W      | R/W      | 0000    |