ETR05022-009

# 18V Driver Transistor Built-In Synchronous Step-Down DC/DC Converter

### **■**GENERAL DESCRIPTION

The XC9248 series is 18V bootstrap synchronous step-down DC/DC converter with built-in Nch-Nch driver transistors. With an input voltage range from 4.5V to 18V and a maximum output current of 2.2A, the series is suitable for digital home appliance power supplies and can be used with small ceramic capacitors.

The series has a 0.8V reference voltage, and using externally connected resistors, the output voltage can be set freely from 1.0V to 12V.

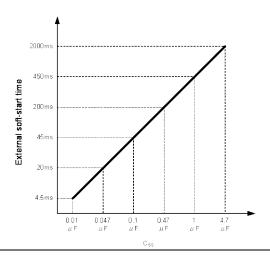

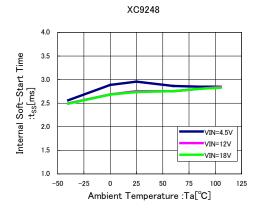

The control method is synchronous PWM (Source/ Sink). The soft start time is internally set to 2.8ms (TYP.), also can be adjusted using external capacitor.

With UVLO (Under Voltage Lock Out) function, the internal driver transistors are forced OFF when input voltage falls down below 3.8V (TYP.).

The series includes over current protection,  $V_{\text{OUT}}$  short-circuit protection, Lx short-circuit protection,  $V_{\text{OUT}}$  overvoltage protection and thermal shutdown.

### ■APPLICATIONS

- Digital home appliance

- Office automation equipment

- Note PCs / Tablet PCs

- Car accessories power supplies

### **■**FEATURES

Input Voltage : 4.5V ~ 18V

Output Voltage :  $1.0V \sim 12V (V_{FB}=0.8V\pm1.5\%)^{(*1)}$

Output Current : 2.2A

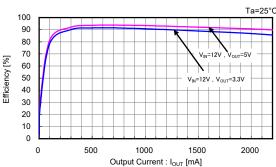

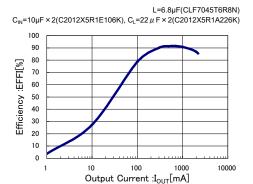

$Efficiency \hspace{1cm} : \hspace{1.5cm} 93.8\% \ ^{(^{*}1)} @V_{IN} = 12V, V_{OUT} = 5V, \hspace{1.5cm} I_{OUT} = 700 mA$

Oscillation Frequency : 500kHz Maximum Duty Cycle : 79%

Soft-Start Time : Fixed 2.8ms, set by external capacitor

Protection Circuit : UVLO

High side over current protection

Low side over current protection

Vout Short-circuit Protection

L<sub>X</sub> Short-circuit Protection

Vout Over voltage protection

Thermal shutdown

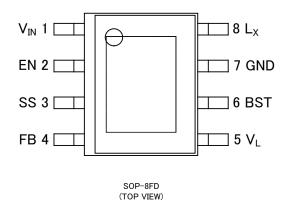

Package : SOP-8FD

Environmentally Friendly : EU RoHS Compliant, Pb Free

(\*1) Performance depends on external components and wiring on the PCB.

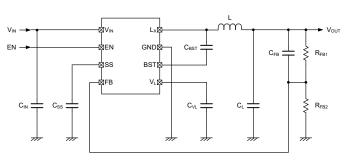

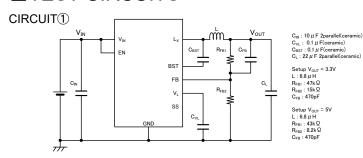

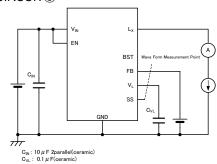

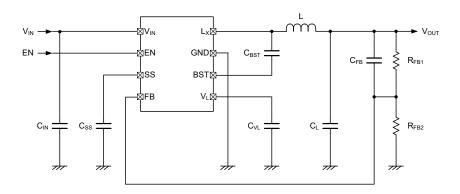

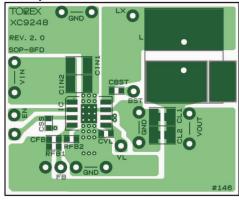

### ■TYPICAL APPLICATION CIRCUIT

# ■TYPICAL PERFORMANCE CHARACTERISTICS

Efficiency vs. Output Current

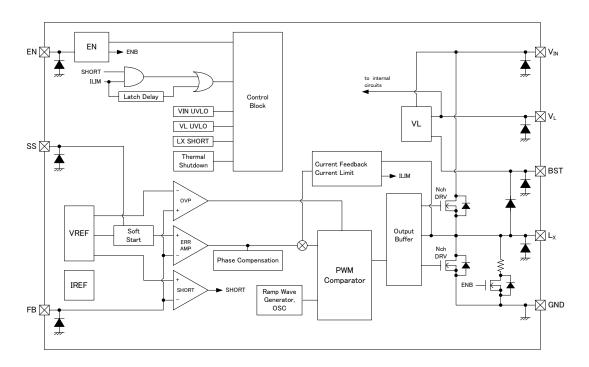

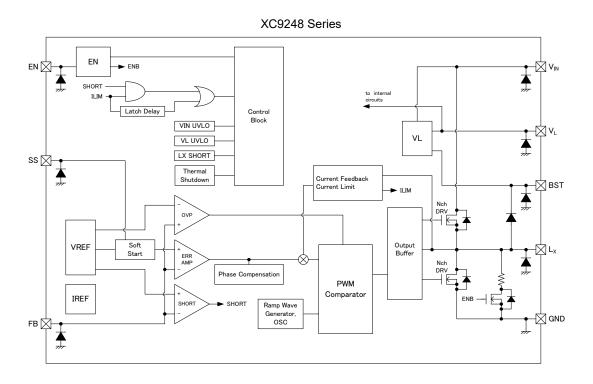

# ■BLOCK DIAGRAM

<sup>\*</sup> Internal diodes include an ESD protection diode and a parasitic diode.

# **■PRODUCT CLASSIFICATION**

### Ordering Information

XC9248123456-7

| DESIGNATOR       | ITEM                        | SYMBOL | DESCRIPTION                 |

|------------------|-----------------------------|--------|-----------------------------|

|                  | TYPF                        | А      | Defends Calcation Code      |

| U                | I TYPE                      | В      | Refer to Selection Guide    |

| 23               | FB Voltage                  | 08     | FB voltage is fixed in 0.8V |

| 4                | Oscillation Frequency       |        | 500kHz                      |

| <b>56-7</b> (*1) | ⑤-⑦ <sup>(*1)</sup> Package |        | SOP-8FD (1,000pcs/Reel)     |

<sup>(\*1)</sup> The "-G" suffix denotes Halogen and Antimony free as well as being fully EU RoHS compliant.

### Selection Guide

| TYPE | CURRENT LIMITER | LATCH FOR<br>CURRENT LIMITER | LATCH FOR<br>Vout-SHORT | LATCH FOR<br>Lx-SHORT (*2) |

|------|-----------------|------------------------------|-------------------------|----------------------------|

| Α    | YES             | YES (*1)                     | YES                     | YES                        |

| В    | YES             | NO                           | NO                      | YES                        |

| TYPE | ENABLE | UVLO | C <sub>L</sub><br>AUTO-DISCHARGE | THERMAL<br>SHUTDOWN |

|------|--------|------|----------------------------------|---------------------|

| Α    | YES    | YES  | YES                              | YES                 |

| В    | YES    | YES  | YES                              | YES                 |

<sup>(\*1)</sup> The over-current protection latch is an integral latch type.

<sup>(\*2)</sup> To prevent an extremely large rush current from flowing in the event that Lx is short-circuited, both the A & B types have an Lx short protection latch function.

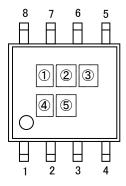

# **■PIN CONFIGURATION**

<sup>\*</sup>The dissipation pad for the SOP-8FD package should be solder-plated in recommended mount pattern and metal masking so as to enhance mounting strength and heat release. If the pad needs to be connected to other pins, it should be connected to the GND (No.7) pin.

## **■ PIN ASSIGNMENT**

| PIN NUMBER | PIN NAME                                 | FUNCTIONS         |  |

|------------|------------------------------------------|-------------------|--|

| 1          | Vin                                      | Power Input       |  |

| 2          | EN                                       | Enable            |  |

| 3          | SS External Soft-start                   |                   |  |

| 4          | FB FB Voltage Monitor                    |                   |  |

| 5          | V <sub>L</sub> Internal Regulator Output |                   |  |

| 6          | BST                                      | Pre Driver Supply |  |

| 7          | GND                                      | GND Ground        |  |

| 8          | Lx                                       | Switching Output  |  |

## **■**FUNCTION

| PIN NAME | SIGNAL | STATUS               |  |

|----------|--------|----------------------|--|

|          | L      | Stand-by             |  |

| EN       | Н      | Active               |  |

|          | OPEN   | Undefined State (*1) |  |

<sup>(\*1)</sup> On the XC9248 series, causes unspecified behavior and thus is prohibited.

# ■ ABSOLUTE MAXIMUM RATINGS

| PARAMETER                      |                               | SYMBOL           | RATINGS                                                       | UNITS |  |

|--------------------------------|-------------------------------|------------------|---------------------------------------------------------------|-------|--|

| V <sub>IN</sub> Pin Voltage    |                               | VIN              | -0.3 ~ 20                                                     | V     |  |

| EN Pin                         | Voltage                       | V <sub>EN</sub>  | -0.3 ~ 20                                                     | V     |  |

| L <sub>X</sub> Pin '           | Voltage                       | V <sub>LX</sub>  | -0.3 ~ V <sub>IN</sub> + 0.3 or 20 <sup>(*1)</sup>            | V     |  |

| BST Pin Voltage                |                               | V <sub>BST</sub> | $V_L - 0.3 \sim V_L + 20$<br>$V_{LX} - 0.3 \sim V_{LX} + 5.5$ |       |  |

| V <sub>∟</sub> Pin Voltage     |                               | V <sub>VL</sub>  | -0.3 ~ V <sub>IN</sub> + 0.3 or 5.5 <sup>(*2)</sup>           | V     |  |

| FB Pin Voltage                 |                               | V <sub>FB</sub>  | -0.3 ~ 5.5                                                    | V     |  |

| SS Pin Voltage                 |                               | V <sub>SS</sub>  | -0.3 ~ 5.5                                                    | V     |  |

| L <sub>X</sub> Pin             | Current                       | I <sub>LX</sub>  | ±5                                                            | Α     |  |

| V <sub>L</sub> Pin             | Current                       | I <sub>VL</sub>  | 85                                                            | mA    |  |

| Dower Dissipation              |                               |                  | 300                                                           |       |  |

| Power Dissipation<br>(Ta=25°C) | SOP-8FD                       | Pd               | 1500 (40mm x 40mm Standard board) (*3)                        | mW    |  |

| (1a-25 C)                      |                               |                  | 2500 (JESD51-7 board) <sup>(*3)</sup>                         |       |  |

| Operating Ambi                 | Operating Ambient Temperature |                  | -40 ~ 105                                                     | °C    |  |

| Storage Temperature            |                               | Tstg             | -50 ~ 125                                                     | °C    |  |

All voltages are described based on the ground voltage.

$<sup>^{(\</sup>mbox{\tiny $^{\prime}$}\mbox{\tiny $1$})}$  The maximum value should be either  $V_{\mbox{\tiny $1N$}}\mbox{\tiny $+0.3V$}$  or 20V in the lowest.

$<sup>^{(\</sup>mbox{\tiny{$^{\circ}}$2)}}$  The maximum value should be either  $V_{\mbox{\tiny{$|N$}}}\text{+}0.3V$  or 5.5V in the lowest.

<sup>(\*3)</sup> The power dissipation figure shown is PCB mounted and is for reference only. Please refer to PACKAGING INFORMATION for the mounting condition.

# **■**ELECTRICAL CHARACTERISTICS

XC9248 Series Ta=25°C

| XC9248 Series                       |                     |                                                                                                                                            |         |          |       |        | Ia=25℃      |

|-------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-------|--------|-------------|

| PARAMETER                           | SYMBOL              | CONDITIONS                                                                                                                                 | MIN.    | TYP.     | MAX.  | UNITS  | CIRCUIT     |

|                                     |                     | When connected to external components                                                                                                      |         |          |       |        |             |

| Operating Voltage Range             | V <sub>IN</sub>     | V <sub>IN</sub> ≦7V: Setup V <sub>OUT</sub> =3.3V                                                                                          | 4.5     | -        | 18    | V      | 1           |

|                                     |                     | V <sub>IN</sub> >7V: Setup V <sub>OUT</sub> =5V                                                                                            |         |          |       |        |             |

| FB Voltage                          | V <sub>FB</sub>     | V <sub>FB</sub> =Sweep (0.812V→0.788V), V <sub>SS</sub> =OPEN                                                                              | 0.788   | 0.800    | 0.812 | V      | 2           |

| FB Voltage                          | VFB/                | 15 1 (4.4. 3.4.7) 50 1                                                                                                                     |         |          |       |        |             |

| Temperature Characteristics         | (VFB•ΔTopr)         | -40°C≦Topr≦105°C                                                                                                                           |         | ±40      |       | ppm/°C | 2           |

| Maximum Output Current              | I <sub>OUTMAX</sub> | When connected to external components                                                                                                      | 2.2(*1) | _        | _     | Α      | (1)         |

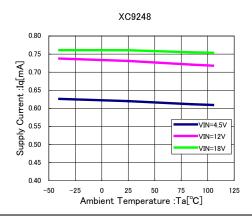

| Supply Current                      | I <sub>q</sub>      | V <sub>IN</sub> =V <sub>EN</sub> =18V, V <sub>ER</sub> =0.9V                                                                               |         | 0.76     | 1.10  | mA     | 3           |

| Stand-by Current                    |                     | V <sub>IN</sub> =18V, V <sub>EN</sub> =0V, V <sub>EB</sub> =OPEN                                                                           | _       | 38       | 51    |        | 3           |

|                                     | I <sub>STB</sub>    | V <sub>FR</sub> =0.7V, V <sub>SS</sub> =OPEN                                                                                               |         |          |       | μA     | 2           |

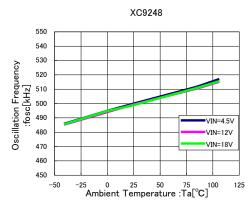

| Oscillation Frequency               | f <sub>osc</sub>    | 15 , 66                                                                                                                                    | 450     | 500      | 550   | kHz    |             |

| Maximum Duty Cycle                  | D <sub>max</sub>    | V <sub>FB</sub> =0.7V, V <sub>SS</sub> =OPEN                                                                                               | 74      | 79       | -     | %      | 2           |

|                                     |                     | V <sub>IN</sub> =Sweep (4.5V→3.5V) , V <sub>EN</sub> =2V, V <sub>FB</sub> =0.9V                                                            |         |          |       |        |             |

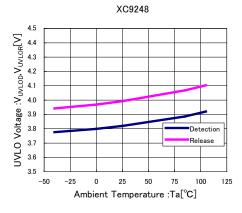

| UVLO Detection Voltage              | $V_{UVLOD}$         | Voltage when V <sub>L</sub> pin changes from                                                                                               | 3.50    | 3.80     | 4.45  | V      | 4           |

|                                     |                     | "H" level to "L" level (*2)                                                                                                                |         |          |       |        |             |

|                                     |                     | $V_{IN}$ =Sweep (3.5V $\rightarrow$ 4.5V), $V_{EN}$ =2V, $V_{FB}$ =0.9V                                                                    |         |          |       |        |             |

| UVLO Release Voltage                | $V_{UVLOR}$         | Voltage when V <sub>∟</sub> pin changes from                                                                                               | 3.55    | 3.90     | 4.50  | V      | 4           |

|                                     |                     | "L" level to "H" level (*2)                                                                                                                |         |          |       |        |             |

| Low side Current Limit              | I <sub>LIMLS</sub>  | $V_{OUT}$ =4.5V (Forced), Bottom point of $L_X$ pin current                                                                                | 2.1     | -        | -     | Α      | 7           |

| Integral Latch Time                 |                     | $V_{FB}$ =0.9V, $I_{LX} = I_{LIMLS}$                                                                                                       |         |          |       |        |             |

| (Type A)                            | $t_{LAT}$           | Time until SS pin changes from                                                                                                             | 0.4     | 1.1      | 1.8   | ms     | (5)         |

| (Type A)                            |                     | "H" level to "L" level (*2)                                                                                                                |         |          |       |        |             |

| Into your Coff about Time o         |                     | V <sub>IN</sub> =12V, V <sub>EN</sub> =2V, V <sub>FB</sub> =0.72V, V <sub>SS</sub> =OPEN                                                   |         | 2.0      |       |        | <b>①</b>    |

| Internal Soft-start Time            | t <sub>ss</sub>     | Time until L <sub>x</sub> pin oscillates                                                                                                   | -       | 2.8      | -     | ms     | 2           |

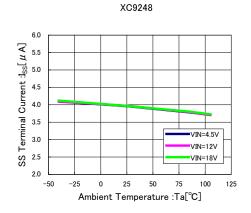

| SS Terminal Current                 | I <sub>SS</sub>     | V <sub>SS</sub> =0V, V <sub>LX</sub> =V <sub>FB</sub> =OPEN                                                                                | 2       | 4        | 6     | μΑ     | 6           |

|                                     | .,                  | V <sub>FB</sub> =0.72V, V <sub>SS</sub> =OPEN                                                                                              |         | 4.0      |       | .,     |             |

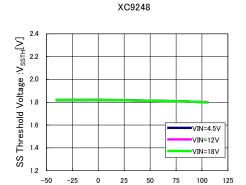

| SS Threshold Voltage                | V <sub>SSTH</sub>   | Voltage when L <sub>x</sub> pin oscillates                                                                                                 | 1.2     | 1.8      | 2.4   | V      | 2           |

| OVP Detection Voltage               | V <sub>OVPD</sub>   | V <sub>FB</sub> =Sweep (0.788V→1.2V), V <sub>SS</sub> =OPEN                                                                                | -       | 0.9      | 1.2   | V      | 2           |

| Ŭ                                   |                     | Setup V <sub>OUT</sub> =5V, I <sub>OUT</sub> =0.7A                                                                                         |         |          |       |        |             |

| Efficiency                          | EFFI (*3)           | When connected to external components                                                                                                      | -       | 93.8     | -     | %      | 8           |

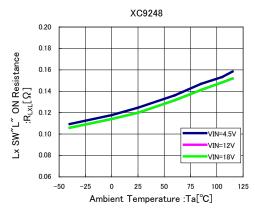

| Lx SW "H" ON Resistance             | R <sub>LXH</sub>    | '                                                                                                                                          | _       | 0.12(*4) | _     | Ω      | _           |

| Lx SW "L" ON Resistance             | R <sub>LXL</sub>    |                                                                                                                                            | _       | 0.12(*4) | _     | Ω      | _           |

| EX GVV E GIVITEGISTATIOS            | TALXL               | V <sub>IN</sub> =12V, V <sub>FB</sub> =0.9V, V <sub>EN</sub> =Sweep (0.2V→1.4V)                                                            |         | 0.12     |       | 32     |             |

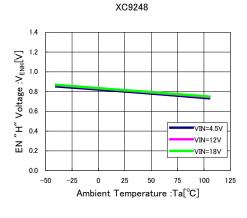

| EN "H" Voltage                      | $V_{ENH}$           | Voltage when $V_L$ pin changes from                                                                                                        | 1.4     | _        | 18    | V      | 4           |

| Liv ii voltage                      | V ENH               | "L" level to "H" level (*2)                                                                                                                | 1.4     |          | 10    | · •    | •           |

|                                     |                     | V <sub>IN</sub> =12V, V <sub>FB</sub> =0.9V, V <sub>EN</sub> =Sweep (1.4V→0.2V)                                                            |         |          |       |        |             |

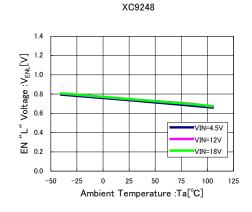

| ENL"I "\/oltogo                     | V                   | $V_{\text{IN}}$ 12V, $V_{\text{FB}}$ 0.3V, $V_{\text{EN}}$ 3Weep (1.4V $\rightarrow$ 0.2V)<br>Voltage when $V_{\text{I}}$ pin changes from | CND     |          | 0.2   | V      | <b>(4</b> ) |

| EN "L" Voltage                      | $V_{ENL}$           | 5 -1 5                                                                                                                                     | GND     | -        | 0.2   | V      | 4)          |

| LV "L" Commont                      |                     | "H" level to "L" level (*2)                                                                                                                | 4       | 0        |       | ^      | •           |

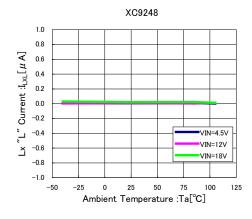

| LX "L" Current                      | I <sub>LXL</sub>    | V <sub>IN</sub> =18V , V <sub>EN</sub> =V <sub>LX</sub> =0V , V <sub>FB</sub> =V <sub>SS</sub> =OPEN                                       | -1      | 0        | -     | μΑ     | 6           |

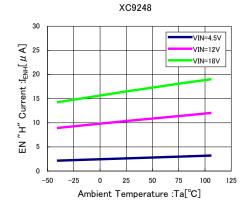

| EN "H" Current                      | I <sub>ENH</sub>    | V <sub>IN</sub> =V <sub>EN</sub> =18V , V <sub>LX</sub> =V <sub>FB</sub> =V <sub>SS</sub> =OPEN                                            | -       | 16       | 21    | μΑ     | 6           |

| EN "L" Current                      | I <sub>ENL</sub>    | V <sub>IN</sub> =18V , V <sub>EN</sub> =0V , V <sub>LX</sub> =V <sub>FB</sub> =V <sub>SS</sub> =OPEN                                       | -0.1    | -        | 0.1   | μΑ     | 6           |

| FB "H" Current                      | Іғвн                | V <sub>IN</sub> =18V , V <sub>EN</sub> =0V , V <sub>FB</sub> =5V , V <sub>LX</sub> =V <sub>SS</sub> =OPEN                                  | -0.1    | -        | 0.1   | μΑ     | 6           |

| FB "L" Current                      | I <sub>FBL</sub>    | V <sub>IN</sub> =18V , V <sub>EN</sub> =V <sub>FB</sub> =0V , V <sub>LX</sub> =V <sub>SS</sub> =OPEN                                       | -0.1    | -        | 0.1   | μΑ     | 6           |

| Thermal Shutdown Temperature        | T <sub>TSD</sub>    |                                                                                                                                            | -       | 150      | -     | °C     | -           |

| Hysteresis Width                    | T <sub>HYS</sub>    |                                                                                                                                            | -       | 25       | -     | °C     | -           |

| C <sub>L</sub> Discharge Resistance | R <sub>DCHG</sub>   | V <sub>IN</sub> =12V , V <sub>EN</sub> =0V , V <sub>LX</sub> =2V , V <sub>FB</sub> =V <sub>SS</sub> =OPEN                                  | -       | 300      | -     | Ω      | 6           |

| C <sub>L</sub> Discharge Current    | Ідсна               | V <sub>IN</sub> =12V , V <sub>EN</sub> =0V , V <sub>LX</sub> =12V , V <sub>FB</sub> =V <sub>SS</sub> =OPEN                                 | -       | 9        | -     | mA     | 6           |

Unless otherwise stated,  $V_{\text{IN}}$ = $V_{\text{EN}}$ =12V

<sup>(\*1)</sup> Mount conditions affect heat dissipation. Maximum output current is not guaranteed when Thermal Shutdown starts to operate earlier.

(\*2) "H"=4.3V~5V, "L"=-0.1V~0.1V

(\*3) EFFI = {[(output voltage)×(output current)]÷[(input voltage)×(input current)]}×100

(\*4) Design value

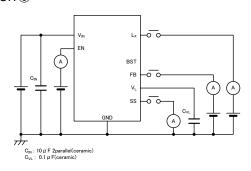

# **■**TEST CIRCUITS

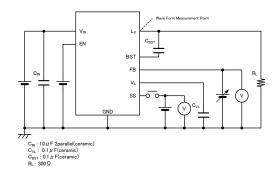

#### CIRCUIT②

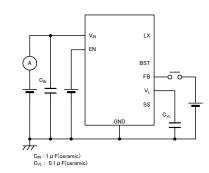

#### CIRCUIT3

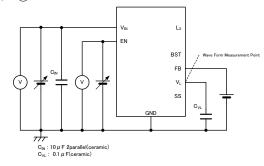

#### CIRCUIT4

#### CIRCUIT®

### CIRCUIT®

### CIRCUIT 7

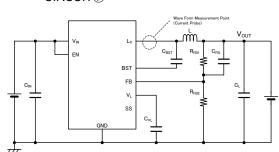

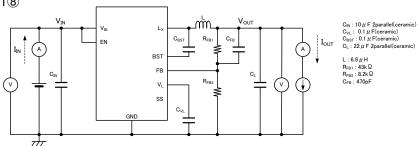

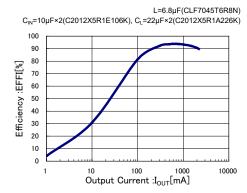

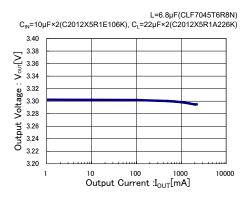

# $C_N: 10 \ \mu \ F \ 2parallel (ceramic)$ $C_{VL}: 0.1 \ \mu \ F (ceramic)$ $C_{BST}: 0.1 \ \mu \ F (ceramic)$ $C_L: 22 \ \mu \ F \ 2parallel (ceramic)$

L : 6.8 μ H R<sub>FB1</sub> : 43k Ω R<sub>FB2</sub> : 8.2k Ω C<sub>FB</sub> : 470pF

# **■**TYPICAL APPLICATION CIRCUIT

#### [Typical Examples]

| Typical Live         | inpics 1     |                |                             |

|----------------------|--------------|----------------|-----------------------------|

|                      | MANUFACTURER | PART NUMBER    | VALUE                       |

|                      | TDK          | CLF10040T100N  | 10 <i>μ</i> Η               |

|                      | TDK          | CLF7045T6R8N   | 6.8 <i>µ</i> H              |

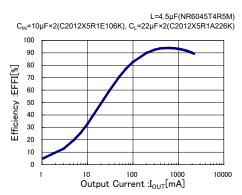

| L                    | TAIYO YUDEN  | NR6045T4R5M    | 4.5 <i>µ</i> H              |

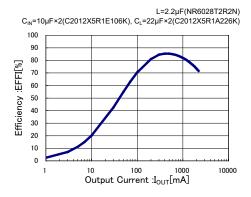

|                      | TAIYO YUDEN  | NR6028T2R2N    | 2.2 µH                      |

| C <sub>IN</sub> (*1) | TDK          | C2012X5R1E106K | 10 µF/25V 2parallel         |

| CIN ( )              | IDK          | C3216X7R1E106K | 10 µF/25V 2parallel         |

|                      |              | C2012X5R1A226M | 22 µF/10V 2parallel         |

| Cı (*1)              | TDK          | C3216X5R1E226M | 22 µF/25V 2parallel         |

| CL( ''               | IDK          | C3225X7R1C226M | 22 дF/16V 2parallel         |

|                      |              | C4532X7R1E226M | 22 µF/25V 2parallel         |

| Css                  |              |                | 0.1 µF <sup>(*2)</sup> /10V |

| C <sub>BST</sub>     |              |                | 0.1 μF/10V                  |

| C <sub>VL</sub>      |              |                | 0.1 μF/10V                  |

<sup>(\*1)</sup> Select components appropriate to the usage conditions (ambient temperature, input & output voltage).

#### <Coil current setting >

For stable operation by current feedback control, the XC9248 series is optimum when the peak-to-peak current (lpk) in the coil is set approximately between 0.5A to 1A. The lpk value can be calculated by using the following equation:

$$lpk[A] = (V_{IN} - V_{OUT}) \times V_{OUT} / V_{IN} / 0.5 / L[\mu H]$$

L : Coil Inductance

### [Examples]

| V <sub>IN</sub> [V] | Vout [V] | L [µH] | lpk [A] |

|---------------------|----------|--------|---------|

| 5.0                 | 1.0      | 2.2    | 0.73    |

| 5.0                 | 2.5      | 3.3    | 0.76    |

| 12.0                | 3.3      | 6.8    | 0.70    |

| 12.0                | 5.0      | 6.8    | 0.86    |

| 18.0                | 5.0      | 10.0   | 0.72    |

| 18.0                | 12.0     | 10.0   | 0.80    |

<sup>(\*2)</sup> For the capacitance value, please refer to P.8 < External soft-start setting >.

# ■TYPICAL APPLICATION CIRCUIT (Continued)

#### <Vour setting>

The output voltage can be set by connecting external dividing resistors. The output voltage is determined by the values of  $R_{FB1}$  and  $R_{FB2}$  as given in the equation below. The total of  $R_{FB1}$  and  $R_{FB2}$  should be less than  $150k\Omega$ . Output voltage range can be set freely from 1.0V to 12V with a 0.8V reference voltage.

$$V_{OUT}=0.8\times(R_{FB1}+R_{FB2})/R_{FB2}$$

Adjust the value of the phase compensation speed-up capacitor  $C_{FB}$  so that  $f_{zfp}=1$  /  $(2 \times \pi \times C_{FB} \times R_{FB1})$  is about 7kHz. Adjustments are required from 5kHz to 50kHz depending on the application, value of inductance (L), and value of load capacitance (C<sub>L</sub>).

#### [Examples]

$$R_{FB1}$$

=47 $k\Omega$ ,  $R_{FB2}$ =15 $k\Omega$ ,  $V_{OUT}$ =0.8 $V\times$ (47 $k\Omega$ +15 $k\Omega$ ) /15 $k\Omega$  =3.3 $V$   $C_{FB}$ =470 $pF$ , fzfb=1/(2 $\times$  7 $\times$ 470 $pF$ ×47 $k\Omega$ )=7.2 $kHz$

#### < Minimum V<sub>OUT</sub> >

The Minimum V<sub>OUT</sub> is set by MINDUTY. The MINDUTY changes by the external inductance(L).

For the L value, please choose the optimal value – see P.7 < Coil current setting>. The Minimum  $V_{OUT}$  can be calculated by using the following equation:

$V_{OUT} = V_{IN} \times MINDUTY / 100$

#### [L vs. MINDUTY]

| L [ <i>µ</i> H] | MINDUTY [%] |

|-----------------|-------------|

| 2.2             | 18          |

| 3.3             | 20          |

| 4.7             | 21          |

| 6.8             | 21          |

| 10              | 22          |

#### <External soft-start setting>

A capacitor can be connected to the SS pin to set a time longer than the internal soft-start time voluntarily.

By setting the EN pin to the  $V_{ENH}$  voltage or higher, a current  $I_{SS}=4 \,\mu$ A (TYP.) flows to the SS pin and charges the capacitor. When the SS pin voltage attains the SS threshold voltage  $V_{SSTH}=1.8V$  (TYP.), the output voltage reaches about 90% of the set voltage. External soft-start can be calculated by using the following equation:

External soft-start time=V<sub>SSTH</sub> × C<sub>SS</sub> / I<sub>SS</sub>

### [Examples]

$C_{SS}=0.1 \mu F$ , External soft-start time=1.8V × 0.1  $\mu F$  / 4  $\mu A$  × 1000=45ms

### **■**OPERATIONAL EXPLANATION

The XC9248 series consists of a reference voltage source, an internal reference voltage source, ramp wave circuit, error amplifier, PWM comparator, phase compensation circuit, Nch MOS driver transistor, current limiter circuit, UVLO, short protection circuit, thermal shutdown circuit, over voltage protection and others. (See the block diagram below.)

By using the error amplifier, the FB pin voltage is compared with the internal reference voltage. The signal is input into the PWM comparator to determine the on time of switching. The signal from the error amplifier is compared with the ramp wave from the ramp wave circuit, and the resulting output is delivered to the output buffer circuit to provide on-time of the duty cycle at the LX pin. This process is continuously performed to ensure stable output voltage.

The current feedback circuit monitors the Nch MOS driver transistor current for each switching operation, and modulates the error amplifier output signal to provide multiple feedback signals. This enables a stable feedback loop even when using a low ESR capacitor such as ceramic, which results in ensuring stable output voltage.

### <Reference Voltage Source>

The reference voltage source provides the reference voltage to ensure stable output voltage of the DC/DC converter.

### <Ramp Wave Circuit>

The ramp wave circuit determines switching frequency. The frequency is fixed 500kHz internally. Clock pulses generated in this circuit are used to produce ramp waveforms needed for PWM operation, and to synchronize all the internal circuits.

#### <Error Amplifier>

The error amplifier is designed to monitor output voltage. The amplifier compares the reference voltage with the feedback voltage. When a voltage lower than the reference voltage is fed back, the output voltage of the error amplifier increases. The gain and frequency characteristics of the error amplifier output are fixed internally to deliver an optimized signal to the mixer. The error amplifier output signal optimized in the mixer is modulated with the current feedback signal. This signal is delivered to the PWM comparator.

# ■OPERATIONAL EXPLANATION (Continued)

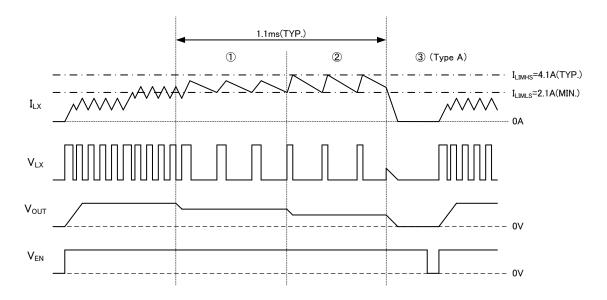

#### <Current limiting>

The current limiting circuit of the XC9248 series monitors the current that flows through the Low side and High side Nch MOS driver Tr, and when over-current is detected, the current limiting function activates.

#### Low side driver current limiting

The current in the Low side driver Tr. is detected to equivalently monitor the bottom value of the coil current.

The Low side driver current limiting function prohibits the High side driver Tr. from turning on in an over-current state where the bottom value of the coil current is higher than the Low side driver current limit value ILIMLS.

Control to lower the switching frequency fosc is also performed. When the over-current state is released, normal operation resumes.

#### 2 High side driver current limiting + Low side driver current limiting

The current in the High side driver Tr. is detected to equivalently monitor the peak value of the coil current.

The High side driver current limiting function forcibly turns off the High side driver Tr. when the peak value of the coil current reaches the High side driver current limit value  $I_{LIMHS}$ .  $I_{LIMHS}$  is set inside the IC, and therefore the Low side driver current limiting function of ① above also detects the over-current state at this time. When the over-current state is released, normal operation resumes.

#### 3 Over-current latch (Type A)

Type A turns off the High side and Low side driver transistors when state 1 or 2 continues for 1.1 ms (TYP.). The L<sub>X</sub> pin is in the C<sub>L</sub> discharged state, and is latch-stopped at the GND level (0V).

The latch-stopped state only stops the pulse output from the  $L_x$  pin; the internal circuitry of the IC continues to operate.

To restart after latch-stopping, L level and then H level must be input into the EN pin, or  $V_{IN}$  pin re-input must be performed (after lowering the voltage below the UVLO detection voltage) to resume operation by soft start.

The over-current latch function may occasionally be released from the current limit detection state by the effects of ambient noise, and it may also happen that the latch time becomes longer or latching does not take place due to board conditions. For this reason, place the input capacitor as close as possible to the IC.

Type B is an automatic recovery type that performs the operation of ① or ② until the over-current state is released.

Low side driver current limit value  $I_{LIMLS}$ =2.1A (MIN.) High side driver current limit value  $I_{LIMHS}$ =4.1A (TYP.)

# ■ OPERATIONAL EXPLANATION (Continued)

#### <Thermal Shutdown>

For protection against heat damage of the ICs, thermal shutdown function monitors chip temperature. The thermal shutdown circuit starts operating and the Nch MOS driver transistor will be turned off when the chip's temperature reaches 150°C. The Lx pin enters the  $C_L$  discharged state and stops functioning at GND level (0V). When the temperature drops to 125°C or less after shutting of the current flow, the IC performs the soft-start function to initiate output startup operation.

#### <UVLO Circuit>

When the  $V_{IN}$  voltage becomes 3.8V (TYP.) or lower, the Nch MOS driver transistor is forced OFF. The Lx pin enters the C<sub>L</sub> discharged state and stops functioning at GND level (0V). When the  $V_{IN}$  voltage becomes 3.9V (TYP.) or higher, switching operation takes place. By releasing the UVLO function, the IC performs the soft-start function to initiate output startup operation. The soft-start function operates even when the  $V_{IN}$  voltage falls momentarily below the UVLO detect voltage. The UVLO circuit does not cause a complete shutdown of the IC, but causes pulse output to be suspended; therefore, the internal circuitry remains in operation.

#### <Bootstrap method>

An Nch MOS driver Tr. is used for the High side driver, and a voltage higher than the  $V_{IN}$  voltage is needed to turn the driver on. For that purpose, the bootstrap method is used to generate a voltage higher than the  $V_{IN}$  voltage. The  $C_{BST}$  capacitance is connected between BST and LX, and because the  $V_{LX}$  voltage is lower than the 4.6V (TYP.)  $V_L$  voltage that is the internal power supply,  $C_{BST}$  is charged from  $V_L$ .

#### <Vout short-circuit protection>

With the A type, when the output voltage  $V_{OUT}$  is shorted to GND or is near a shorted state (the FB voltage is 1/2 or lower), and a current over the current limit flows to the High side or Low side driver Tr., a  $V_{OUT}$  short circuit is detected and the High side and Low side driver Trs. are immediately turned off and latched. The  $L_X$  pin enters the  $C_L$  discharged state and stops functioning at GND level (0V). Once in the latched state, operation is resumed by either turning the IC off and restarting with the EN pin, or by re-input into the  $V_{IN}$  pin (the voltage is lowered below the under-voltage lockout detection voltage once).

#### <Lx short-circuit protection>

If the event that the  $L_X$  pin shorts to GND,  $L_X$  short-circuit protection activates for protection from over-current due to rush current and to protect the IC.

If the  $L_X$  pin shorts to GND, High side current limiting will activate due to rush current when the High side driver Tr. turns on. The High side driver Tr. turn offs, and the Low side driver Tr. turns on at the same time. At this time, if Low side current limiting did not activate, an  $L_X$  short-circuit is detected, and the Low side driver is turned off and latched at the same time as the High side driver Tr. Once in the latched state, operation is resumed by either turning the IC off and restarting with the EN pin, or by re-input into the  $V_{IN}$  pin (the voltage is lowered below the under-voltage lockout detection voltage once).

#### <Vour over-voltage protection>

To minimize output voltage overshoot,  $V_{\text{OUT}}$  over-voltage protection activates when  $V_{\text{OUT}}$  overshoot occurs due to the output resistance changing from a heavy load to a light load or otherwise. When  $V_{\text{OUT}}$  overshoot occurs and the FB voltage that senses  $V_{\text{OUT}}$  rises to 0.9V (TYP.) or more, the High side driver Tr. is immediately turned off and the Low side driver Tr. is turned on to prevent  $V_{\text{OUT}}$  overshoot. When the FB voltage falls to 0.8V (TYP.) or less due to hysteresis, the High side driver Tr. turns on at the next clock cycle.

# ■OPERATIONAL EXPLANATION (Continued)

#### <CL high-speed discharge function>

When L level is input into the EN pin and the IC enters the standby state, the charge on the output capacitor  $C_L$  can be discharged at high speed with the Nch MOS switch Tr. incorporated between  $L_X$  and GND. This enables the prevention of application malfunctioning due to  $C_L$  charge remaining when the IC stops.

The  $C_L$  discharge time can be calculated from the equation below. Note that the equation varies depending on the set voltage  $V_{\text{OUT(E)}}$ .

#### (1) Equation when the set voltage V<sub>OUT(E)</sub> is 1V to 4V.

The  $C_L$  discharge time is determined by  $C_L$  and  $R_{DCHG}$ . If the time constant of  $C_L$  and  $R_{DCHG}$  is  $\mathcal{I}$   $\not \subset C_L \times R_{DCHG}$ ), the output voltage discharge time can be calculated by using the following equation:

$$V = V_{OUT(E)} \times e - t / \tau_{or} t = t \ln (V_{OUT(E)} / V)$$

V : Output voltage after discharge

V<sub>OUT(E)</sub>: Output voltage t: Discharge time

τ CL×RDCHG

#### (2) Equation when the set voltage V<sub>OUT(E)</sub> is 4.1V to 12V.

The  $C_L$  discharge time is determined by constant current until  $V_{OUT(E)}$  is 4 V. When 4V or less, it is determined by  $C_L$  and  $R_{DCHG}$  as in (1). If  $T_C \subset C_L \times R_{DCHG}$  is the time constant of  $C_L$  and  $R_{DCHG}$  and the  $C_L$  discharge current is  $I_{DCHG}$ , the discharge time of the output voltage can be calculated by using the following equation:

$$t = t n (4/V) + C_L \times (V_{OUT(E)} - 4) / I_{DCHG}$$

V : Output voltage after discharge

V<sub>OUT(E)</sub>: Output voltage,

t: Discharge time

$\tau$   $C_L \times R_{DCHG}$

I<sub>DCHG</sub>: C<sub>L</sub>: Discharge time

### ■NOTE ON USE

- 1. For temporary, transitional voltage drop or voltage rising phenomenon, the IC is liable to malfunction should the ratings be exceeded.

- 2. The DC/DC converter characteristics depend greatly on the externally connected components as well as on the characteristics of this IC, so refer to the specifications and typical standard circuit examples of each component when carefully considering which components to select. Be especially careful of the capacitor characteristics and use B characteristics (JIS standard) or X7R, X5R (EIA standard) ceramic capacitors.

- 3. Where wiring impedance is high, operations may become unstable due to noise and/or phase lag depending on output current.

- Please wire the input capacitor (C<sub>IN</sub>) and the output capacitor (C<sub>L</sub>) as close to the IC as possible.

- 4. This IC monitors Peak to Peak current in the coil by means of a Low side driver current limiting circuit and a High side driver current limiting circuit. The Peak to Peak current varies depending on the difference between the input voltage and the output voltage as well as the L value of the coil and thus, in some cases, current limiting may activate too frequently and cause operation to become unstable or the current may not reach the maximum output current.

- 5. With the A type, when a sharp load fluctuation occurs, the V<sub>OUT</sub> voltage drop is conveyed directly to the FB pin through C<sub>FB</sub>, and short-circuit protection may activate at a voltage higher than 1/2 the V<sub>OUT</sub> voltage.

- 6. The V<sub>L</sub> pin is the output of the internal regulator for operation of the DC/DC control block. For stable operation, always connect an external capacitor C<sub>VL</sub> to the V<sub>L</sub> pin. Do not use the V<sub>L</sub> pin for external power supply, as it has been optimized as a local power supply.

- 7. With this IC, operation may become unstable at the minimum operating voltage or less.

- 8. Make sure that the absolute maximum ratings of the external components and of this IC are not exceeded.

- Torex places an importance on improving our products and their reliability.

We request that users incorporate fail-safe designs and post-aging protection treatment when using Torex products in their systems.

# ■NOTE ON USE (Continued)

#### 10. Instructions for pattern layouts

- (1) In order to stabilize V<sub>IN</sub> voltage level, we recommend that a by-pass capacitor (C<sub>IN</sub>) be connected as close as possible to the V<sub>IN</sub> and GND pins.

- (2) Please mount each external component as close to the IC as possible.

- (3) Wire external components as close to the IC as possible and use thick, short connecting traces to reduce the circuit impedance.

- (4) Make sure that the GND traces are as thick as possible, as variations in ground potential caused by high ground currents at the time of switching may result in instability of the IC.

- (5) Internal driver transistors bring on heat because of the output current (IouT) and ON resistance of the Nch MOS driver transistors.

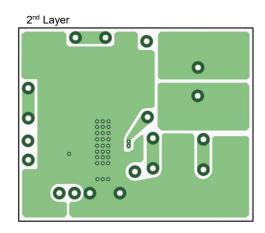

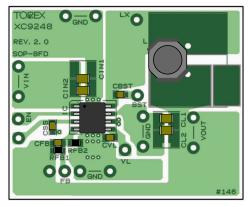

#### <Reference Pattern Layout>

1st Layer

#### PCB mounted

# **■**TYPICAL PERFORMANCE CHARACTERISTICS

(1) Efficiency vs. Output current

$XC9248(V_{IN}=12V, V_{OUT}=3.3V)$

$XC9248(V_{IN}=12V, V_{OUT}=5V)$

$XC9248(V_{IN}=9V, V_{OUT}=4V)$

$XC9248(V_{IN}=5V, V_{OUT}=1V)$

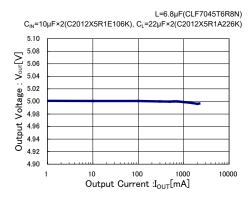

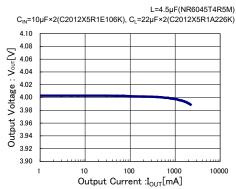

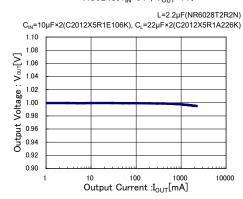

(2) Output Voltage vs. Output Currnt

$XC9248(V_{IN}=12V , V_{OUT}=3.3V)$

$XC9248(V_{IN}=12V, V_{OUT}=5V)$

$XC9248(V_{IN}=9V, V_{OUT}=4V)$

$XC9248(V_{IN}=5V, V_{OUT}=1V)$

# ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

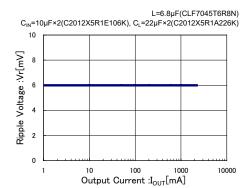

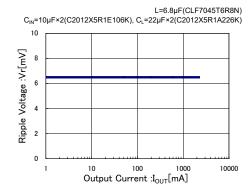

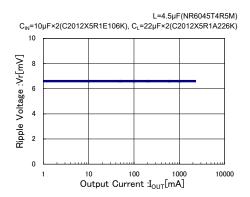

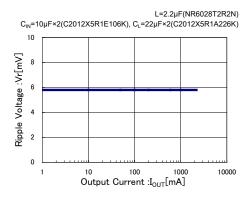

(3) Ripple Voltage vs. Output Current

$XC9248(V_{IN}=12V, V_{OUT}=3.3V)$

$XC9248(V_{IN}=12V, V_{OUT}=5V)$

XC9248(VIN=9V, VOUT=4V)

XC9248(VIN=5V, VOUT=1V)

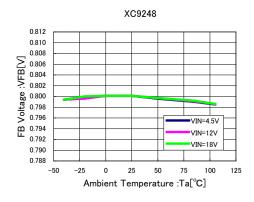

(4) FB Voltage vs. Ambient Temperature

(5) UVLO Voltage vs. Ambient Temperature

(6) Oscillation Frequency vs. Ambient Temperature

(7) Supply Current vs. Ambient Temperature

# ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

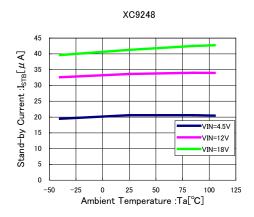

(8) Stand-by Current vs. Ambient Temperature

(10) Lx "L" Current vs. Ambient Temperature

(11) EN "H" Current vs. Ambient Temperature

(12) EN "H" Voltage vs. Ambient Temperature

(13) EN "L" Voltage vs. Ambient Temperature

(14) Internal Soft-Start Time vs. Ambient Temperature

(15) SS Terminal Current vs. Ambient Temperature

# ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

(16) SS Threshold Voltage vs. Ambient Temperature

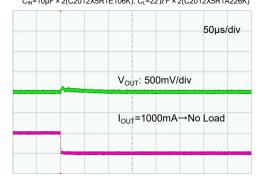

#### (17) Load Transient Response

Ambient Temperature :Ta[°C]

#### XC9248

$m V_{IN}\!\!=\!12V,~V_{OUT}\!\!=\!3.3V,~I_{OUT}\!\!=\!1000mA\!\!\longrightarrow\!\!No~Load$   $\rm L=6.8\mu F(CLF7045T6R8N)$

$L = 6.8 \mu F (CLF7045T6R8N)$   $C_{\text{IN}} = 10 \mu F \times 2 (C2012X5R1E106K), \ C_{\text{L}} = 22 \ \mu \ F \times 2 (C2012X5R1A226K)$

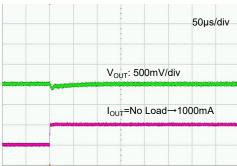

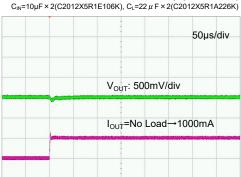

#### XC9248

$V_{IN}$ =9V,  $V_{OUT}$ =4V,  $I_{OUT}$ =No Load $\rightarrow$ 1000mA

$L=4.5\mu F(NR6045T4R5M)$   $C_{IN}=10\mu F\times 2(C2012X5R1E106K),\ C_{L}=22\ \mu F\times 2(C2012X5R1A226K)$

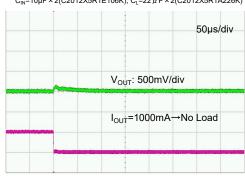

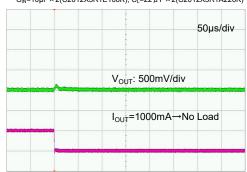

XC9248

$V_{IN}$ =9V,  $V_{OUT}$ =4V,  $I_{OUT}$ =1000mA $\rightarrow$ No Load

L=4.5μF(NR6045T4R5M) C<sub>IN</sub>=10μF×2(C2012X5R1E106K), C<sub>L</sub>=22μF×2(C2012X5R1A226K)

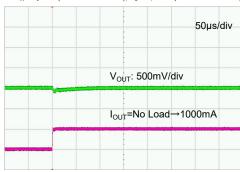

### XC9248

$V_{IN}$ =5V,  $V_{OUT}$ =1V,  $I_{OUT}$ =No Load $\rightarrow$ 1000mA

#### XC9248

$V_{IN}$ =5V,  $V_{OUT}$ =1V,  $I_{OUT}$ =1000mAightarrowNo Load

# **■**PACKAGING INFORMATION

For the latest package information go to, <a href="www.torexsemi.com/technical-support/packages">www.torexsemi.com/technical-support/packages</a>

| PACKAGE | OUTLINE / LAND PATTERN | THERMAL CHARACTERISTICS |                           |  |

|---------|------------------------|-------------------------|---------------------------|--|

| 000 000 | COD OFF BYO            | Standard Board          | OOD OED Dawn Disain ation |  |

| SOP-8FD | SOP-8FD PKG            | JESD51-7 Board          | SOP-8FD Power Dissipation |  |

# ■ MARKING RULE

### SOP-8FD

### ① represents products series

| MARK | PRODUCT SERIES |  |

|------|----------------|--|

| В    | XC9248*****-G  |  |

### 2 represents products type

| MARK | PRODUCT SERIES |  |

|------|----------------|--|

| Α    | XC9248A****-G  |  |

| В    | XC9248B****-G  |  |

### 3 represents FB voltage and oscillation frequency

|   | MARK | VOLTAGE (V) | OSCILLATION FREQUENCY | PRODUCT SERIES |

|---|------|-------------|-----------------------|----------------|

| Ī | 5    | 0.8         | 500kHz                | XC9248*085**-G |

④⑤ represents production lot number 01~09, 0A~0Z, 11~9Z, A1~A9, AA~AZ, B1~ZZ in order. (G, I, J, O, Q, W excluded)

<sup>\*</sup> No character inversion used.

- 1. The product and product specifications contained herein are subject to change without notice to improve performance characteristics. Consult us, or our representatives before use, to confirm that the information in this datasheet is up to date.

- 2. The information in this datasheet is intended to illustrate the operation and characteristics of our products. We neither make warranties or representations with respect to the accuracy or completeness of the information contained in this datasheet nor grant any license to any intellectual property rights of ours or any third party concerning with the information in this datasheet.

- Applicable export control laws and regulations should be complied and the procedures required by such laws and regulations should also be followed, when the product or any information contained in this datasheet is exported.

- 4. The product is neither intended nor warranted for use in equipment of systems which require extremely high levels of quality and/or reliability and/or a malfunction or failure which may cause loss of human life, bodily injury, serious property damage including but not limited to devices or equipment used in 1) nuclear facilities, 2) aerospace industry, 3) medical facilities, 4) automobile industry and other transportation industry and 5) safety devices and safety equipment to control combustions and explosions. Do not use the product for the above use unless agreed by us in writing in advance.

- 5. Although we make continuous efforts to improve the quality and reliability of our products; nevertheless Semiconductors are likely to fail with a certain probability. So in order to prevent personal injury and/or property damage resulting from such failure, customers are required to incorporate adequate safety measures in their designs, such as system fail safes, redundancy and fire prevention features.

- 6. Our products are not designed to be Radiation-resistant.

- 7. Please use the product listed in this datasheet within the specified ranges.

- 8. We assume no responsibility for damage or loss due to abnormal use.

- 9. All rights reserved. No part of this datasheet may be copied or reproduced unless agreed by Torex Semiconductor Ltd in writing in advance.

TOREX SEMICONDUCTOR LTD.