# Microprocessor Reset Circuits with Short Delay Time

### **Description**

The FP6808 is a cost-effective system supervisor circuit designed to monitor microprocessor voltage and  $V_{\text{DD}}$  in digital systems. This device provides a reset signal to the host processor when necessary.

The circuit asserts a reset signal whenever the  $V_{DD}$  supply voltage declines below a preset threshold. It keeps reset signal asserted for at least 20ms after  $V_{DD}$  has risen above the reset threshold.

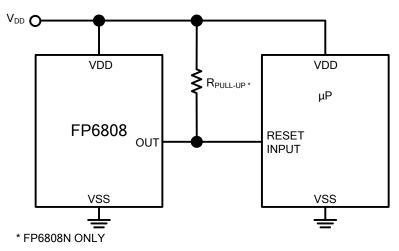

The FP6808-N has an open-drain active-low output stage, while FP6808-C has a push-pull active-low output. The FP6808-N's open-drain output requires a pull-up resistor.

The FP6808 is optimized to reject fast transient glitches on the  $V_{\text{DD}}$  line. Low supply current makes this device suitable for portable equipment.

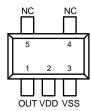

# **Pin Assignments**

S5 Package (SOT-23-5)

Figure 1. Pin Assignment of FP6808

#### SOT-23-5 Marking

| Part Number   | Product<br>Code | Part Number   |    |

|---------------|-----------------|---------------|----|

| FP6808-23NS5P | Ca              | FP6808-23CS5P | Ck |

| FP6808-26NS5P | Cb              | FP6808-26CS5P | Cm |

| FP6808-29NS5P | Cd              | FP6808-29CS5P | Cn |

| FP6808-31NS5P | Се              | FP6808-31CS5P | Cr |

| FP6808-40NS5P | Cf              | FP6808-40CS5P | Cs |

| FP6808-44NS5P | Ch              | FP6808-44CS5P | Ct |

| FP6808-46NS5P | Ci              | FP6808-46CS5P | Cu |

### **Features**

- Precision V<sub>DD</sub> Monitor for 2.5V, 3.0V, 3.3V and 5.0V Supplies

- Precision Monitoring Voltages from 1.6V to 5.0V Available in 100mV Steps

- 20ms Guaranteed Minimum Reset Output Duration

- Low Supply Current

- ±2% High Precision Detection Voltage

- V<sub>DD</sub> Transient Immunity

- No External Components

- Guaranteed Reset Valid to V<sub>DD</sub>=1V

- Available in Two Output Configurations

- Open-Drain Output (FP6808-N)

- Push-Pull Output (FP6808-C)

- RoHS Compliant

- Small SOT-23-5 Package

## **Applications**

- Computer

- Battery Powered Equipment

- Microprocessor Power Supply Monitoring

- Controller

- Embedded System

- Automotive

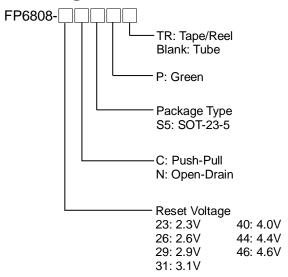

## **Ordering Information**

FP6808-1.3-DEC-2012

# **Typical Application Circuit**

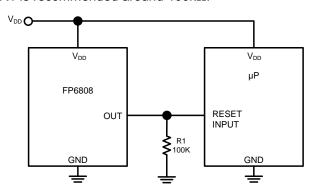

Figure 2. Typical Application Circuit of FP6808

# **Functional Pin Description**

| Pin Name         | Pin Function                 |  |  |  |

|------------------|------------------------------|--|--|--|

| оит              | oltage Detection Output Pin. |  |  |  |

| VDD              | /oltage Input Pin.           |  |  |  |

| vss              | GND Pin.                     |  |  |  |

| NC <sup>*1</sup> | No Connection.               |  |  |  |

Note: \*1. The NC pin is electrically open. The NC pin can be connected to VDD or VSS

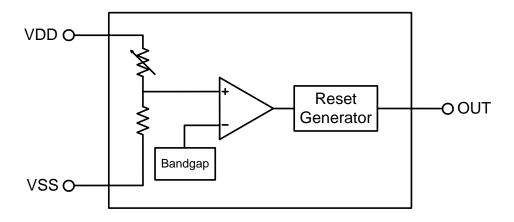

# **Block Diagram**

Figure 3. Block Diagram of FP6808

# **Absolute Maximum Ratings**

| • Supply Voltage (V <sub>DD</sub> to V <sub>SS</sub> )                                      | 0.3V to +6V                      |

|---------------------------------------------------------------------------------------------|----------------------------------|

| Output Voltage (Push-Pull)                                                                  | -0.3 to $(V_{DD}+0.3V)$          |

| Output Voltage (Open Drain)                                                                 | -0.3V to (V <sub>DD</sub> +0.3V) |

| • Input Current (V <sub>DD</sub> )                                                          | - 20mA                           |

| Output Current (I <sub>OUT</sub> )                                                          | 20mA                             |

| • Rate of Rise (V <sub>DD</sub> )                                                           | - 100V/µs                        |

| <ul> <li>Power Dissipation, P<sub>D</sub> @T<sub>A</sub>=25°C</li> </ul>                    |                                  |

| SOT-23-5                                                                                    | +400mW                           |

| Operating Temperature Range (T <sub>A</sub> )                                               | 40°C to +105°C                   |

| Storage Temperature (T <sub>S</sub> )                                                       | 65°C to +150°C                   |

| • Lead Temperature (Soldering, 10s)                                                         | - +300°C                         |

| Note: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent dam | nage to the device.              |

| Recommended Operating Conditions                                                            |                                  |

| •Supply Voltage (V <sub>DD</sub> to V <sub>SS</sub> )                                       | - +1.0V to +5.5V                 |

| Operation Temperature Range                                                                 | -40°C to +85°C                   |

# **Electrical Characteristics**

( $V_{DD}$  =full range,  $T_A$ =25°C, unless otherwise specified.)

| Parameter                                                 | Symbol          | Conditions                                                                            | Min                  | Тур. | Max  | Unit       |  |

|-----------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------|----------------------|------|------|------------|--|

| V <sub>DD</sub> Range                                     | V <sub>DD</sub> | 1.0                                                                                   |                      |      | 5.5  | μA         |  |

|                                                           | I <sub>DD</sub> | V <sub>DD</sub> <5.5V, FP6808-46/44/40                                                |                      | 3    |      |            |  |

| Supply Current                                            |                 | V <sub>DD</sub> <3.6V, FP6808-23/26/29/31                                             |                      | 3    |      | μA         |  |

|                                                           |                 | FP6808-46                                                                             | 4.54                 | 4.63 | 4.72 |            |  |

| December 1                                                | .,              | FP6808-44                                                                             | 4.29                 | 4.38 | 4.47 |            |  |

| Reset Threshold                                           | V <sub>TH</sub> | FP6808-40                                                                             | 3.92                 | 4.00 | 4.08 | V          |  |

|                                                           |                 | FP6808-31                                                                             | 3.02                 | 3.08 | 3.14 | 1          |  |

| Reset Threshold                                           | V <sub>TH</sub> | FP6808-29                                                                             | 2.87                 | 2.93 | 2.99 | V          |  |

|                                                           |                 | FP6808-26                                                                             | 2.58                 | 2.63 | 2.68 |            |  |

|                                                           |                 | FP6808-23                                                                             | 2.27                 | 2.32 | 2.37 | -<br> <br> |  |

| Reset Threshold Tempco                                    |                 |                                                                                       |                      | 30   |      | ppm/°C     |  |

| V <sub>DD</sub> to Reset Delay                            |                 | $V_{DD} = V_{TH}$ to (Vth-100mV)                                                      |                      | 20   |      | μs         |  |

| Reset Active Timeout<br>Period                            |                 |                                                                                       | 20                   | 40   | 60   | ms         |  |

|                                                           |                 | V <sub>DD</sub> =V <sub>TH</sub> min, I <sub>SINK</sub> =1.2mA,<br>FP6808-23/26/29/31 |                      |      | 0.3  |            |  |

| Output Voltage Low<br>(Push-Pull and<br>Open-Drain)       | V <sub>OL</sub> | $V_{DD} = V_{TH} \text{ min, } I_{SINK} = 3.2 \text{mA,}$<br>FP6808-44/46             |                      |      | 0.4  | V          |  |

|                                                           |                 | V <sub>DD</sub> >1.0V, I <sub>SINK</sub> =50μA                                        |                      |      | 0.3  |            |  |

| Output Voltage High (push-pull)                           | V <sub>OH</sub> | $V_{DD} > V_{TH}$ max, $I_{SOURCE}$ =500 $\mu$ A, FP6808-23/26/29/31                  |                      |      |      |            |  |

|                                                           |                 | V <sub>DD</sub> > V <sub>TH</sub> max, I <sub>SOURCE</sub> =800μA,<br>FP6808-44/46    | V <sub>DD</sub> -1.5 |      |      |            |  |

| Output Open-Drain<br>Output Leakage Current<br>(FP6808-N) |                 | V <sub>DD</sub> > V <sub>TH</sub> , RESET deasserted                                  |                      |      |      | μА         |  |

# **Typical Performance Curves**

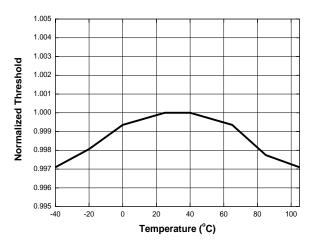

Figure 4. Normalized Reset Threshold vs. Temperature

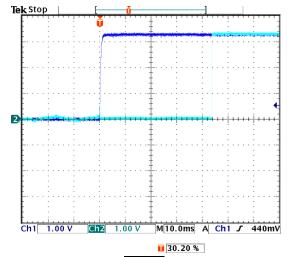

Figure 6. Power-Up RESET Timeout Waveforms; Ch1: VDD Ch2: OUT

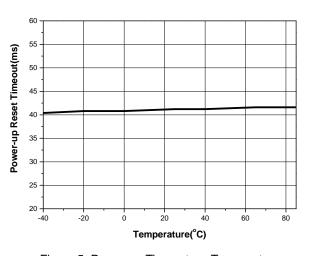

Figure 5. Power-up Timeout vs. Temperature

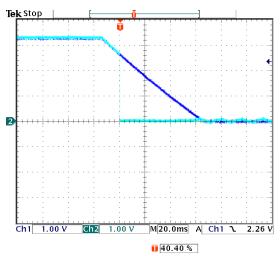

Figure 7. Power-Down RESET Delay Waveforms; Ch1: VDD Ch2: OUT

## **Typical Performance Curves (Continued)**

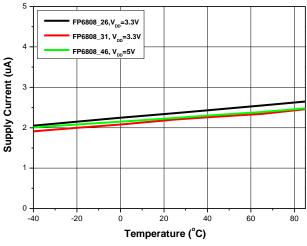

Figure 8. Supply Current vs. Temperature

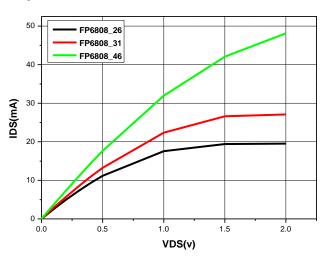

Figure 10. Output Sourcing Capability

Figure 9. Output Sinking Capability

## **Functional Description**

FP6808 is supervisory circuit, monitoring critical voltages and asserting reset signal to the subsequent devices. The reset signal can start the microprocessor in a known state, avoiding code-execution errors during power-up, power-down or brownout conditions. OUT is guaranteed to be a logic low for  $V_{TH} > V_{CC} > 0.9 V$ . Once  $V_{CC}$  exceeds the reset threshold, an internal timer will keep OUT low for the reset timeout. After this period, OUT will go high. If  $V_{CC}$  falls below the reset threshold, OUT will go low immediately.

Whenever  $V_{CC}$  drops below  $V_{TH}$ , the internal timer will reset to zero and OUT will go low. The internal timer will keep activated only when  $V_{CC} > V_{TH}$ , and OUT remains low for the reset timeout interval.

FP6808-1.3-DEC-2012

### **Application Information**

#### **Benefits of Highly Accurate Reset Threshold**

Most microprocessor supervisor ICs has reset threshold voltages between 5% and 10% below the value of nominal supply voltages. This ensures a reset will not occur within 5% of the nominal supply, but will occur when supply is 10% below nominal. In other words, the reset is guaranteed to assert after the power supply falls out of regulation, but keeps inactive even when power is at the minimum specified operating voltage of the system ICs.

### **Negative-Going V<sub>DD</sub> Transients**

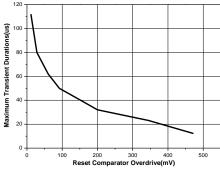

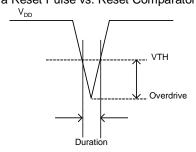

In addition to issuing a reset to microprocessor during power-up, power-down and brownout conditions, FP6808 is relatively immune to short-duration negative-going V<sub>CC</sub> transients (glitches). Figure 11 shows typical transient duration vs. reset comparator overdrive, for which the FP6808 does not generate a reset signal. The graph was generated by using a negative-going pulse applied to V<sub>DD</sub>, as shown in Figure 12, starting 0.5V above the actual reset threshold and ending below it by the magnitude indicated (reset comparator over-drive). The graph indicates that the maximum pulse width negative-going V<sub>DD</sub> transient can have without causing a reset signal. As the reset comparator overdrive increases, the maximum allowable pulse width decreases. A typical 0.1µF bypass capacitor mounted as close to the V<sub>DD</sub> pin as possible provides additional transient immunity.

Figure 11. Maximum Transient Durations Without Causing a Reset Pulse vs. Reset Comparator Overdrive

Figure 12. The  $V_{\text{DD}}$  with Negative Going Transients

#### Ensuring a Valid Reset Output Down to V<sub>DD</sub>=0

When  $V_{DD}$  falls below 1V, the FP6808 no longer sinks current, it will become an open circuit. Therefore, high-impedance CMOS logic inputs connected to OUT can drift to undetermined voltages. This presents no problem in most applications for microprocessor's inoperative condition with  $V_{DD}$  below 1V. However, in applications where OUT must be valid down to 0V, adding a pull-down resistor to OUT causes stray leakage currents to flow to ground, providing some impedance between OUT and ground (Figure 13). R1 is recommended around  $100k\Omega$ .

Figure 13. OUT Valid to V<sub>DD</sub>=Ground Circuit

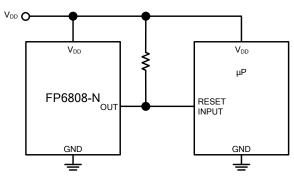

### Interfacing to µPs with Bidirectional Reset Pins

Since the output of FP6808N is open drain, this device interfaces easily with microprocessor that has bidirectional reset pins. Connecting the FP6808N's output directly to the micro-controller's RESET pin with a single pull-up resistor allows either device to assert reset (Figure 14).

Figure 14. Interfacing to µPs with Bidirectional Reset I/O

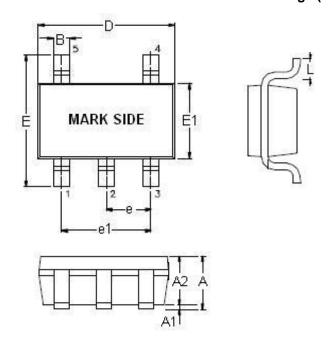

# **Outline Information**

### SOT-23-5 Package (Unit: mm)

| SYMBOLS      | DIMENSION IN MILLIMETER |      |  |  |

|--------------|-------------------------|------|--|--|

| UNIT         | MIN                     | MAX  |  |  |

| Α            | 0.90                    | 1.45 |  |  |

| A1           | 0.00                    | 0.15 |  |  |

| A2<br>B<br>D | 0.90                    | 1.30 |  |  |

|              | 0.30                    | 0.50 |  |  |

|              | 2.80                    | 3.00 |  |  |

|              | 2.60                    | 3.00 |  |  |

| E1           | 1.50                    | 1.70 |  |  |

| е            | 0.90                    | 1.00 |  |  |

| e1           | 1.80                    | 2.00 |  |  |

| Ĺ            | 0.30                    | 0.60 |  |  |

Note: Followed From JEDEC MO-178-C.

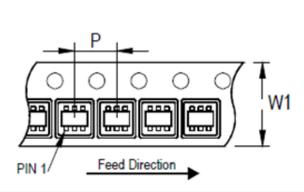

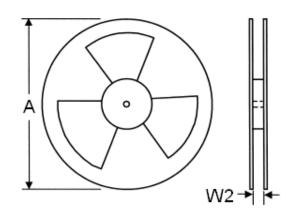

## **Carrier Dimensions**

| Tape Size | Pocket Pitch | Reel Size (A) |     | Reel Width | Empty Cavity | Units per Reel |

|-----------|--------------|---------------|-----|------------|--------------|----------------|

| (W1) mm   | (P) mm       | in            | mm  | (W2) mm    | Length mm    |                |

| 8         | 4            | 7             | 180 | 8.4        | 300~1000     | 3,000          |

FP6808-1.3-DEC-2012