# FM8PE51

# EPROM/ROM-Based 8-Bit Microcontroller

#### **Devices Included in this Data Sheet:**

FM8PE51E : EPROM deviceFM8PE51 : Mask ROM device

#### **FEATURES**

- Only 47 single word instructions

- · All instructions are single cycle except for program branches which are two-cycle

- 13-bit wide instructions

- · 8-bit wide data path

- 5-level deep hardware stack

- 4K x 13 bits on chip EPROM/ROM

- 140 x 8 bits on chip general purpose registers (SRAM)

- · Operating speed: DC-20 MHz clock input

DC-100 ns instruction cycle

- · Direct, indirect addressing modes for data accessing

- · One 8-bit real time clock/counter (Timer0) with 8-bit programmable prescaler

- Three 8-bit real time clock/counter (Timer1, Timer2, and Timer3) with period setting

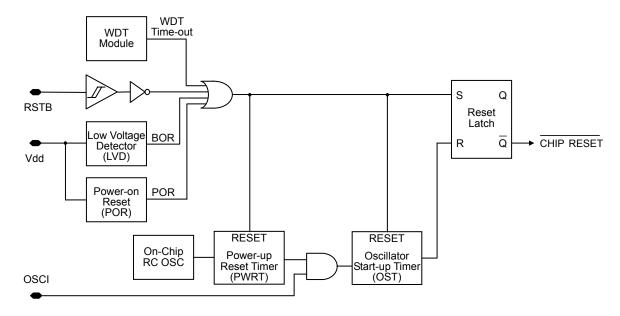

- Internal Power-on Reset (POR)

- Built-in Low Voltage Detector (LVD) for Brown-out Reset (BOR)

- Power-up Reset Timer (PWRT) and Oscillator Start-up Timer(OST)

- On chip Watchdog Timer (WDT) with internal oscillator for reliable operation and soft-ware watch-dog enable/disable control

- Five I/O ports (38 I/O pins) with independent direction control

- 32 programmable pull-high input pins

- 12 wake-up pins

- · 2 open-drain pins

- 2 R-option pins

- · Clock output with high driving ability

- 19 channels of 15-bit resolution Resistor to Frequency Converter (RFC) output

- 2 channels of maximum 10-bit resolution Pulse Width Modulation (PWM) output

- · Built-in 8-bit data comparator

- Seven internal interrupt source: Timer0 overflow, Timer1 match, Timer2 match, Timer3 match, SPI module (Receive & Transmit), RFC module; One external interrupt source: INT pin change

- · Wake-up from SLEEP by port input change

- · Power saving SLEEP mode

- Programmable Code Protection

- · Built-in RC oscillator with external resistor

- · Selectable oscillator options:

- ERC: External Resistor/Capacitor Oscillator

- ERIC: External Resistor/Internal Capacitor Oscillator

- HF: High Frequency Crystal/Resonator Oscillator

- XT: Crystal/Resonator Oscillator

- LF: Low Frequency Crystal Oscillator

- · Wide-operating voltage range:

- EPROM : 2.3V to 5.5V

- ROM: 2.3V to 5.5V

This datasheet contains new product information. Feeling Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sales of the product.

## **GENERAL DESCRIPTION**

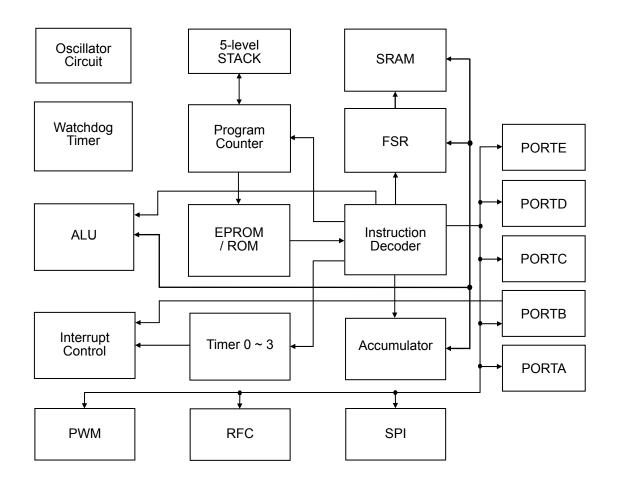

The FM8PE51 series is a family of low-cost, high speed, high noise immunity, EPROM/ROM-based 8-bit CMOS microcontrollers. It employs a RISC architecture with only 47 instructions. All instructions are single cycle except for program branches which take two cycles. The easy to use and easy to remember instruction set reduces development time significantly.

The FM8PE51 series consists of Power-on Reset (POR), Brown-out Reset (BOR), Power-up Reset Timer (PWRT), Oscillator Start-up Timer(OST), Watchdog Timer, EPROM/ROM, SRAM, tri-state I/O port, I/O pull-high/open-drain control, Power saving SLEEP mode, 4 real time programmable clock/counter, Interrupt, SPI, RFC, data compare, Wake-up from SLEEP mode, and Code Protection for EPROM products. There are three oscillator configurations to choose from, including the power-saving LP (Low Power) oscillator and cost saving RC oscillator. The FM8PE51 series address 4K×13 of program memory.

The FM8PE51 series can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory.

#### **BLOCK DIAGRAM**

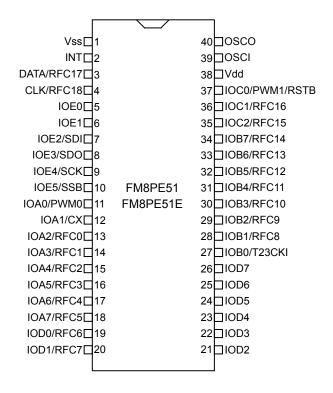

# **PIN CONNECTION**

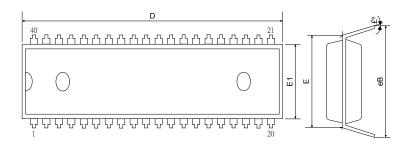

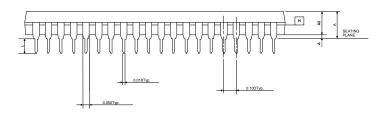

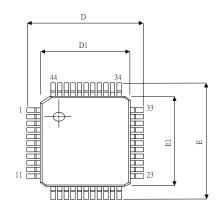

**PDIP**

# **PIN DESCRIPTIONS**

| Name         | I/O | Description                                                                                   |

|--------------|-----|-----------------------------------------------------------------------------------------------|

| IOA0 ~ IOA7  | I/O | Bi-direction I/O port                                                                         |

| IOAU ~ IOA/  | 1/0 | Software controlled pull-high for all pins                                                    |

| IOB0 ~ IOB7  | I/O | Bi-direction I/O port with system wake-up function                                            |

| 1060 ~ 1067  | 1/0 | Software controlled pull-high for all pins                                                    |

| IOC0 ~ IOC2  | I/O | Bi-direction I/O pins with driving ability selection                                          |

| IOC3         | I/O | Bi-direction I/O pin                                                                          |

|              |     | By connecting IOC4 and IOC6 together                                                          |

| CLK          | I/O | IOC4 is a bi-direction I/O pin with system wake-up and software controlled pull-high function |

| OLK          | 1/0 | IOC6 is a bi-direction I/O pin with software controlled open-drain output                     |

|              |     | Note: Both IOC4 and IOC6 should not be defined as output pins at the same time.               |

|              |     | By connecting IOC5 and IOC7 together                                                          |

| DATA         | I/O | IOC5 is a bi-direction I/O pin with system wake-up and software controlled pull-high function |

| DAIA         | 1/0 | IOC7 is a bi-direction I/O pin with software controlled open-drain output                     |

|              |     | Note: Both IOC5 and IOC7 should not be defined as output pins at the same time.               |

|              |     | Bi-direction I/O port                                                                         |

| IOD0 ~ IOD7  | I/O | Software controlled pull-high for all pins                                                    |

|              |     | IOD0 and IOD1 are R-option pins                                                               |

| IOE0 ~ IOE1  | I/O | Bi-direction I/O pins with system wake-up function                                            |

| IOEU ~ IOE I | 1/0 | Software controlled pull-high for all pins                                                    |

| IOE2 ~ IOE5  | I/O | Bi-direction I/O pins                                                                         |

| 10E2 ~ 10E3  | 1/0 | All pins can be pulled-high by software                                                       |

| IOE6 ~ IOE7  | I/O | Bi-direction I/O pins                                                                         |

| INT          | 1   | External interrupt input triggered by falling edge                                            |

| SDI          | 1   | Serial data in for SPI                                                                        |

| SDO          | 0   | Serial data out for SPI                                                                       |

| SCK          | I/O | Serial clock for SPI                                                                          |

| SSB          | _   | Slave select (active low) for SPI                                                             |

| PWM0 ~ PWM1  | 0   | PWM output pins                                                                               |

| RFC0 ~ RFC18 | 0   | The RC oscillator network output of RFC module                                                |

| CX           | ı   | The RC oscillator network input of RFC module                                                 |

| OSCI         | ı   | X'tal type: Oscillator crystal input                                                          |

| USCI         | ı   | RC type: Clock input of RC oscillator                                                         |

| osco         | 0   | X'tal type: Oscillator crystal output.                                                        |

| 0300         | )   | RC mode: Outputs with 1/4 the frequency of OSCI to denotes the instruction cycle rate         |

| CKOUT        | 0   | Oscillator frequency output with high driving ability and output phase selection              |

| RSTB         |     | System clear (RESET) input. This pin is an active low RESET to the device. Internal weak      |

| NOID         | ı   | pull-high.                                                                                    |

| Vdd          | -   | Positive supply                                                                               |

| Vss          | -   | Ground                                                                                        |

Legend: I=input, O=output, I/O=input/output

# 1.0 MEMORY ORGANIZATION

FM8PE51 series memory is organized into program memory and data memory.

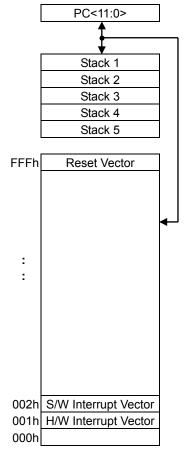

#### 1.1 Program Memory Organization

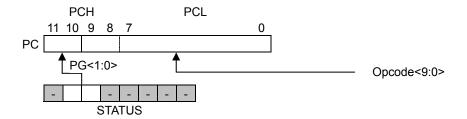

The FM8PE51 series have a 12-bit Program Counter capable of addressing a 4K×13 program memory space. The RESET vector for the FM8PE51 series is at FFFh.

The H/W interrupt vector is at 001h. And the S/W interrupt vector is at 002h.

FM8PE51 series has program memory size greater than 1K words, but the CALL and GOTO instructions only have a 10-bit address range. This 10-bit address range allows a branch within a 1K program memory page size. To allow CALL and GOTO instructions to address the entire 4K program memory address range for FM8PE51 series, there is another two bits to specify the program memory page. This paging bit comes from the PG<1:0> bits (STATUS<6:5>). When doing a CALL or GOTO instruction, the user must ensure that page bit PG<1:0> are programmed so that the desired program memory page is addressed. When one of the return instructions is executed, the entire 12-bit PC is POPed from the stack. Therefore, manipulation of the PG<1:0> is not required for the return instructions.

FIGURE 1.1: Program Memory Map and STACK

FM8PE51 Series

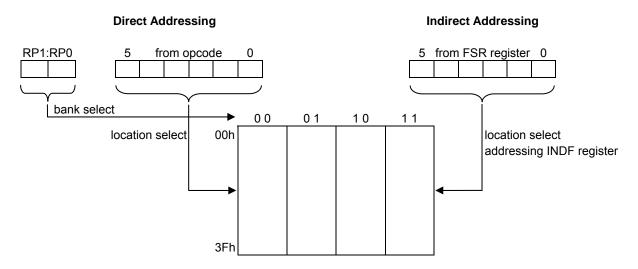

# 1.2 Data Memory Organization

Data memory is composed of Special Function Registers and General Purpose Registers.

The General Purpose Registers are accessed either directly or indirectly through the FSR register.

The Special Function Registers are registers used by the CPU and peripheral functions to control the operation of the device.

In FM8PE51 series, the data memory is partitioned into four banks. Switching between these banks requires the RP1 and RP0 bits in the FSR register to be configured for the desired bank.

TABLE 1.1: Registers File Map for FM8PE51 Series

| FSR<7:6> |           | Descr     | ription           |            |  |  |  |  |  |

|----------|-----------|-----------|-------------------|------------|--|--|--|--|--|

| Address  | 0 0       | 0 1       | 1 0               | 11         |  |  |  |  |  |

| Address  | Bank 0    | Bank 1    | Bank 2            | Bank 3     |  |  |  |  |  |

| 00h      | INDF      |           |                   |            |  |  |  |  |  |

| 01h      | TMR0      |           |                   |            |  |  |  |  |  |

| 02h      | PCL       |           |                   |            |  |  |  |  |  |

| 03h      | STATUS    |           |                   |            |  |  |  |  |  |

| 04h      | FSR       | Mamani    | book to addraga i | n Donk O   |  |  |  |  |  |

| 05h      | PORTA     | ivieniory | back to address i | II Dalik U |  |  |  |  |  |

| 06h      | PORTB     |           |                   |            |  |  |  |  |  |

| 07h      | PORTC     |           |                   |            |  |  |  |  |  |

| 08h      | PORTD     |           |                   |            |  |  |  |  |  |

| 09h      | PORTE     |           |                   |            |  |  |  |  |  |

| 0Ah      | SPIRCB    | T23CON    | PWMCON            | RFCCON     |  |  |  |  |  |

| 0Bh      | SPITXB    | TMR2      | PW0DCL            | RFCDL      |  |  |  |  |  |

| 0Ch      | SPISTAT   | PR2       | PW0DCH            | RFCDH      |  |  |  |  |  |

| 0Dh      | SPICON    | TMR3      | PW1DCL            | CMPDX      |  |  |  |  |  |

| 0Eh      | TMR1      | PR3       | PW1DCH            | CMPDY      |  |  |  |  |  |

| 0Fh      | PR1       |           |                   | CMPSTAT    |  |  |  |  |  |

| 10h      | General   |           |                   |            |  |  |  |  |  |

| 1011     | Purpose   | Memory    | back to address i | n Bank 0   |  |  |  |  |  |

| 1Fh      | Registers | Wichiory  | back to address i | II Balik 0 |  |  |  |  |  |

| 11 11    | registers |           |                   |            |  |  |  |  |  |

| 20h      | General   | General   | General           | General    |  |  |  |  |  |

|          | Purpose   | Purpose   | Purpose           | Purpose    |  |  |  |  |  |

| 3Eh      | Registers | Registers | Registers         | Registers  |  |  |  |  |  |

| 3Fh      | INTFLAG   | Memory    | back to address i | n Bank 0   |  |  |  |  |  |

| N/A | OPTION |

|-----|--------|

| 05h | IOSTA |

|-----|-------|

| 06h | IOSTB |

| 07h | IOSTC |

| 08h | IOSTD |

| 09h | IOSTE |

| 0Ch | T1CON |

|-----|-------|

| 0Dh | PHCON |

| 0Eh | PCON  |

| 0Fh | INTEN |

|     |       |

TABLE 1.2: The Registers Controlled by OPTION/OPTIONR or IOST/IOSTR Instructions

| IADLL 1.2. | TABLE 1.2. The Registers Controlled by OF Holly OF Holly of 1031/1031 k instructions |         |                             |      |              |             |         |       |      |  |  |

|------------|--------------------------------------------------------------------------------------|---------|-----------------------------|------|--------------|-------------|---------|-------|------|--|--|

| Address    | Name                                                                                 | B7      | В6                          | B5   | B4           | В3          | B2      | B1    | B0   |  |  |

| Unbanked   | Jnbanked                                                                             |         |                             |      |              |             |         |       |      |  |  |

| N/A (r/w)  | OPTION                                                                               | /PHBCE  | GIE                         |      |              | PSA         | PS2     | PS1   | PS0  |  |  |

| 05h (r/w)  | IOSTA                                                                                |         |                             | Po   | ort A I/O Co | ntrol Regis | ster    |       |      |  |  |

| 06h (r/w)  | IOSTB                                                                                |         | Port B I/O Control Register |      |              |             |         |       |      |  |  |

| 07h (r/w)  | IOSTC                                                                                |         | Port C I/O Control Register |      |              |             |         |       |      |  |  |

| 08h (r/w)  | IOSTD                                                                                |         |                             | Po   | rt D I/O Co  | ntrol Regis | ster    |       |      |  |  |

| 09h (r/w)  | IOSTE                                                                                |         |                             | Po   | rt E I/O Co  | ntrol Regis | ster    |       |      |  |  |

| 0Ch (r/w)  | T1CON                                                                                |         |                             |      |              |             | T10N    | T1P1  | T1P0 |  |  |

| 0Dh (r/w)  | PHCON                                                                                | HDC     |                             |      |              | /PHE        | /PHD    | /PHB  | /PHA |  |  |

| 0Eh (r/w)  | PCON                                                                                 | LVDTE   | ODE                         | WDTE | -            | ROC         | -       | -     | /WUE |  |  |

| 0Fh (r/w)  | INTEN                                                                                | SPITXIE | RFCIE                       | T3IE | T2IE         | T1IE        | SPIRCIE | INTIE | T0IE |  |  |

Legend: - = unimplemented, read as '0', \* = unimplemented, read as '1'.

**TABLE 1.3: Operational Registers Map**

| TABLE 1.3: | Operational I | Registers I | Мар         |           |              |              |              |              |       |

|------------|---------------|-------------|-------------|-----------|--------------|--------------|--------------|--------------|-------|

| Address    | Name          | B7          | В6          | B5        | B4           | В3           | B2           | B1           | B0    |

| Unbanked   |               |             |             |           |              |              |              |              |       |

| 00h (r/w)  | INDF          | Us          | es contents | of FSR to | address da   | ata memory   | / (not a phy | /sical regis | ter)  |

| 01h (r/w)  | TMR0          |             |             | 8-b       | it real-time | clock/cour   | iter         |              |       |

| 02h (r/w)  | PCL           |             |             |           | Low order    | 8 bits of PC | ;            |              |       |

| 03h (r/w)  | STATUS        | GP          | PG1         | PG0       | TO           | PD           | Z            | DC           | С     |

| 04h (r/w)  | FSR           | RP1         | RP0         |           | Indirect     | data memo    | ory address  | pointer      |       |

| 05h (r/w)  | PORTA         | IOA7        | IOA6        | IOA5      | IOA4         | IOA3         | IOA2         | IOA1         | IOA0  |

| 06h (r/w)  | PORTB         | IOB7        | IOB6        | IOB5      | IOB4         | IOB3         | IOB2         | IOB1         | IOB0  |

| 07h (r/w)  | PORTC         | IOC7        | IOC6        | IOC5      | IOC4         | IOC3         | IOC2         | IOC1         | IOC0  |

| 08h (r/w)  | PORTD         | IOD7        | IOD6        | IOD5      | IOD4         | IOD3         | IOD2         | IOD1         | IOD0  |

| 09h (r/w)  | PORTE         | IOE7        | IOE6        | IOE5      | IOE4         | IOE3         | IOE2         | IOE1         | IOE0  |

| Bank 0     |               |             |             |           |              |              |              |              |       |

| 0Ah (r/w)  | SPIRCB        | RC7         | RC6         | RC5       | RC4          | RC3          | RC2          | RC1          | RC0   |

| 0Bh (r/w)  | SPITXB        | TX7         | TX6         | TX5       | TX4          | TX3          | TX2          | TX1          | TX0   |

| 0Ch (r/w)  | SPISTAT       |             | TXBFIF      | TXBF      | TM1IF        | SDOOD        | SCKOD        | RCBFIF       | RCBF  |

| 0Dh (r/w)  | SPICON        | CKEDG       | SPION       | RCOV      | SSE          | SSEMOD       | SPIM2        | SPIM1        | SPIM0 |

| 0Eh (r/w)  | TMR1          | TMR17       | TMR16       | TMR15     | TMR14        | TMR13        | TMR12        | TMR11        | TMR10 |

| 0Fh (r/w)  | PR1           | PR17        | PR16        | PR15      | PR14         | PR13         | PR12         | PR11         | PR10  |

| Bank 1     |               | •           |             |           |              | •            |              | •            |       |

| 0Ah (r/w)  | T23CON        | -           | -           | -         | T16          | T3ON         | T3CS         | T2ON         | T2CS  |

| 0Bh (r/w)  | TMR2          | TMR27       | TMR26       | TMR25     | TMR24        | TMR23        | TMR22        | TMR21        | TMR20 |

| 0Ch (r/w)  | PR2           | PR27        | PR26        | PR25      | PR24         | PR23         | PR22         | PR21         | PR20  |

| 0Dh (r/w)  | TMR3          | TMR37       | TMR36       | TMR35     | TMR34        | TMR33        | TMR32        | TMR31        | TMR30 |

| 0Eh (r/w)  | PR3           | PR37        | PR36        | PR35      | PR34         | PR33         | PR32         | PR31         | PR30  |

| 0Fh        | -             |             |             | Uni       | mplemente    | d, read as   | "0"s         | •            |       |

| Bank 2     |               | •           |             |           | -            |              |              |              |       |

| 0Ah (r/w)  | PWMCON        | -           | -           | -         | -            | -            | PW1T3        | PW10N        | PW00N |

| 0Bh (r/w)  | PW0DCL        | DC1         | DC0         | -         | -            | -            | -            | -            | -     |

| 0Ch (r/w)  | PW0DCH        | DC9         | DC8         | DC7       | DC6          | DC5          | DC4          | DC3          | DC2   |

| 0Dh (r/w)  | PW1DCL        | DC1         | DC0         | -         | -            | -            | -            | -            | -     |

| 0Eh (r/w)  | PW1DCH        | DC9         | DC8         | DC7       | DC6          | DC5          | DC4          | DC3          | DC2   |

| 0Fh        | -             |             |             | Uni       | mplemente    | d, read as   | "0"s         | •            |       |

| Bank 3     | •             | •           |             |           | -            |              |              |              |       |

| 0Ah (r/w)  | RFCCON        | RFCON       | START       | -         | RFCS4        | RFCS3        | RFCS2        | RFCS1        | RFCS0 |

| 0Bh (r)    | RFCDL         | RFCD7       | RFCD6       | RFCD5     | RFCD4        | RFCD3        | RFCD2        | RFCD1        | RFCD0 |

| 0Ch (r)    | RFCDH         | RFCOV       | RFCD14      | RFCD13    | RFCD12       | RFCD11       | RFCD10       | RFCD9        | RFCD8 |

| 0Dh (r/w)  | CMPDX         | DX7         | DX6         | DX5       | DX4          | DX3          | DX2          | DX1          | DX0   |

| 0Eh (r/w)  | CMPDY         | DY7         | DY6         | DY5       | DY4          | DY3          | DY2          | DY1          | DY0   |

| 0Fh (r)    | CMPSTAT       | -           | -           | -         | -            | CMPF3        | CMPF2        | CMPF1        | CMPF0 |

| Unbanked   |               |             |             |           |              |              |              |              |       |

| 3Fh (r/w)  | INTFLAG       | SPITXIF     | RFCIF       | T3IF      | T2IF         | T1IF         | SPIRCIF      | INTIF        | TOIF  |

| J (17 W)   |               | J. 117(11   |             | . 511     |              |              | J (OII       |              | . 511 |

Legend: - = unimplemented, read as '0', \* = unimplemented, read as '1'.

# 2.0 FUNCTIONAL DESCRIPTIONS

#### 2.1 Operational Registers

## 2.1.1 INDF (Indirect Addressing Register)

| Address   | Name | B7 | В6          | B5        | B4         | В3         | B2           | B1            | В0   |

|-----------|------|----|-------------|-----------|------------|------------|--------------|---------------|------|

| 00h (r/w) | INDF | Us | es contents | of FSR to | address da | ata memory | / (not a phy | /sical regist | ter) |

The INDF Register is not a physical register. Any instruction accessing the INDF register can actually access the register pointed by FSR Register. Reading the INDF register itself indirectly (FSR="0") will read 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected).

The bits 5-0 of FSR register are used to select up to 64 registers (address: 00h ~ 3Fh).

In FM8PE51 series, the data memory is partitioned into four banks. Switching between these banks requires the RP1 and RP0 bits in the FSR register to be configured for the desired bank. The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers. All Special Function Registers and some of General Purpose Registers from other banks are mirrored in bank 0 for code reduction and quicker access.

| Accessed<br>Bank | RP1:RP0 |

|------------------|---------|

| 0                | 0 0     |

| 1                | 0 1     |

| 2                | 1 0     |

| 3                | 1 1     |

#### **EXAMPLE 2.1: INDIRECT ADDRESSING**

- Register file 38 contains the value 10h

- Register file 39 contains the value 0Ah

- · Load the value 38 into the FSR Register

- A read of the INDF Register will return the value of 10h

- Increment the value of the FSR Register by one (@FSR=39h)

- A read of the INDR register now will return the value of 0Ah.

FIGURE 2.1: Direct/Indirect Addressing for FM8PE51 Series

## 2.1.2 TMR0 (Time Clock/Counter register)

| Address   | Name | B7 | B6 | B5  | B4           | В3         | B2   | B1 | В0 |

|-----------|------|----|----|-----|--------------|------------|------|----|----|

| 01h (r/w) | TMR0 |    |    | 8-b | it real-time | clock/cour | nter |    |    |

The Timer0 is a 8-bit timer/counter. The clock source of Timer0 can come from the instruction cycle clock. The prescaler is assigned to Timer0 by clearing the PSA bit (OPTION<3>). In this case, the prescaler will be cleared when TMR0 register is written with a value.

## 2.1.3 PCL (Low Bytes of Program Counter) & Stack

| Address   | Name | B7 | B6 | B5 | B4          | В3           | B2 | B1 | В0 |

|-----------|------|----|----|----|-------------|--------------|----|----|----|

| 02h (r/w) | PCL  |    |    |    | Low order 8 | B bits of PC | ;  |    |    |

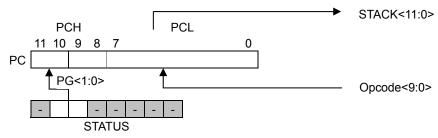

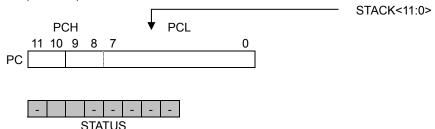

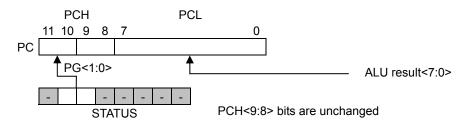

FM8PE51 devices have a 12-bit wide Program Counter (PC) and five-level deep 12-bit hardware push/pop stack. The low byte of PC is called the PCL register. This register is readable and writable. The high byte of PC is called the PCH register. This register contains the PC<11:8> bits and is not directly readable or writable. All updates to the PCH register go through the PG<1:0> bits (STATUS<6:5>). As a program instruction is executed, the Program Counter will contain the address of the next program instruction to be executed. The PC value is increased by one, every instruction cycle, unless an instruction changes the PC.

For a GOTO instruction, the PC<9:0> is provided by the GOTO instruction word. The PC<11:10> is updated from the PG<1:0> bits (STATUS<6:5>). The PCL register is mapped to PC<7:0>.

For a CALL instruction, the PC<9:0> is provided by the CALL instruction word. The PC<11:10> is updated from the PG<1:0> bits (STATUS<6:5>). The next PC will be loaded (PUSHed) onto the top of STACK. The PCL register is mapped to PC<7:0>.

For a RETIA, RETFIE, or RETURN instruction, the PC are updated (POPed) from the top of STACK. The PCL register is mapped to PC<7:0>.

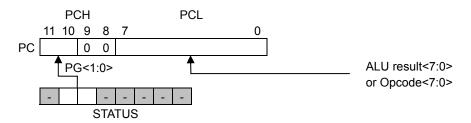

For any instruction where the PCL is the destination (excluding TBL instruction), the PC<7:0> is provided by the instruction word or ALU result, and the PC<9:8> will be cleared. The PC<11:10> will come from the PG<1:0> bits (STATUS<6:5>).

For TBL instruction, the PC<7:0> is provided by the ALU result, and the PC<9:8> are not changed. The PC<11:10> will come from the PG<1:0> bits (STATUS<6:5>).

# FIGURE 2.2: Loading of PC in Different Situations

#### Situation 1: GOTO Instruction

# Situation 2: CALL Instruction

Situation 3: RETIA, RETFIE, or RETURN Instruction

Situation 4: Instruction with PCL as destination (excluding TBL instruction)

Situation 5: TBL Instruction

# 2.1.4 STATUS (Status Register)

| Address   | Name   | В7 | В6  | B5  | B4 | В3 | B2 | B1 | B0 |

|-----------|--------|----|-----|-----|----|----|----|----|----|

| 03h (r/w) | STATUS | GP | PG1 | PG0 | TO | PD | Z  | DC | С  |

This register contains the arithmetic status of the ALU, the RESET status.

If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the <u>write</u> to <u>these</u> three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended. For example, CLRR STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as 000u u1uu (where u = unchanged).

#### C: Carry/borrow bit.

ADDAR, ADDIA

- = 1, a carry occurred.

- = 0, a carry did not occur.

SUBAR, SUBIA

- = 1, a borrow did not occur.

- = 0, a borrow occurred.

Note: A subtraction is executed by adding the two's complement of the second operand. For rotate (RRR, RLR) instructions, this bit is loaded with either the high or low order bit of the source register.

DC: Half carry/half borrow bit.

ADDAR, ADDIA

- = 1, a carry from the 4th low order bit of the result occurred.

- = 0, a carry from the 4th low order bit of the result did not occur.

SUBAR, SUBIA

- = 1, a borrow from the 4th low order bit of the result did not occur.

- = 0, a borrow from the 4th low order bit of the result occurred.

#### Z: Zero bit.

- = 1, the result of a logic operation is zero.

- = 0, the result of a logic operation is not zero.

**PD**: Power down flag bit.

- = 1, after power-up or by the CLRWDT instruction.

- = 0, by the SLEEP instruction.

**TO**: Time overflow flag bit.

- = 1, after power-up or by the CLRWDT or SLEEP instruction.

- = 0, a watch-dog time overflow occurred.

**PG1:PG0** : Program memory page select bits. Used for GOTO, CALL, or any instruction with PCL as destination.

| PG1 | PG0 | Program Memory Page [Address] |

|-----|-----|-------------------------------|

| 0   | 0   | Page 0 [000h~3FFh]            |

| 0   | 1   | Page 1 [400h~7FFh]            |

| 1   | 0   | Page 2 [800h~BFFh]            |

| 1   | 1   | Page 3 [C00h~FFFh]            |

GP: General purpose read/write bit.

# 2.1.5 FSR (Indirect Data Memory Address Pointer)

| Address   | Name | В7  | В6  | B5                                   | B4 | В3 | B2 | B1 | В0 |

|-----------|------|-----|-----|--------------------------------------|----|----|----|----|----|

| 04h (r/w) | FSR  | RP1 | RP0 | Indirect data memory address pointer |    |    |    |    |    |

Bit5:Bit0: Select registers address in the indirect addressing mode. See 2.1.1 for detail description.

RP1:RP0: These bits are used to switching the bank of four data memory banks. See 2.1.1 for detail description.

## 2.1.6 PORTA, PORTB, PORTC, PORTD & PORTE (Port Data Registers)

| Address   | Name  | B7   | В6   | B5   | B4   | В3   | B2   | B1   | В0   |

|-----------|-------|------|------|------|------|------|------|------|------|

| 05h (r/w) | PORTA | IOA7 | IOA6 | IOA5 | IOA4 | IOA3 | IOA2 | IOA1 | IOA0 |

| 06h (r/w) | PORTB | IOB7 | IOB6 | IOB5 | IOB4 | IOB3 | IOB2 | IOB1 | IOB0 |

| 07h (r/w) | PORTC | IOC7 | IOC6 | IOC5 | IOC4 | IOC3 | IOC2 | IOC1 | IOC0 |

| 08h (r/w) | PORTD | IOD7 | IOD6 | IOD5 | IOD4 | IOD3 | IOD2 | IOD1 | IOD0 |

| 09h (r/w) | PORTE | IOE7 | IOE6 | IOE5 | IOE4 | IOE3 | IOE2 | IOE1 | IOE0 |

Reading the port (PORTA, PORTB, PORTC, PORTD, PORTE register) reads the status of the pins independent of the pin's input/output modes. Writing to these ports will write to the port data latch.

# 2.1.7 SPIRCB (SPI Receive Buffer Register) (Bank 0)

| Address   | Name   | В7  | В6  | B5  | B4  | В3  | B2  | B1  | В0  |

|-----------|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0Ah (r/w) | SPIRCB | RC7 | RC6 | RC5 | RC4 | RC3 | RC2 | RC1 | RC0 |

RC7:RC0: SPI receives data buffer. Once the 8-bits data have been received, the data in SPI shift register (SPISR) will be moved to the SPIRCB register.

The data must be read out before the next 8-bits data reception is completed if needed.

The RCBF flag is set when the data in SPISR is moved to the SPIRCB register, and cleared as the SPIRCB register reads.

# 2.1.8 SPITXB (SPI Transmit Buffer Register) (Bank 0)

| Address   | Name   | В7  | B6  | B5  | B4  | В3  | B2  | B1  | В0  |

|-----------|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0Bh (r/w) | SPITXB | TX7 | TX6 | TX5 | TX4 | TX3 | TX2 | TX1 | TX0 |

**TX7:TX0**: SPI transmits data buffer. Once the first valid clock pulse appear on SCK pin, the data in SPITXB will be loaded into SPISR and start to shift in/out.

The new data must be written to SPITXB before the 8-bits data transmission is completed if needed.

The TXBF flag is set when the data in SPITXB is moved to the SPISR register, and cleared as the SPITXB register writes.

## 2.1.9 SPISTAT (SPI Status Register) (Bank 0)

| Address   | Name    | В7 | B6     | B5   | B4    | В3    | B2    | B1     | В0   |

|-----------|---------|----|--------|------|-------|-------|-------|--------|------|

| 0Ch (r/w) | SPISTAT | -  | TXBFIF | TXBF | TM1IF | SDOOD | SCKOD | RCBFIF | RCBF |

**RCBF**: SPI receive buffer full flag. Set when the data in SPISR is moved to the SPIRCB register, reset by software or by reading SPIRCB register.

- = 1, Receive complete, SPIRCB is full.

- = 0, Receive not complete, SPIRCB is empty.

**RCBFIF**: SPI receive buffer full interrupt flag. Set when the data in SPISR is moved to the SPIRCB register, reset by software.

- = 1, Receive complete, SPIRCB is full.

- = 0, Receive not complete, SPIRCB is empty.

SCKOD: Open-drain control bit for SCK pin output

- = 1, Open-drain enable.

- = 0, Open-drain disable.

**SDOOD**: Open-drain control bit for SDO pin output

- = 1, Open-drain enable.

- = 0, Open-drain disable.

TM1IF: SPI receive complete interrupt flag in Timer 1 mode. Set when receiving complete, reset by software.

- = 1, In Timer 1 mode, receiving complete.

- = 0, In Timer 1 mode, receiving not complete yet.

**TXBF**: SPI transmit buffer empty flag. Set when the data in SPITXB is moved to the SPISR register, reset by software or by writing SPITXB register.

- = 1, Transmit start, SPITXB is empty.

- = 0, SPITXB is full.

**TXBFIF**: SPI transmit buffer empty interrupt flag. Set when the data in SPITXB is moved to the SPISR register, reset by software.

- = 1, Transmit start, SPITXB is empty.

- = 0, SPITXB is full.

## 2.1.10 SPICON (SPI Control Register) (Bank 0)

| Address   | Name   | В7    | В6    | B5   | B4  | B3     | B2    | B1    | В0    |

|-----------|--------|-------|-------|------|-----|--------|-------|-------|-------|

| 0Dh (r/w) | SPICON | CKEDG | SPION | RCOV | SSE | SSEMOD | SPIM2 | SPIM1 | SPIM0 |

SPIM2:SPIM0 : SPI mode setting

| SPIM2 : SPIM0 | SSP Mode                                                  |

|---------------|-----------------------------------------------------------|

| 0, 0, 0       | SPI master mode, clock = Fosc/2                           |

| 0, 0, 1       | SPI master mode, clock = Fosc/4                           |

| 0, 1, 0       | SPI master mode, clock = Fosc/8                           |

| 0, 1, 1       | SPI master mode, clock = Fosc/16                          |

| 1, 0, 0       | SPI master mode, clock = Fosc/32                          |

| 1, 0, 1       | SPI slave mode, clock = SCK pin, SSB pin control enabled  |

| 1, 1, 0       | SPI slave mode, clock = SCK pin, SSB pin control disabled |

| 1, 1, 1       | SPI master mode, clock = Timer1 output/2                  |

**SSEMOD**: SSE bit control enable bit

- = 1, Disable the SSE bit control. It means the SCK input/output directly.

- = 0, Enable the SSE bit control. It means the SCK input/output will be inhibited if SSE = 0.

**SSE**: SPI shift register enable bit

- = 1, Start to transmit/receive, and keep on "1" while the current byte is still being transmitted/received.

- = 0, Reset by hardware as soon as the shifting is complete.

Note: this bit is a "don't care" if SSEMOD = 1.

**RCOV**: SPI receive buffer overflow bit (only in slave mode)

# FM8PE51

- = 1, A new byte is received while the SPIRCB register is still holding the previous data. In this case, the data in SPISR register will be ignored and lost.

- = 0, Not overflow.

SPION: SPI module enable bit

- = 1, Enable SPI module.

- = 0, Disable SPI module.

**CKEDG**: Clock edge select bit

- = 1, Data shifts out on falling edge of SCK, and shifts in on rising edge of SCK.

- = 0, Data shifts in on rising edge of SCK, and shifts in on falling edge of SCK.

#### 2.1.11 TMR1 (Timer 1 Register) (Bank 0)

| Address   | Name | В7    | В6    | B5    | B4    | В3    | B2    | B1    | В0    |

|-----------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0Eh (r/w) | TMR1 | TMR17 | TMR16 | TMR15 | TMR14 | TMR13 | TMR12 | TMR11 | TMR10 |

TMR17:TMR10: Timer 1 register and increase until the value matches to PR1 register, and then reset to "0".

## 2.1.12 PR1 (Timer 1 Pulse-width Register) (Bank 0)

| Address   | Name | В7   | В6   | B5   | B4   | В3   | B2   | B1   | В0   |

|-----------|------|------|------|------|------|------|------|------|------|

| 0Fh (r/w) | PR1  | PR17 | PR16 | PR15 | PR14 | PR13 | PR12 | PR11 | PR10 |

PR17:PR10 : Timer 1 period register.

## 2.1.13 T23CON (Timer 2&3 Control Register) (Bank 1)

| Address   | Name   | B7 | В6 | B5 | B4  | В3   | B2   | B1   | В0   |

|-----------|--------|----|----|----|-----|------|------|------|------|

| 0Ah (r/w) | T23CON | -  | -  | -  | T16 | T3ON | T3CS | T2ON | T2CS |

T2CS: Timer 2 clock source selection bit

- = 1, External clock input T23CKI pin.

- = 0, Internal clock Fosc/4.

T20N: Timer 2 module enable bit

- = 1. Enable Timer 2 module.

- = 0, Disable Timer 2 module.

T3CS: Timer 3 clock source selection bit

- = 1, External clock input T23CKI pin.

- = 0, Internal clock Fosc/4.

T3ON: Timer 3 module enable bit

- = 1, Enable Timer 3 module.

- = 0, Disable Timer 3 module.

T16: 8-bit or 16-bit timer selection bit for Timer2 & Timer3

- = 1, Timer2 & Timer3 are concatenated to form a 16-bit timer.

- = 0, Timer2 & Timer3 are two 8-bit incrementing timers.

Bit7:BIT5: Not used. Read as "0"s

## 2.1.14 TMR2 (Timer 2 Register) (Bank 1)

| Address   | Name | B7    | В6    | B5    | B4    | В3    | B2    | B1    | В0    |

|-----------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0Bh (r/w) | TMR2 | TMR27 | TMR26 | TMR25 | TMR24 | TMR23 | TMR22 | TMR21 | TMR20 |

TMR27:TMR20: Timer 2 register and increase until the value matches to PR2 register, and then reset to "0".

# 2.1.15 PR2 (Timer 2 Pulse-width Register) (Bank 1)

| Address   | Name | В7   | В6   | B5   | B4   | В3   | B2   | B1   | В0   |

|-----------|------|------|------|------|------|------|------|------|------|

| 0Ch (r/w) | PR2  | PR27 | PR26 | PR25 | PR24 | PR23 | PR22 | PR21 | PR20 |

PR27:PR20 : Timer 2 period register.

#### 2.1.16 TMR3 (Timer 3 Register) (Bank 1)

| Address   | Name | B7    | B6    | B5    | B4    | В3    | B2    | B1    | В0    |

|-----------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0Dh (r/w) | TMR3 | TMR37 | TMR36 | TMR35 | TMR34 | TMR33 | TMR32 | TMR31 | TMR30 |

TMR37:TMR30: Timer 3 register and increase until the value matches to PR3 register, and then reset to "0".

## 2.1.17 PR3 (Timer 3 Pulse-width Register) (Bank 1)

| Address   | Name | В7   | В6   | B5   | B4   | В3   | B2   | B1   | B0   |

|-----------|------|------|------|------|------|------|------|------|------|

| 0Eh (r/w) | PR3  | PR37 | PR36 | PR35 | PR34 | PR33 | PR32 | PR31 | PR30 |

PR37:PR30 : Timer 3 period register.

#### 2.1.18 PWMCON (PWM Control Register) (Bank 2)

| Address   | Name   | B7 | В6 | B5 | B4 | В3 | B2    | B1    | В0    |

|-----------|--------|----|----|----|----|----|-------|-------|-------|

| 0Ah (r/w) | PWMCON | -  | -  | -  | -  | -  | PW1T3 | PW10N | PW00N |

PW00N: PWM0 module enable bit

= 1, Enable PWM0 output, IOA0/PWM0 pin is configured to PWM0 pin.

= 0, Disable PWM0 output, IOA0/PWM0 pin is configured to IOA0 pin.

**PW10N**: PWM1 module enable bit

= 1, Enable PWM1 output, IOC0/PWM1 pin is configured to PWM1 pin.

= 0, Disable PWM1 output, IOC0/PWM1 pin is configured to IOC0 pin.

PW1T3: PWM1 time base selection bit

= 1, the PWM1 time base is determined by TMR3 and PR3.

= 0, the PWM1 time base is determined by TMR2 and PR2.

Bit7:bit3: Not used. Read as "0"s.

#### 2.1.19 PW0DCL (PWM0 Duty Cycle Register Low Byte) (Bank 2)

| Address   | Name   | B7  | В6  | B5 | B4 | В3 | B2 | B1 | В0 |

|-----------|--------|-----|-----|----|----|----|----|----|----|

| 0Bh (r/w) | PW0DCL | DC1 | DC0 | -  | -  | -  | -  | -  | -  |

Bit5:bit0: Not used. Read as "0"s.

DC1:DC0: The low bits of PWM0 duty cycle.

#### 2.1.20 PW0DCH (PWM0 Duty Cycle Register High Byte) (Bank 2)

| Address   | Name   | В7  | B6  | B5  | B4  | В3  | B2  | B1  | В0  |

|-----------|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0Ch (r/w) | PW0DCH | DC9 | DC8 | DC7 | DC6 | DC5 | DC4 | DC3 | DC2 |

**DC9:DC2**: The high byte of PWM0 duty cycle.

# 2.1.21 PW1DCL (PWM1 Duty Cycle Register Low Byte) (Bank 2)

| Address   | Name   | B7  | В6  | B5 | B4 | В3 | B2 | B1 | В0 |

|-----------|--------|-----|-----|----|----|----|----|----|----|

| 0Dh (r/w) | PW1DCL | DC1 | DC0 | -  | -  | -  | -  | -  | -  |

Bit5:bit0: Not used. Read as "0"s.

**DC1:DC0**: The low bits of PWM1 duty cycle.

#### 2.1.22 PW1DCH (PWM1 Duty Cycle Register High Byte) (Bank 2)

| Address   | Name   | В7  | B6  | B5  | B4  | В3  | B2  | B1  | B0  |

|-----------|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0Eh (r/w) | PW1DCH | DC9 | DC8 | DC7 | DC6 | DC5 | DC4 | DC3 | DC2 |

**DC9:DC2**: The high byte of PWM1 duty cycle.

#### 2.1.23 RFCCON (RFC Control Register) (Bank 3)

| Address   | Name   | В7    | B6    | B5 | B4    | В3    | B2    | B1    | B0    |

|-----------|--------|-------|-------|----|-------|-------|-------|-------|-------|

| 0Ah (r/w) | RFCCON | RFCON | START | -  | RFCS4 | RFCS3 | RFCS2 | RFCS1 | RFCS0 |

RFCS4:RFCS0: Select one the RFC oscillation network of RFCx (x = 0 to 18). The selected IOxx/RFCx pin will be configured as RFCx output pin if RFCON = 1. Other IOxx/RFCx pins will still behave as port pins. If RFCON = 0, all IOxx/RFCx pins will still behave as port pins.

= 0,0,0,0,0, IOA2/RFC0 pin is configured to RFC0 pin.

= 0,0,0,0,1, IOA3/RFC1 pin is configured to RFC1 pin.

= 0,0,0,1,0, IOA4/RFC2 pin is configured to RFC2 pin.

= 0,0,0,1,1, IOA5/RFC3 pin is configured to RFC3 pin.

= 0,0,1,0,0, IOA6/RFC4 pin is configured to RFC4 pin.

= 0,0,1,0,1, IOA7/RFC5 pin is configured to RFC5 pin.

= 0,0,1,1,0, IOD0/RFC6 pin is configured to RFC6 pin.

= 0,0,1,1,1, IOD1/RFC7 pin is configured to RFC7 pin.

= 0,1,0,0,0, IOB1/RFC8 pin is configured to RFC8 pin.

= 0,1,0,0,1, IOB2/RFC9 pin is configured to RFC9 pin.

= 0,1,0,1,0, IOB3/RFC10 pin is configured to RFC10 pin.

= 0,1,0,1,1, IOB4/RFC11 pin is configured to RFC11 pin.

= 0,1,1,0,0, IOB5/RFC12 pin is configured to RFC12 pin.

= 0,1,1,0,1, IOB6/RFC13 pin is configured to RFC13 pin.

= 0,1,1,1,0, IOB7/RFC14 pin is configured to RFC14 pin.

= 0,1,1,1,1, IOC2/RFC15 pin is configured to RFC15 pin.

= 1,0,0,0,0, IOC1/RFC16 pin is configured to RFC16 pin.

= 1,0,0,0,1, DATA/RFC17 pin is configured to RFC17 pin.

= 1,0,0,1,0, CLK/RFC18 pin is configured to RFC18 pin.

Bit5 : Not used. Read as "0".

START: RFC counter enable bit

= 1, RFC counter start to convert.

= 0, Stop the RFC conversion, reset by hardware when conversion is finished or by software.

RFCON: RFC module enable bit

- = 1, Enable RFC module, the selected IOxx/RFCx pin is configured to RFCx pin, and the IOA1/CX pin is configured to CX pin.

- = 0, Disable RFC module, all the IOxx/RFCx pins are configured to IOXX pin, and the IOA1/CX pin is configured to IOA1 pin.

#### 2.1.24 RFCDL (RFC Data Register Low Byte) (Bank 3)

| Address | Name  | В7    | В6    | B5    | B4    | В3    | B2    | B1    | B0    |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0Bh (r) | RFCDL | RFCD7 | RFCD6 | RFCD5 | RFCD4 | RFCD3 | RFCD2 | RFCD1 | RFCD0 |

RFCD7:RFCD0 : The low byte of RFC conversion result.

## 2.1.25 RFCDH (RFC Data Register High Byte) (Bank 3)

| ĺ | Address | Name  | В7    | В6     | B5     | B4     | В3     | B2     | B1    | В0    |

|---|---------|-------|-------|--------|--------|--------|--------|--------|-------|-------|

| I | 0Ch (r) | RFCDH | RFCOV | RFCD14 | RFCD13 | RFCD12 | RFCD11 | RFCD10 | RFCD9 | RFCD8 |

RFCD14:RFCD8: The high byte of RFC conversion result.

RFCOV: RFC counter overflow flag. Set when RFC counter overflow, reset by RFC counter reset.

= 1. Overflow.

= 0, Not overflow.

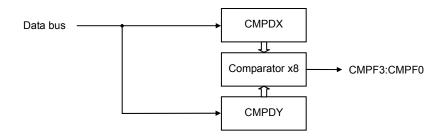

## 2.1.26 CMPDX (Data X Register Data Comparator) (Bank 3)

| Address   | Name  | В7  | В6  | B5  | B4  | В3  | B2  | B1  | В0  |

|-----------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0Dh (r/w) | CMPDX | DX7 | DX6 | DX5 | DX4 | DX3 | DX2 | DX1 | DX0 |

**DX7:DX0**: The data X of data comparator, this data will be compared to CMPDY.

#### 2.1.27 CMPDY (Data Y Register for Data Comparator) (Bank 3)

| Address   | Name  | B7  | В6  | B5  | B4  | В3  | B2  | B1  | В0  |

|-----------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0Eh (r/w) | CMPDY | DY7 | DY6 | DY5 | DY4 | DY3 | DY2 | DY1 | DY0 |

**DY7:DY0**: The data Y of data comparator, this data will be compared to CMPDX.

#### 2.1.28 CMPDY (Data Comparator Status Register) (Bank 3)

| Address | Name    | B7 | В6 | B5 | B4 | В3    | B2    | B1    | В0    |

|---------|---------|----|----|----|----|-------|-------|-------|-------|

| 0Fh (r) | CMPSTAT | -  | -  | -  | -  | CMPF3 | CMPF2 | CMPF1 | CMPF0 |

**CMPF4:CMPF0**: the error number of the compared result  $(0 \sim 8)$  of data comparator

Bit7:bit4: Not used. Read as "0"s.

#### 2.1.29 INTFLAG (Interrupt Status Register)

| Address   | Name    | B7      | В6    | B5   | B4   | В3   | B2      | B1    | В0   |

|-----------|---------|---------|-------|------|------|------|---------|-------|------|

| 3Fh (r/w) | INTFLAG | SPITXIF | RFCIF | T3IF | T2IF | T1IF | SPIRCIF | INTIF | T0IF |

**T0IF**: Timer0 overflow interrupt flag. Set when Timer0 overflows, reset by software.

**INTIF**: External INT pin interrupt flag. Set by falling edge on INT pin, reset by software.

**SPIRCIF**: SPI receive module interrupt flag. Set when SPI receiver buffer is full (SPI data transmission complete), reset by software.

T1IF: Timer1 match interrupt flag. Set when TMR1 register matches to PR1 register, reset by software.

T2IF: Timer2 match interrupt flag. Set when TMR2 register matches to PR2 register, reset by software.

**T3IF**: Timer3 match interrupt flag. Set when TMR3 register matches to PR3 register, reset by software.

RFCIF: RFC module interrupt flag. Set when RFC conversion is completed, reset by software.

**SPITXIF**: SPI transmit module interrupt flag. Set when SPI transmit buffer is empty (SPI data transmission start), reset by software.

#### 2.1.30 ACC (Accumulator)

| I | Address   | Name | B7 | В6 | B5 | B4    | В3      | B2 | B1 | B0 |

|---|-----------|------|----|----|----|-------|---------|----|----|----|

|   | N/A (r/w) | ACC  |    |    |    | Accum | nulator |    |    |    |

Accumulator is an internal data transfer, or instruction operand holding. It can not be addressed.

## 2.1.31 OPTION Register

|   | Address   | Name   | B7     | В6  | B5 | B4 | В3  | B2  | B1  | B0  |

|---|-----------|--------|--------|-----|----|----|-----|-----|-----|-----|

| ı | N/A (r/w) | OPTION | /PHBCE | GIE |    |    | PSA | PS2 | PS1 | PS0 |

Accessed by OPTION/OPTIONR instructions.

By executing the OPTION instruction, the contents of the ACC Register will be transferred to the OPTION Register. By executing the OPTIONR instruction, user can read this register into ACC.

The OPTION Register contains various control bits to configure the Timer0/WDT prescaler, Timer0, pull-high, and interrupt.

The OPTION Register are set all "1"s except GIE bit after any reset.

PS2:PS0: Prescaler rate select bits.

| PS2:PS0 | Timer0 Rate | WDT Rate |

|---------|-------------|----------|

| 0 0 0   | 1:2         | 1:1      |

| 0 0 1   | 1:4         | 1:2      |

| 0 1 0   | 1:8         | 1:4      |

| 0 1 1   | 1:16        | 1:8      |

| 1 0 0   | 1:32        | 1:16     |

| 1 0 1   | 1:64        | 1:32     |

| 1 1 0   | 1:128       | 1:64     |

| 1 1 1   | 1:256       | 1:128    |

PSA: Prescaler assign bit.

= 1, WDT (watch-dog timer).

= 0, TMR0 (Timer0).

**GIE**: Global interrupt enable bit.

- = 0, Disable all interrupts. For wake-up from SLEEP mode through an interrupt event, the device will continue execution at the instruction after the SLEEP instruction.

- = 1, Enable all un-masked interrupts. For wake-up from SLEEP mode through an interrupt event, the device will branch to the interrupt address (001h).

- Note: 1. The GIE bit is not writable bit. This bit is only set by ENI or RETFIE instructions, and cleared by DISI instruction or entering into interrupt subroutine.

- 2. When an interrupt event occur with the GIE bit and its corresponding interrupt enable bit are all set, the GIE bit will be cleared by hardware to disable any further interrupts. The RETFIE instruction will exit the interrupt routine and set the GIE bit to re-enable interrupt.

/PHBCE : = 0, Enable the internal pull-high of IOB0~ IOB7, IOC4~IOC5, and IOE0~IOE5 pins.

= 1, Disable the internal pull-high of IOB0~ IOB7, IOC4~IOC5, and IOE0~IOE5 pins.

Note: /PHB, /PHE are "AND" gating with /PHBCE, that is each one written "0" will enable pull-high.

## 2.1.32 IOSTA, IOSTB, IOSTC, IOSTD & IOSTE (Port I/O Control Registers)

| Address   | Name  | B7 | В6                          | B5 | B4 | В3 | B2 | B1 | B0 |  |

|-----------|-------|----|-----------------------------|----|----|----|----|----|----|--|

| 05h (r/w) | IOSTA |    | Port A I/O Control Register |    |    |    |    |    |    |  |

| 06h (r/w) | IOSTB |    | Port B I/O Control Register |    |    |    |    |    |    |  |

| 07h (r/w) | IOSTC |    | Port C I/O Control Register |    |    |    |    |    |    |  |

| 08h (r/w) | IOSTD |    | Port D I/O Control Register |    |    |    |    |    |    |  |

| 09h (r/w) | IOSTE |    | Port E I/O Control Register |    |    |    |    |    |    |  |

Accessed by IOST/IOSTR instructions.

The Port I/O Control Registers are loaded with the contents of the ACC Register by executing the IOSTR (05h~09h) instruction. By executing the IOSTR instruction, user can read these registers into ACC.

A '1' from a IOST Register bit puts the corresponding output driver in hi-impedance state (input mode). A '0' enables the output buffer and puts the contents of the output data latch on the selected pins (output mode).

The IOST Registers are set all "1"s (output drivers disabled) upon RESET.

# 2.1.33 T1CON (Timer 1 Control Register)

| Address   | Name  | В7 | В6 | B5 | B4 | В3 | B2   | B1   | В0   |

|-----------|-------|----|----|----|----|----|------|------|------|

| 0Ch (r/w) | T1CON |    |    |    |    |    | T10N | T1P1 | T1P0 |

Accessed by IOST/IOSTR instructions.

T1P1:T1P0 : Timer 1 prescaler bits.

| T1P1 : T1P0 | Prescaler Rate |

|-------------|----------------|

| 0, 0        | 1:1            |

| 0, 1        | 1:4            |

| 1, 0        | 1:8            |

| 1, 1        | 1 : 16         |

T10N: Timer 1 module enable bit

= 1, Enable Timer 1 module.

= 0, Disable Timer 1 module.

## 2.1.34 PHCON (Pull-high Control Register)

| Address   | Name  | В7  | В6 | B5 | B4 | В3   | B2   | B1   | В0   |

|-----------|-------|-----|----|----|----|------|------|------|------|

| 0Dh (r/w) | PHCON | HDC |    |    |    | /PHE | /PHD | /PHB | /PHA |

Accessed by IOST/IOSTR instructions.

/PHA: = 0, Enable the internal pull-high of IOA0~ IOA7 pins.

= 1, Disable the internal pull-high of IOA0~ IOA7 pins.

**/PHB**: = 0, Enable the internal pull-high of IOB0~ IOB7 pins.

= 1, Disable the internal pull-high of IOB0~ IOB7 pins.

Note: /PHB is "AND" gating with /PHBCE, that is each one written "0" will enable pull-high.

**/PHD** : = 0, Enable the internal pull-high of IOD0 $\sim$  IOD7 pins.

= 1, Disable the internal pull-high of IOD0~ IOD7 pins.

/PHE: = 0, Enable the internal pull-high of IOE0~ IOE5 pins.

= 1, Disable the internal pull-high of IOE0~ IOE5 pins.

Note: /PHE is "AND" gating with /PHBCE, that is each one written "0" will enable pull-high.

**HDC**: Driving ability enable bit of IOC0~IOC2 pins.

= 0, Normal driving ability of IOC0~IOC2 pins.

= 1, Reduce the driving ability of IOC0~IOC2 pins.

## 2.1.35 PCON (Power Control Register)

| Address   | Name | В7    | В6  | B5   | B4 | В3  | B2 | B1 | B0   |

|-----------|------|-------|-----|------|----|-----|----|----|------|

| 0Eh (r/w) | PCON | LVDTE | ODE | WDTE | -  | ROC | -  | -  | /WUE |

Accessed by IOST/IOSTR instructions.

/WUE: Input change wake-up function of IOB0~IOB7, IOC4~IOC5, and IOE0~IOE1 pins enable bit.

= 0, Enable the input change wake-up function.

= 1, Disable the input change wake-up function.

Bit2:Bit1: Not used. Read as "0"s.

**ROC**: R-option function of IOD0 and IOD1 pins enable bit.

= 0, Disable the R-option function.

= 1, Enable the R-option function. In this case, if a 430K $\Omega$  external resistor is connected/disconnected to Vss, the status of IOD0 (IOD1) is read as "0"/"1".

Bit4: Not used. Read as "1".

WDTE: WDT (watch-dog timer) enable bit.

= 0, Disable WDT.

= 1, Enable WDT.

**ODE**: Open-drain function of IOC6 and IOC7 pins enable bit.

= 0, Disable the open-drain function for both IOC6 and IOC7 pins.

= 1, Enable the open-drain function for both IOC6 and IOC7 pins.

**LVDTE**: LVDT (low voltage detector) enable bit.

= 0, Disable LVDT.= 1, Enable LVDT.

#### 2.1.36 INTEN (Interrupt Mask Register)

| Address   | Name  | B7      | В6    | B5   | B4   | В3   | B2      | B1    | В0   |

|-----------|-------|---------|-------|------|------|------|---------|-------|------|

| 0Fh (r/w) | INTEN | SPITXIE | RFCIE | T3IE | T2IE | T1IE | SPIRCIE | INTIE | T0IE |

Accessed by IOST/IOSTR instructions.

**T0IE**: Timer0 overflow interrupt enable bit.

= 0, Disable the Timer0 overflow interrupt.

= 1, Enable the Timer0 overflow interrupt.

INTIE: External INT pin interrupt enable bit.

= 0, Disable the External INT pin interrupt.

= 1, Enable the External INT pin interrupt.

SPIRCIE: SPI receive module interrupt enable bit.

= 0, Disable the SPI receive module interrupt.

= 1, Enable the SPI receive module interrupt.

T1IE: Timer1 match interrupt enable bit.

= 0, Disable the Timer1 match interrupt.

= 1, Enable the Timer1 match interrupt.

**T2IE**: Timer2 match interrupt enable bit.

= 0, Disable the Timer2 match interrupt.

= 1, Enable the Timer2 match interrupt.

T3IE: Timer3 match interrupt enable bit.

= 0, Disable the Timer3 match interrupt.

= 1, Enable the Timer3 match interrupt.

**RFCIE**: RFC module interrupt enable bit.

= 0, Disable the RFC module interrupt.

= 1, Enable the RFC module interrupt.

SPITXIE: SPI transmit module interrupt enable bit.

= 0, Disable the SPI transmit module interrupt.

= 1, Enable the SPI transmit module interrupt.

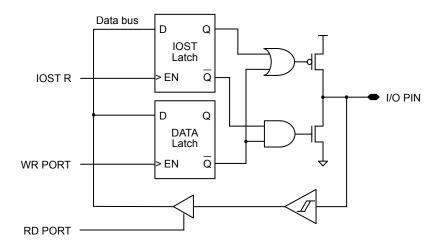

#### 2.2 I/O Ports

Port A, port B, port C, port D and port E are bi-directional tri-state I/O ports.

All I/O pins (IOA, IOB, IOC, IOD and IOE) have data direction control registers (IOSTA, IOSTB, IOSTC, IOSTD, and IOSTE) which can configure these pins as output or input.

IOA<7:0>, IOB<7:0>, IOC<5:4>, IOD<7:0> and IOE<5:0> have corresponding pull-high control bits (/PHBCE, /PHA, /PHB, /PHD, and /PHE bits) to enable the weak internal pull-high. The weak pull-high is automatically turned off when the pin is configured as an output pin.

IOC6 and IOC7 have an open-drain control bit (ODE, PCON<6>) to enable the open-drain output when these pins are configured to be an output pin.

IOD0 and IOD1 are the R-option pins enabled by setting the ROC bit (PCON<3>). When the R-option function is used, it is recommended that IOD0 and IOD1 are used as output pins, and read the status of IOD0 and IOD1 before these pins are configured to be an output pin.

IOB0~IOB7, IOC4~IOC5, and IOE0~IOE1 also provide the input change interrupt/wake-up function which are enabled by clear /WUE bit (PCON<0>). The input change interrupt/wake-up function is automatically turned off when the pin is configured as an output pin.

#### FIGURE 2.3: Block Diagram of I/O PINs

Pull-high/R-option is not shown in the figure

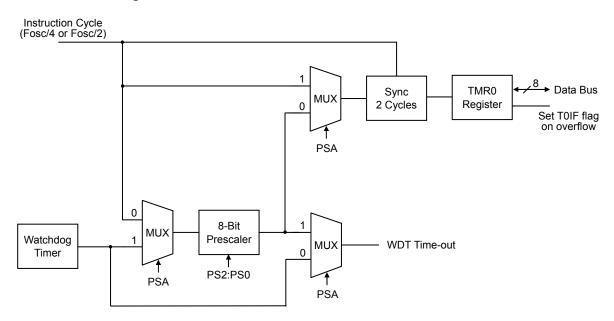

#### 2.3 Timer0/WDT & Prescler

# 2.3.1 <u>Timer0</u>

The Timer0 is a 8-bit timer/counter. The clock source of Timer0 comes from the internal clock.

The timer0 register (TMR0) will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles.

## 2.3.2 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. So the WDT will still run even if the clock on the OSCI and OSCO pins is turned off, such as in SLEEP mode. During normal operation or in SLEEP mode, a WDT time-out will cause the device reset and the TO bit (STATUS<4>) will be cleared.

The WDT can be disabled by clearing the control bit WDTE (PCON<5>) to "0".

The WDT has a nominal time-out period of 18 ms (without prescaler). If a longer time-out period is desired, a

prescaler with a division ratio of up to 1:128 can be assigned to the WDT controlled by the OPTION register. Thus, the longest time-out period is approxmately 2.3 seconds if reset delay time is set to 18ms.

The CLRWDT instruction clears the WDT and the prescaler, if assigned to the WDT, and prevents it from timing out and generating a device reset.

The SLEEP instruction resets the WDT and the prescaler, if assigned to the WDT. This gives the maximum SLEEP time before a WDT Wake-up Reset.

#### 2.3.3 Prescaler

An 8-bit counter (down counter) is available as a prescaler for the Timer0, or as a postscaler for the Watchdog Timer (WDT). Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 means that there is no prescaler for the WDT, and vice-versa. The PSA bit (OPTION<3>) determines prescaler assignment. The PS<2:0> bits (OPTION<2:0>) determine

The PSA bit (OPTION<3>) determines prescaler assignment. The PS<2:0> bits (OPTION<2:0>) determine prescaler ratio.

When the prescaler is assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler. When it is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '1's.

To avoid an unintended device reset, CLRWDT or CLRR TMR0 instructions must be executed when changing the prescaler assignment from Timer0 to the WDT, and vice-versa.

FIGURE 2.4: Block Diagram of The Timer0/WDT Prescaler

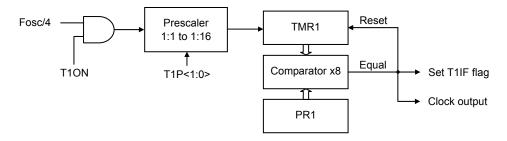

#### 2.4 Timer1

The Timer1 is a 8-bit clock counter with a programmable prescaler and a 8-bit period register (PR1). It also can be as a baud rate clock generator for the SPI module. The clock source of Timer1 comes from the internal clock (Fosc/4). The option of Timer1 prescaler (1:1, 1:4, 1:8, 1:16) is defined by T1P1:T1P0 (T1CON<1:0>) bits. The prescaler is cleared when a value is written to TMR1 or T1CON register, and during any kind of reset as well.

The timer increments from 00h until it equals the period register (PR1). It then resets to 00h at the next increment cycle. The timer interrupt flag (T1IF) is set when the timer rollover to 00h.

The timer also has a corresponding interrupt enable bit (T1IE). The timer interrupt can be enabled/disabled by setting/clearing this bit.

The timer s can be turned on and off under software control. When the timer on control bit (T1ON, T1CON<2>) is set, the timer increments from the clock source. When T1ON is cleared, the timer is turned off and cannot cause the

timer interrupt flag to be set.

**TABLE 2.1: Timer 1 Prescaler Rate**

| T1P1 : T1P0 | Prescaler Rate |

|-------------|----------------|

| 0, 0        | 1:1            |

| 0, 1        | 1:4            |

| 1, 0        | 1:8            |

| 1, 1        | 1 : 16         |

FIGURE 2.5: Block Diagram of The Timer1

#### 2.5 Timer2 & Timer3

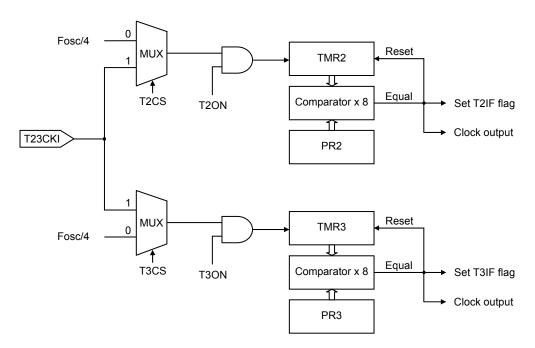

Timer2 and Timer3 are two 8-bit incrementing timers, each with an 8-bit period register (PR2 and PR3, respectively) and separate overflow interrupt flags. Timer2 and Timer3 can operate either as timers (increment on internal clock, Fosc/4), or as counters (increment on falling edge of external clock on pin IOB0/T23CKI). They are also software configurable to operate as a single 16-bit timer/counter. These timers are also used as the time base for the PWM (Pulse Width Modulation) modules.

## 2.5.1 Timer2 & Timer3 in 8-Bit Mode

Both Timer2 and Timer3 will operate in 8-bit mode when the T16 (T23CON<4>) bit is clear. These two timers can be independently configured to increment from the internal clock (Fosc/4), or from an external clock source on IOB0/T23CKI pin. The timer clock source in configured by the TxCS bit (x = 2 for Timer2 (T23CON<0>), x = 3 for Timer3 (T23CON<2>)). When TxCS is set, the clock source is the IOB0/T23CKI pin and the counters will increment on every falling edge of the IOB0/T23CKI pin.

The timer increments from 00h until it equals the period register (PRx, x = 2 for Timer2, x = 3 for Timer3). It then resets to 00h at the next increment cycle. The timer interrupt flag is set when the timer rollover to 00h. Timer2 and Timer3 have individual interrupt flag bits (T2IF and T3IF).

Each timer also has a corresponding interrupt enable bit (T2IE and T3IE). The timer interrupt can be enabled/disabled by setting/clearing this bit.

The timer s can be turned on and off under software control. When the timer on control bit (TxON, T23CON<1> and T23CON<3>) is set, the timer increments from the clock source. When TxON is cleared, the timer is turned off and cannot cause the timer interrupt flag to be set.

When TxCS is set, the clock source is the IOB0/T23CKI pin, and the counter will increment on every falling edge on the IOB0/T23CKI pin. The T23CKI input is synchronized with internal phase clocks. This cause a delay from the time a falling edge appears on T23CKI to the time TMR2 or TMR3 is actually incremented.

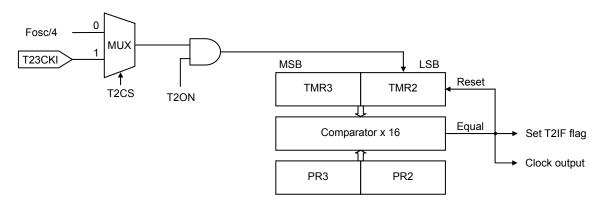

## 2.5.2 Timer2 & Timer3 in 16-bit Mode

To select 16-bit mode, set the T16 bit. In this mode, TMR2 and TMR3 are concatenated to from a 16-bit timer (TMR3:TMR2). The 16-bit timer increments until it matches the 16-bit period register (PR3:PR2). On the following timer clock, the timer value is reset to 0000h, and the T2IF bit is set.

When selecting the clock source for the 16-bit timer, the T2CS bit control the entire 16-bit timer and T3CS is a "don't

care". When T2CS is clear, the timer increments from the internal clock (Fosc/4). When T2CS is set, the timer increments on every falling edge of the IOB0/T23CKI pin.

For the 16-bit timer to increment, both T2ON and T3ON bits must be set.

**TABLE 2.2: Turning on 16-Bit Timer**

| T16 | T3ON | T2ON | Result                                |

|-----|------|------|---------------------------------------|

| 1   | 1    | 1    | 16-bit timer (TMR3:TMR2) ON           |

| 1   | 0    | 1    | 16-bit timer ON, only TMR2 increments |

| 1   | Х    | 0    | 16-bit timer OFF                      |

| 0   | 1    | 1    | Timers in 8-bit mode                  |

When T2CS is set, the 16-bit TMR3:TMR2 increments on the falling edge of clock input T23CKI. The T23CKI input is synchronized with internal phase clocks. This cause a delay from the time a falling edge appears on T23CKI to the time TMR3:TMR2 is actually incremented.

FIGURE 2.6: Timer2 and Timer3 in Two 8-bit Timer/Counter Mode

FIGURE 2.7: Timer2 and Timer3 in 16-bit Timer/Counter Mode

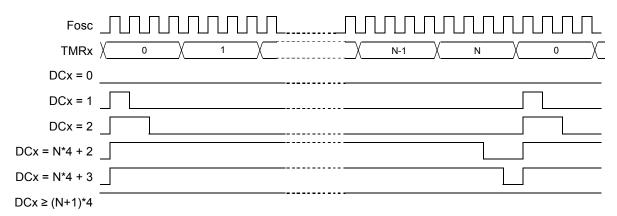

## 2.6 PWM (Pulse Width Modulation) Module

Two high speed pulse width modulation (PWM) outputs are provided. The PWM0 output uses Timer2 as its time base, the PWM1 may be configured to use Timer2 or Timer3 as the time base. The PWM outputs are on the IOA0/PWM0, and IOC0/PWM1 pins.

Each PWM output has a maximum resolution of 10-bits. The duty cycle of the output can vary from 0% to 100%. The user needs to set the PW0ON bit (PWMCON<0>) to enable the PWM output. When PW0ON bit is set, the IOA0/PWM0 pin is configured as PWM0 output and forced as an output, irrespective of the data direct bit (IOSTA<0>). When the PW0ON is clear, the pin behaves as a port pin.

Similarly, the PW1ON bit (PWMCON<1>) controls the configuration of the IOC0/PWM1 pin.

## 2.6.1 PWM Periods

The period of PWM0 output is determined by Timer2 and its period register (PR2). The period of the PWM1 output can be software configured to use either Timer2 or Timer3 as the time base. For PWM1, when PW1T3 bit (PWMCON<2>) is clear, the time base is determined by TMR2 and PR2, and when PW1T3 bit is set, the time base is determined by TMR3 and PR3.

Running two different PWM outputs on two different timers allows different periods. Running all PWMs from Timer2 allows the best use of resources by freeing Timer3 to operate as an 8-bit timer. Timer2 and Timer3 cannot be used as a 16-bit timer if any PWM is being used.

The PWM periods can be calculated as follows:

```

Period of PWM0 = [(PR2) + 1] \times 4Tosc

Period of PWM1 = [(PR2) + 1] \times 4Tosc or

[(PR3) + 1] \times 4Tosc

```

The duty cycle of PWMx is determined by the 10-bit value DCx<9:0>. The upper 8-bits are from register PWxDCH and lower2-bits are from PWxDCL<7:6> (PWxDCH:PWxDCL<7:6>).

The PWMx duty cycle is as follows:

```

PWMx Duty Cycle = (DCx) x Tosc

Where DCx represents the 10-bit value from PWxDCH:PWxDCL.

```

If DCx = 0, then the duty cycle is zero. If PRx = PWxDCH, then the PWM output will be low for one to four Tosc (depending on the state of the PWxDCL<7:6> bits). For a duty cycle to be 100%, the PWxDCH value must be greater then the PRx value.

The duty cycle registers for both PWM outputs are double buffered. When the user writes to these registers, they are stored in master latches. When TMR2 (or TMR3) overflows and a new PWM period beings, the master latch values are transferred to the slave latches.

# 2.6.2 PWM Interrupts

The PWM modules make use of the TMR2 and/or TMR3 interrupts. A timer interrupt is generated when TMR2 or TMR3 equals its period register and on the following increment is cleared to zero. This interrupt also marks the beginning of a PWM cycle. The user can write new duty cycle values before the timer rollover. The TMR2 interrupt is latched into the T2IF bit and the TMR3 interrupt is latched into the T3IF bit. These flags must be cleared in software.

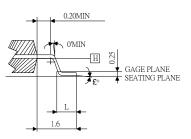

# FIGURE 2.8: The Output Waveform of PWM Driver (PRx = N)

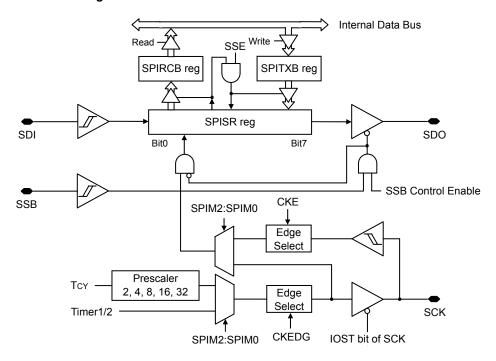

# 2.7 SPI(Serial Peripheral Interface) Module

The Serial Port Interface (SPI) Module is a serial interface useful communicating with other peripheral or microcontroller device.

The SPI mode allows 8-bit of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- 1. Serial Clock (SCK)

- 2. Serial Data In (SDI)

- 3. Serial Data Output (SDO)

Additionally a fourth pin may be used when in a slave mode of operation:

4. Slave Select (SSB)

The SPI consists of a transmit/receive shift register (SPISR), a receive buffer register (SPIRCB), and a transmit buffer register (SPITXB). The SPISR shifts the data in and out of the device, MSB first. Once the first valid clock pulse appear on SCK pin (controlled by SSE (SPICON<4>) and SSEMOD (SPICON<3>) bits), data in SPITXB will be loaded into SPISR and start to shift in/out, then transmit buffer empty detect bit TXBF (SPISTAT<5>), and interrupt flag bits SPITXIF (INTFLAG<7>) and TXBFIF (SPISTAT<6>) are set. Once the 8-bits of data have been received, the data in SPISR will be moved to the SPIRCB register, then receive buffer full detect bit RCBF (SPISTAT<0>), and interrupt flag bits SPIRCIF (INTFLAG<2>) and RCBFIF (SPISTAT<1>) are set.

If FM8PE51 is a master controller, it sends clock through the SCK pin. A couple of 8-bit data are transmitted and received at the same time. And if EM8PE51 is defined as a slave, its SCK pin could be programmed as an input pin

If FM8PE51 is a master controller, it sends clock through the SCK pin. A couple of 8-bit data are transmitted and received at the same time. And if FM8PE51 is defined as a slave, its SCK pin could be programmed as an input pin. Data will continue to be shifted based on both the clock rate and the selected edge.

When the application S/W is expecting to transmit valid data, the SPITXB should be written before the SSE bit is set (SSEMOD = 0) or the next data packet SCK pulse appears (SSEMOD = 1). Buffer empty bit TXBF indicates when SPISR has been loaded with the data of SPITXB (reception/transmission start). The TXBF bit is cleared by software or by writing SPITXB register. And the TXBF bit may be ignored if the SPI is only a receiver.

Also when the application S/W is expecting to receive valid data, the SPIRCB should be read before the next byte of data have been received completely. Buffer full bit RCBF indicates when SPIRCB has been loaded with the received data (reception/transmission is complete). The RCBF bit is cleared by software or by reading SPIRCB register. And the RCBF bit may be ignored if the SPI is only a transmitter.

Generally the SPI interrupt is used to determine when the transmission/reception has started/completed, the SPIRCB/SPITXB must be read and/or written. If the interrupt method is not going to be used, then S/W polling RCBF and/or TXBF bits is needed.

If the SPI is only going to receive, the TXBF flag could be ignored.

FIGURE 2.9: SPI Block Diagram

**TABLE 2.3: SPI Mode Setting**

| SPIM2 : SPIM0 | SPI Mode                                                  |

|---------------|-----------------------------------------------------------|

| 0,0,0         | SPI master mode, clock = Fosc/2                           |

| 0,0,1         | SPI master mode, clock = Fosc/4                           |

| 0,1,0         | SPI master mode, clock = Fosc/8                           |

| 0,1,1         | SPI master mode, clock = Fosc/16                          |

| 1,0,0         | SPI master mode, clock = Fosc/32                          |

| 1,0,1         | SPI slave mode, clock = SCK pin, SSB pin control enabled  |

| 1,1,0         | SPI slave mode, clock = SCK pin, SSB pin control disabled |

| 1,1,1         | SPI master mode, clock = Timer1 output/2                  |

# TABLE 2.4: The Description of SPI SCK Control Bit

| CKEDG | = 1, Data shifts out on falling edge of SCK, and shifts in on rising edge of SCK |

|-------|----------------------------------------------------------------------------------|

|       | = 0, Data shifts in on rising edge of SCK, and shifts in on falling edge of SCK  |

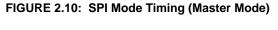

#### 2.7.1 Master Mode

#### 2.7.1.1 Master Mode with SSE Control (SSEMOD = 0)

In this master mode, the data is transmitted/received as soon as the SPI shift register enable bit SSE (SPICON<4>) bit is setting to "1" by S/W. The data in SPITXB will be loaded into SPISR at the same time and start to shift in/out, then transmit buffer empty detect bit (TXBF), and interrupt flag bits (SPITXIF, TXBFIF) are set. And then user could write the next byte data to SPITXB register before the SSE bit is set if next byte transmission is needed. The SSE bit will be kept in "1" if the communication is still undergoing. And the SSE bit will be cleared by hardware while the shifting is completed. Once the 8-bits of data have been received, the data in SPISR will be moved to the SPIRCB register, then buffer full detect bit (RCBF), interrupt flag bits (SPIRCIF, RCBFIF) are set. And then user could read out the SPIRCB register before next 8-bit data transmission is completed if needed.

How to transmit/receive data in this master mode:

- 1. Enable SPI function by setting the SPION (SPICON<6>) bit.

- 2. Decide the transmission rate and source by programming SPIM2:SPIM0 (SPICON<2:0>) bits.

- 3. Write the data that you want to transmit to SPITXB register if needed.

- 4. Set SSE (SPICON<4>) bit to start transmit.

- 5. When the 8-bit data transmission starts, both of the SPITXIF and TXBFIF interrupt flags will set to 1. Besides, both of these bits are cleared by software. The TXBF flag also will be set to "1", cleared by software or by writing data to SPITXB register.

- 6. After the 8-bit data transmission is completed, the SSE bit will be reset to "0" by hardware. Therefore, if user wants to transmit/receive another 8-bit data, write next byte data to SPITXB register and set SSE bit to "1" again.

- 7. Also after the 8-bit data transmission is completed, both of the SPIRCIF and RCBFIF interrupt flags will set to 1. Besides, both of these bits are cleared by software. The RCBF flag also will be set to "1", cleared by software or by reading out SPIRCB register.

- 8. Read out the SPIRCB register before next byte transmission being finished if needed.

## 2.7.1.2 Master Mode without SSE Control (SSEMOD = 1)

In this master mode, the data is transmitted/received as soon as write data to SPITXB register by S/W. The data in SPITXB will be loaded into SPISR at the same time and start to shift in/out, then transmit buffer empty detect bit (TXBF), and interrupt flag bits (SPITXIF, TXBFIF) are set. And then user could write the next byte data to SPITXB register if next byte transmission is needed. If the next byte data is not written into SPITXB, the communication will be stopped after the 8-bit data transmission is completed. Once the 8-bits of data have been received, the data in SPISR will be moved to the SPIRCB register, then buffer full detect bit (RCBF), interrupt flag bits (SPIRCIF, RCBFIF) are set. And then user could read out the SPIRCB register before next 8-bit data transmission is completed if needed.

How to transmit/receive data in this master mode:

- 1. Enable SPI function by setting the SPION (SPICON<6>) bit.

- 2. Decide the transmission rate and source by programming SPIM2:SPIM0 (SPICON<2:0>) bits.

- 3. Write the data that you want to transmit to SPITXB register to start transmit.

- 4. When the 8-bit data transmission starts, both of the SPITXIF and TXBFIF interrupt flags will set to 1. Besides, both of these bits are cleared by software. The TXBF flag also will be set to "1", cleared by software or by writing data to SPITXB register.

- 5. After the 8-bit data transmission is completed, if user wants to transmit/receive another 8-bit data, write next byte data to SPITXB register before this byte transmission being finished.

- 6. Also after the 8-bit data transmission is completed, both of the SPIRCIF and RCBFIF interrupt flags will set to 1. Besides, both of these bits are cleared by software. The RCBF flag also will be set to "1", cleared by software or by reading out SPIRCB register.

- 7. Read out the SPIRCB register before next byte transmission being finished if needed.

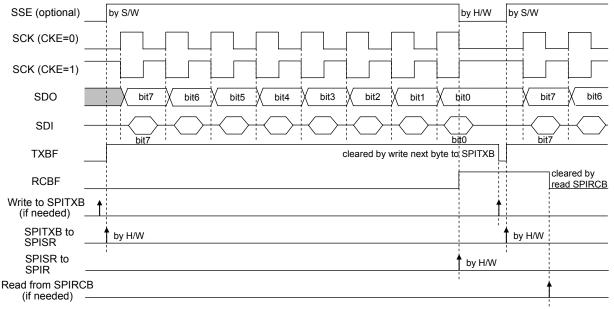

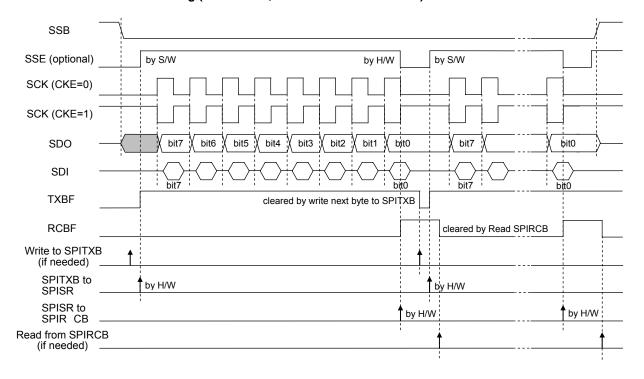

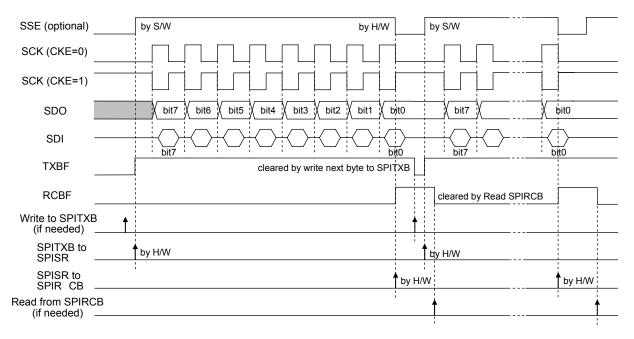

#### 2.7.2 Slave Mode

#### 2.7.2.1 Slave Mode with SSE Control (SSEMOD = 0)

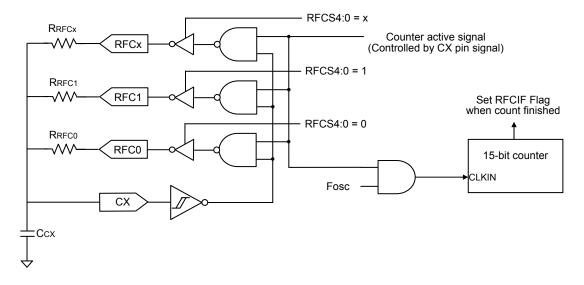

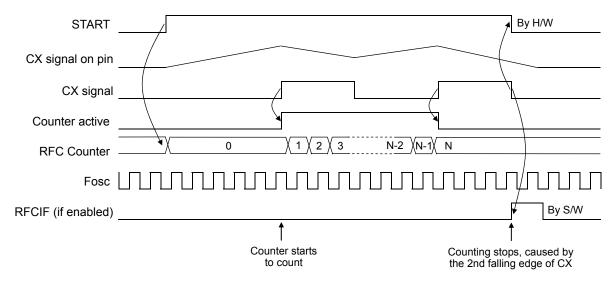

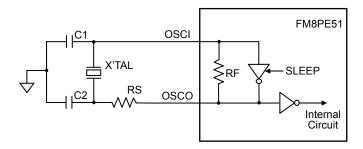

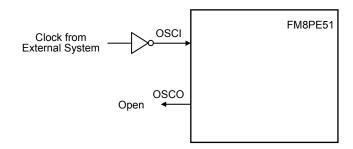

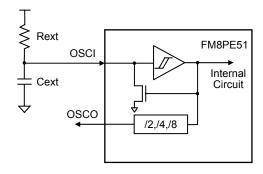

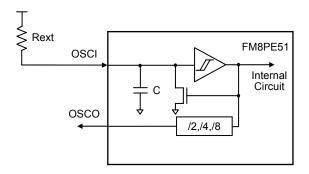

In this slave mode, the data is transmitted and received as the external clock pulses appear on SCK pin. Once the SPI shift register enable bit SSE (SPICON<4>) has been set to "1", data in SPITXB will be loaded into SPISR and start to shift in/out, then transmit buffer empty detect bit (TXBF), and interrupt flag bits (SPITXIF, TXBFIF) are set. And then user could write the next byte data to SPITXB register before the SSE bit is set if next byte transmission is needed. Once the 8-bits of data have been received, the data in SPISR will be moved to the SPIRCB register, then buffer full detect bit (RCBF), interrupt flag bits (SPIRCIF, RCBFIF) are set. And then user could read out the SPIRCB register before next 8-bit data transmission is completed if needed.